Изобретение относится к вычислительной технике и может быть использовано в составе специализированных управляющих.или универсальных цифровых вычислительных машин, а также в качестве базового элемента при разработке различного типа распределенных вычислительных структур с повышенной помехоустойчивостью.

Цель изобретения - повышение помехоустойчивости за счет обеспечения некритичности частного к единичным сбоям.

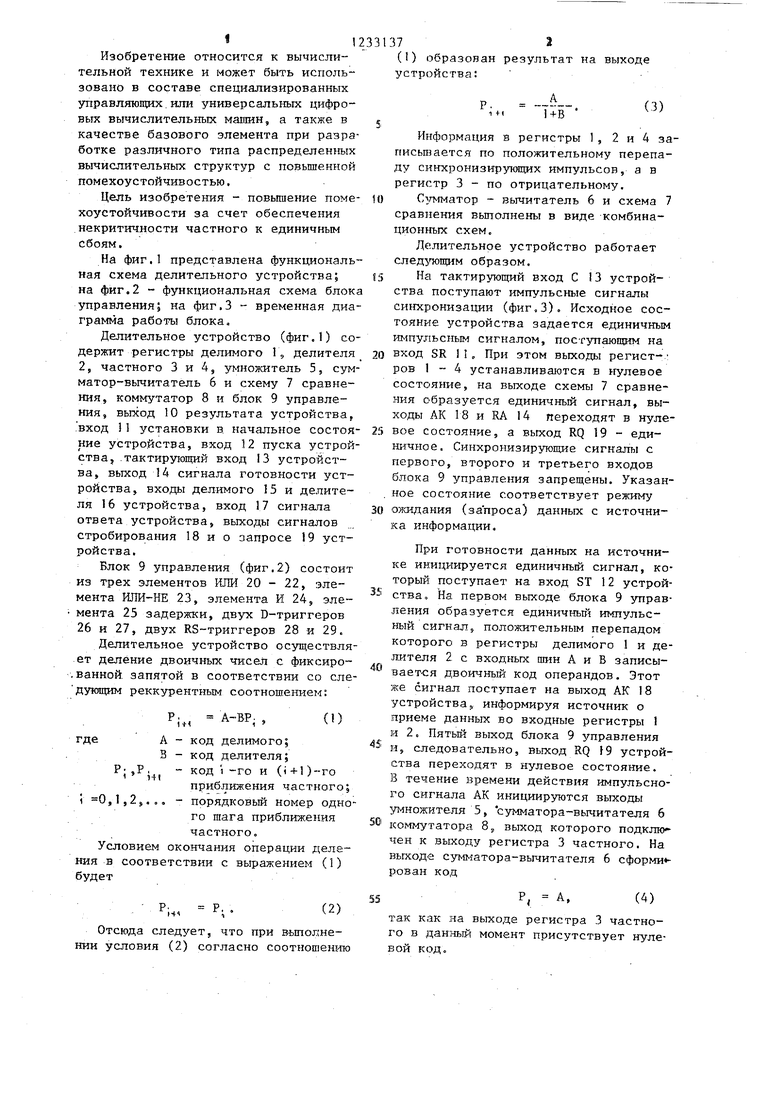

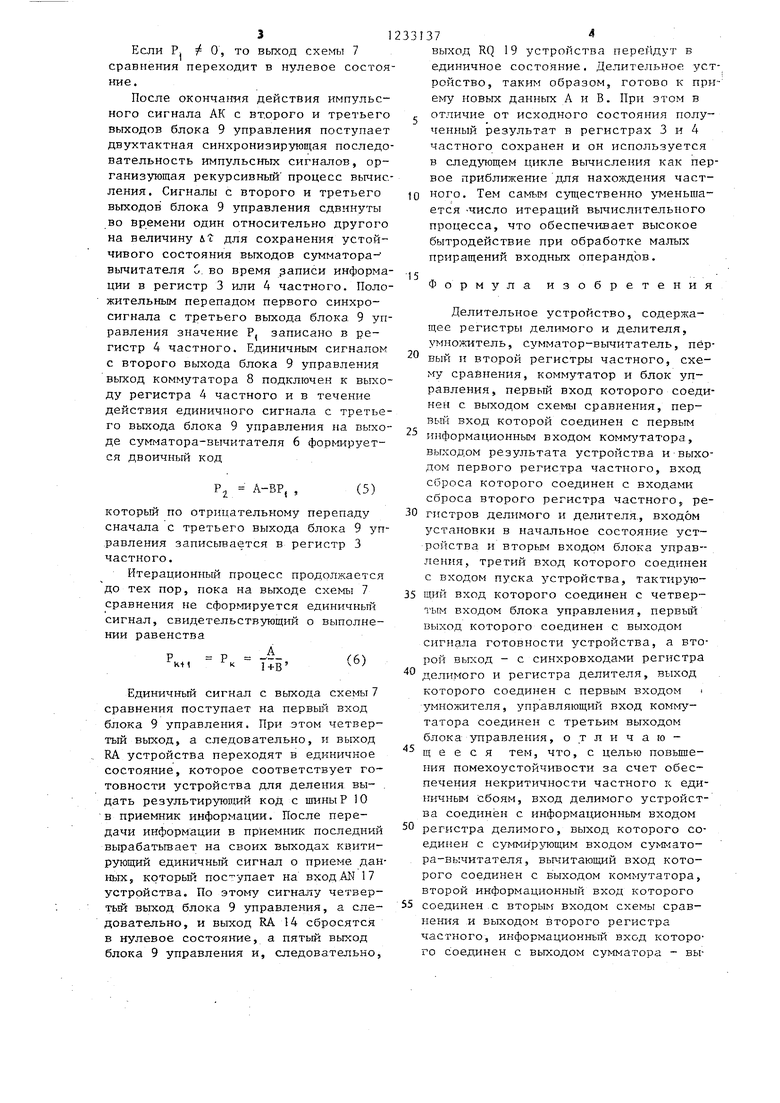

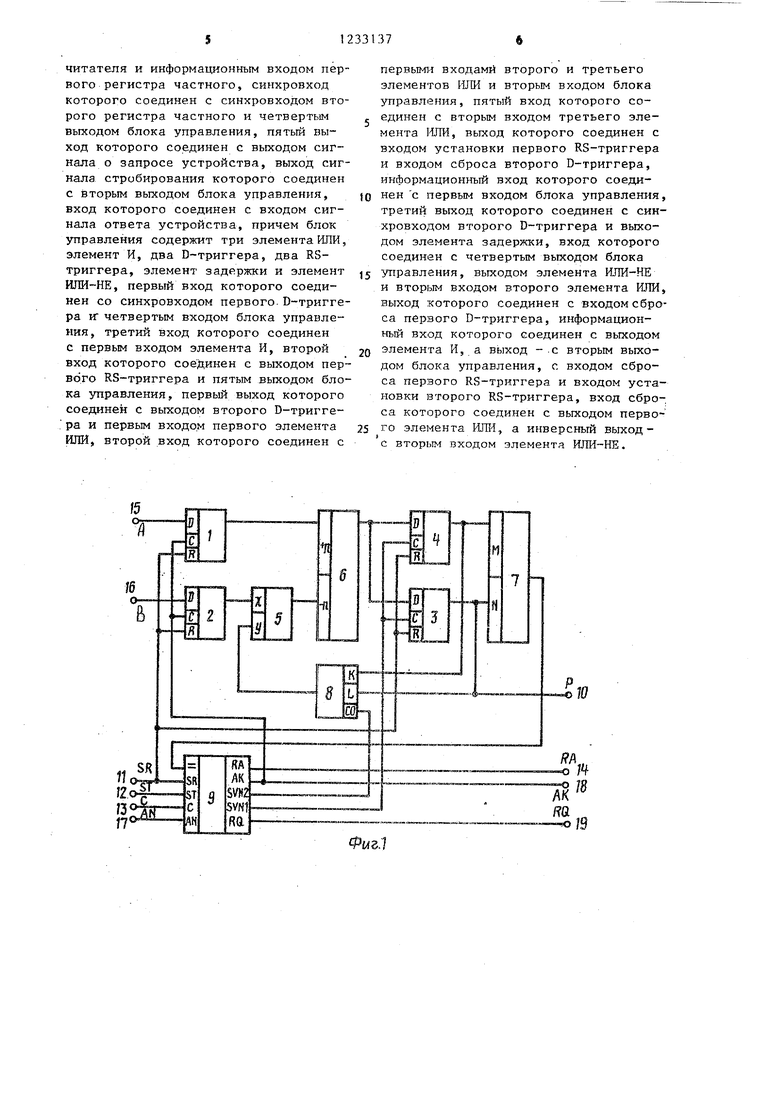

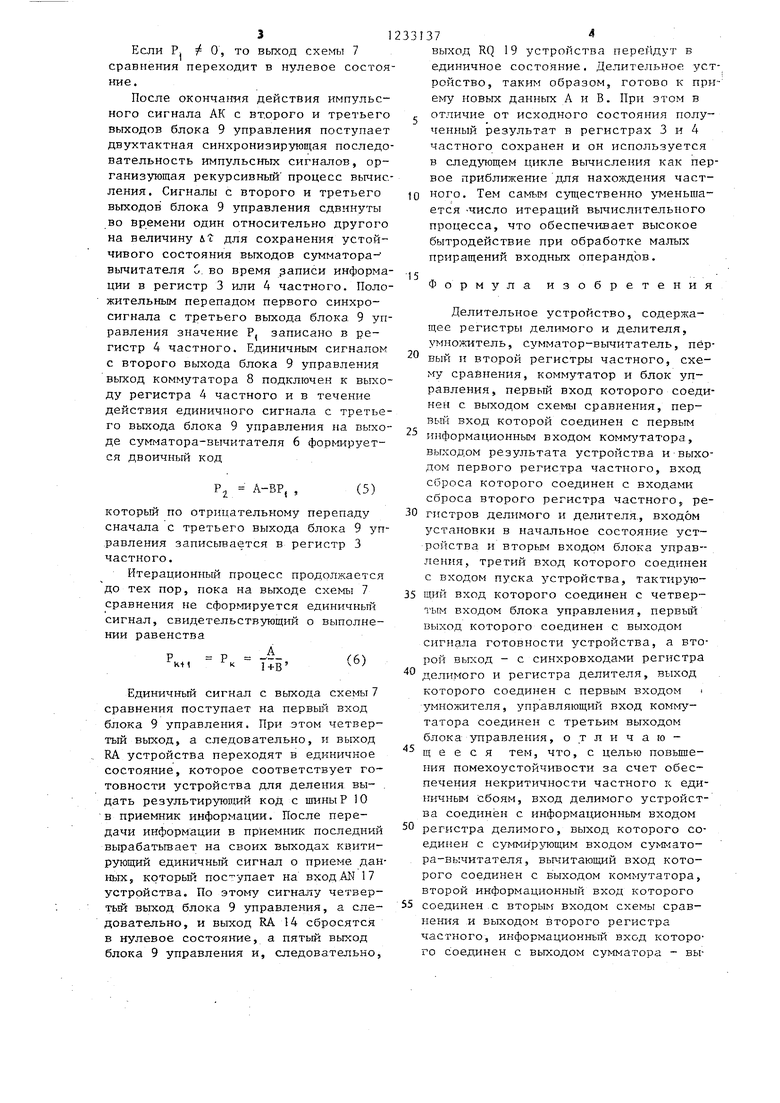

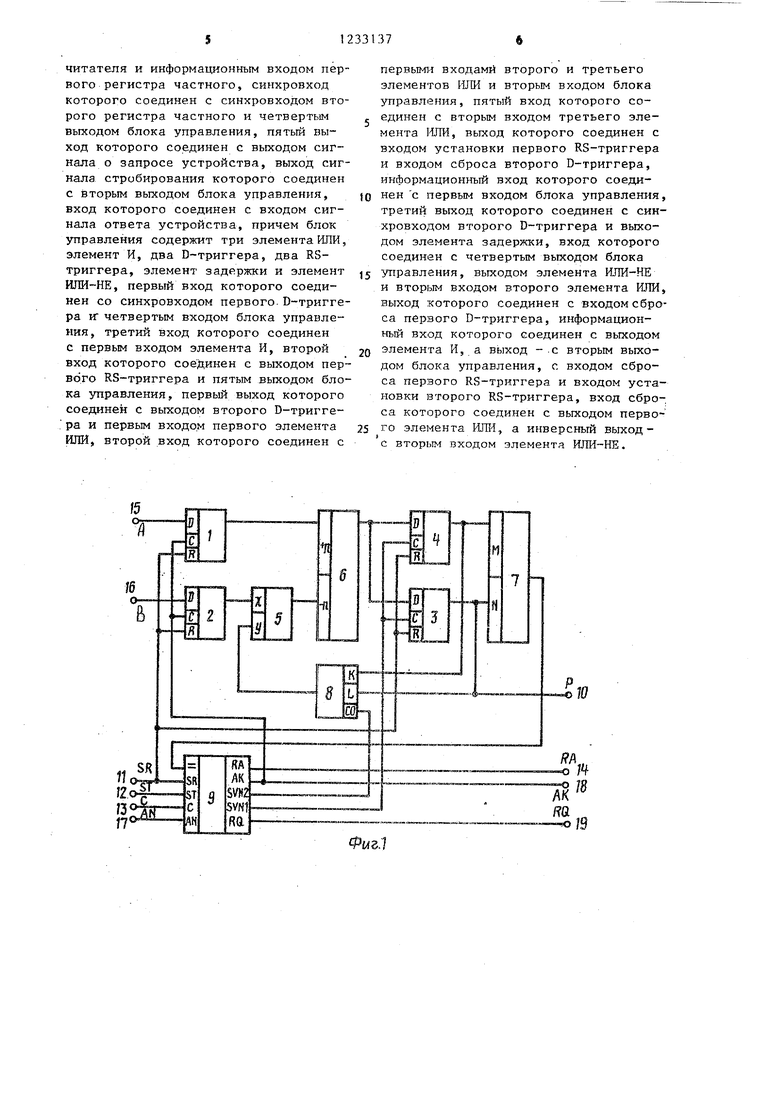

На фиг.1 представлена функциональная схема делительного устройства; на фиг.2 - функциональная схема блока управления; на фиг.З - временная диаграмма работы блока.

Делительное устройство (фиг.1) содержит регистры делимого 1,, делителя 2, частного 3 и 4, умножитель 5, сум- матор-вьгчитатель 6 и схему 7 сравнения, коммутатор 8 и блок 9 управления, выход 10 результата устройства, вход } 1 установки в, начальное состоя- 1ние устройства, вход 12 пуска устройства, .тактирующий вход 13 устройства, выход 14 сигнала готовности устройства, входы делимого 15 и делителя 16 устройства, вход 17 сигнала ответа устройства, выходы сигналов стробирования 18 и о запросе 19 устройства.

Блок 9 управления (фиг,2) состоит из трех элементов ИЛИ 20 - 22, элемента ИЛИ-НЕ 23, элемента И 24, эле- мента 25 задержки, двух D-триггеров 26 и 27, двух КЗ-триггеров 28 и 29.

Делительное устройство осуществля- .ет деление двоичных чисел с фиксиро- .ванной запятой в соответствии со сле- дующим реккурентным соотношением:

и

А-ВР,,

(1)

где

А - код делимого; В - код делителя;

Р;,Р, - код 1 -го и (i+l)-rO

приближения частного; i 0,1,2,.., - порядковый номер одного шага приближения частного.

Условием окончания операции деления в соответствии с выражением (1) будет

р.,

- р

jr I .

(2)

Отсюда следует, что при выполнении условия (2) согласно соотношению

(I) образован результат на выходе устройства:

р. 1 +(

А

I+B

(3)

Информация в регистры 1, 2 и 4 за- письшается по положительному перепау синхронизирующих импульсов, а в регистр 3 - по отрицательному.

С гмматор - вычитатель 6 и схема 7 сравнения выполнены в виде комбина- ционргых схем.

Делительное устройство работает спедующим образом.

На тактирующий вход С 13 устройства поступают импульсные сигналы ситсронизации (фиг.З). Исходное состояние устройства задается единичным импульсным сигналом, поступающим на

вход SR 1I, При этом выходы регист- ров 1 - 4 устанавливаются в нулевое состояние, на выходе схемы 7 сравнения О бразуется единичный сигнал, выходы ЛК 18 и RA 14 переходят в нулевое состояние, а выход RQ 19 - единичное. Синхронизирующие сигналы с первого, второго и третьего входов блока 9 управления запрещены. Указан- кое состояние соответствует режиму

ожидания (запроса) данных с источниа информации.

При готовности данных на источнике инициируется единичный сигнал, который поступает на вход ST 12 устройства. На первом выходе блока 9 управления образуется единичный импульсный сигнал, положительным перепадом которого в регистры делимого 1 и де- .тштеля 2 с входных шин А и В записывается двоичный код операндов. Этот же сигнал поступает на выход АК 18 устройства,, информируя источник о приеме данных во входные регистры 1 и 2. Пятый выход блока 9 управления

н, следовательно, выход RQ }9 устройства переходят в нулевое состояние. В течение времени действия импульсного сигнала АК инициируются выходы /множителя 5, сумматора-вычитателя 6

коммутатора 8, выход которого подклю чен к выходу регистра 3 частного, На выходе cyм aтopa-вычитaтeля 6 сформи - рован код

Р, А, (4)

так как на выходе регистра 3 частного в дан;яый момент присутствует нулевой код.

Если PI 7 О, то выход схемы 7 сравнения переходит в нулевое состояние.

После окончания действия импульсного сигнала АК с второго и третьего выходов блока 9 управления поступает двухтактная синхронизнруищая последовательность импульсных сигналов, организующая рекурсивный процесс вычисления. Сигналы с второго и третьего выходов блока 9 управления сдвинуты во времени один относительно другого на величину it для сохранения устойчивого состояния выходов сумматора- вычитателя С. во время записи информации в регистр 3 или 4 частного. Положительным перепадом первого синхросигнала с третьего выхода блока 9 управления значение Р, записано в регистр 4 частного. Единичным сигналом с второго выхода блока 9 управления выход коммутатора 8 подключен к выходу регистра 4 частного и в течение действия единичного сигнала с третьего выхода блока 9 управления на выходе сумматора-вычитателя 6 формируется двоичный код

Р,, А-ВР, ,

который по отрицательному перепаду сначала с третьего выхода блока 9 уп- .равления записывается в регистр 3 частного.

Итерационный процесс продолжается до тех пор, пока на выходе схемы 7 сравнения не сформируется единичньш сигнал, свидетельствующий о выполнении равенства

K-ti

I+B

(6)

Единичный сигнал с выхода схемы 7 сравнения поступает на первый вход блока 9 управления. При этом четвертый выход, а следовательно, и выход RA устройства переходят в единичное состояние, которое соответствует готовности устройства для делеция выдать результирующий коД с шины Р 10 в приемник информации. После передачи информации в приемник последний вырабатьтает на своих выходах квитирующий единичный сигнал о приеме дан- m.ix, который пос -упает на входМ 17 устройства. По этому сигналу четвертый выход блока 9 управления, а следовательно, и выход RA 14 сбросятся в нулевое состояние, а пятый выход блока 9 управления и, следовательно,

233137

выход RQ 19 устройства перейдут в единичное состояние. Делителы-гое устройство, таким образом, готово к приему новых данных А и В. При этом в г отличие от исходного состояния полученный результат в регистрах 3 и 4 частного сохранен и он используется в следующем цикле вычисления как первое приближение для нахождения част- 10 ного. Тем самым существенно уменьшается -число итераций вычислительного процесса, что обеспечивает высокое бытродействие при обработке малых приращений входных операндов.

Формула изобретения

Делительное устройство, содержащее регистры делимого и делителя, умножитель, сумматор-вычитатель, пёр20 вый и второй регистры частного, схему сравнения, коммутатор и блок управления, первый вход которого соединен с выходом схемы сравнения, первый вход которой соединен с первым

25 информационным входом коммутатора, вьгходом результата устройства и выходом первого регистра частного, вход сброса которого соединен с входами сброса второго регистра частного ре30 гистров делимого и делителя., входом З становки в начальное состояние устройства и вторым входом блока управления, третий вход которого соединен с входом пуска устройства, тактир то35 щий вход которого соединен с четвертым входом блока управления, первьй выход которого соединен с выходом сигнала готовности устройства, а второй выход - с синхровходами регистра

делимого и регистра делителя, выход которого соединен с первым входом умножителя, управляющий вход коммутатора соединен с третьим выходом блока управления, отличающееся тем, что, с целью повьше- ния помехоустойчивости за счет обеспечения некритичности частного к единичным сбоям, вход делимого устройства соединён с информационным входом

45

50

регистра делимого, выход которого соединен с сумми рзтощим входом сумматора-вычитателя, вычитающий вход которого соединен с выходом коммутатора, второй информационный вход которого 55 соединен ,с вторым входом схемы сравнения и выходом второго регистра частного, информационный вход которого с оединен с вы :одом сумматора - вычитателя и информационным входом первого регистра частного, синхровход которого соединен с синхровходом второго регистра частного и четвертым выходом блока управления, пятый выход которого соединен с выходом сигнала о запросе устройства, выход сигнала стробирования которого соединен с вторым выходом блока управления, вход которого соединен с входом сигнала ответа устройства, причем блок управления содержит три элемента ИЛИ, элемент И, два D-триггера, два RS- триггера, элемент задержки и элемент ИЛИ-НЕ, первый вход которого соединен со синхровходом первого.D-триггера И четвертым входом блока управления, третий вход которого соединен с первым входом элемента И, второй вход которого соединен с выходом первого RS-триггера и пятым выходом блока управления, первый выход которого соединен с выходом второго D-тригге- . ра и первым входом первого элемента ШШ, второй вход которого соединен с

первыми входами второго и третьего элементов ИЛИ и вторым входом блока управления, пятый вход которого со- единен с вторым входом третьего элемента 1-ШИ, выход которого соединен с входом установки первого RS-триггера и входом сброса второго D-триггера, информационный вход которого соедийен с первым входом блока управления, третий выход которого соединен с синхровходом второго D-триггера и выходом элемента задержки, вход которого соединен с четвертым выходом блока

управления, выходом элемента ИЛИ-НЕ и вторьм входом второго элемента ИЛИ, выход которого соединен с входом сброса первого D-триггера, информационный вход которого соединен с выходом

элемента И, а выход - -с вторым выходом блока управления, с входом сброса первого RS-триггера и входом установки второго RS-триггера, вход сброса которого соединен с выходом первого элемента ИЛИ, а инверсный выход- с вторым входом элемента ИЛИ-НЕ.

,3} 12

t, tg

t

.Редактор Н.Бобкова

3 tj « .J

Составитель Е.Захарченко

Техред Л.Олейник Корректор В.Бутяга

Заказ 2771/50 Тираж 671Подписное

ВНИИГШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно -полиграфическое предприятие, г. Ужгород, ул. Проектная,4

-f°o

iЙ

a:C

OQOQ

tfS.Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство для деления двоичных чисел | 1985 |

|

SU1270758A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| Устройство для деления | 1986 |

|

SU1429110A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для деления | 1985 |

|

SU1283752A1 |

| Устройство для деления | 1989 |

|

SU1667060A1 |

| Устройство для деления | 1989 |

|

SU1709301A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

Изобретение относится к вычислительной технике и может быть использовано в составе специализированных управляющих или .универсальных цифровых вычислительных машин, а также в качестве базового элемента при разработке различного типа распределенных вычислительных структур с повьпаенной помехоустойчивостью. Целью изобретения является повьшение помехоустойчивости за счет обеспечения некритичности к единичным сбоям в канале передачи и преобразования данньтх. В делительное устройство, содержащее регистры делимого и делителя, первый и второй регистры частного,-перемножитель, сумматор-вычитатель, схему сравнения, коммутатор и блок управления, введена обратная связь с выходов регистров частного через коммутатор на второй вход перемножителя и обратная связь по цепям управления с выхода cxeNflj сравнения через блок управления. 3 ил. I (Л ::о 00 со

| Вычислительное устройство | 1980 |

|

SU989556A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1978 |

|

SU781813A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-23—Публикация

1984-07-03—Подача