I1236466

Изобретение относится к вычислительной технике и может быть использовано для одновременного вычисления функций F (х, у), Fj (х, у), в частности, для аппаратного преоб- § разования молярных координат в депкартовые и функций ZZ ( У

V

(х, УР z), в частности, для ко- :-. о герентного накопления.

Целью изобретения является расширение класса решаемых задач за счет возможности выполнения когерентных сумм.

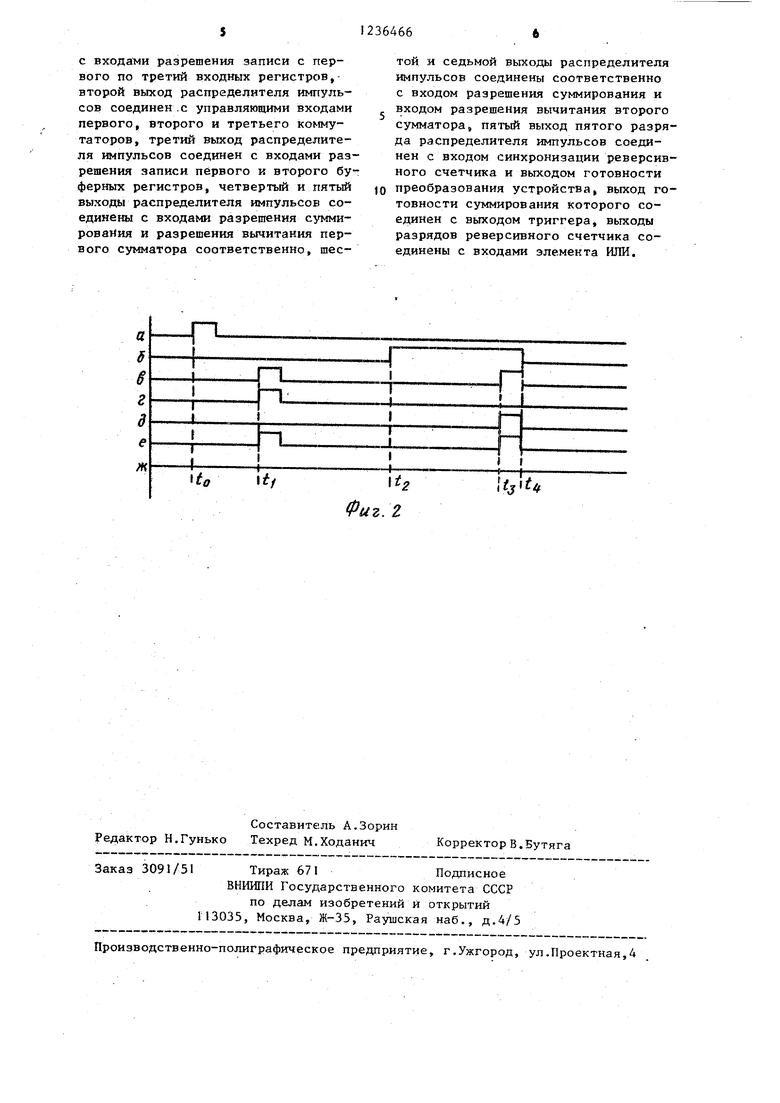

На фиг, представлена блок-схема устройства; на фиг. 2 - временная диаграмма работы устройства при выполнении преобразования координат.

Устройство содержит реверсивный счетчик 1, элемент ИЛИ 2, генератор 3 импульсов, элемент И 4, распределитель 5 импульсов, триггер 6, сумматоры 7 и 8, буферные регистры 9 и 10, блоки 11 и 12 умножения, коммутаторы 13 - 15, блоки 16 и 17 памяти, входные регистры 18 20, вход 21, выходы 22 и 23,

Вычисление значений функций F, (х у) и F,j (х, у) проводят на основе соотношений

F (х, у) f (xj t дх f,, (xj.y ; F(x, у) t ux f, (х„) y,(

где x - определяется старшими разрядами х;

ux определяется младшими разрядами аргумента х„

Вычисление значений функций F, (х, у, z), F (х, у, z) проводят на основе соотношений

F, (х, у, z) (x;)y + f(x,. ) Z,,

1 0 .

Fj(x, y, z) ,(x,)y; t f, (x.) z,i

2)

Для функций преобразования нелинейных координат в декартовы с формулы (1) имеем

X г COS ч - йЧ г sinM ,

(3)

у г + йЧ т созЧ д

Для функ1дай когерентного Накопления с формулы (2)имеем

(A. - В. sin4.)i

1 --0

(4)

к

IZ (в, COS Ч ;

( - о

+ А. .)

Рассмотрим работу устройства на примере ,(3) и (4),

)

to

IS

20

25

30

35

40

45

)

50

В блоках 16 и 17 памяти хранятся соответственно значения cos Ч и sin м-.

Предварительно выходы распределителя 5 импульсов, выход триггера 6, счетчика 1, выходы первого 18, второго 19, третьего 20 входных регистров установлены в нулевое состояние (цепи установки не приведены),

Для вычисления преобразований по формуле (3) по сигналу на входе 21 в счетчик 1 записывается единица,, указывающая, что устройство проводит вычисления один раз, разрешающая прохождение тактовых импульсов с генератора 3 импульсов через элемент И 4 на распределитель 5 импульсов, который формирует на своем первом выходе импульс (фиг, 2 ), по которому осуществляется прием информации в входные регистры 8 - 20, При этом в первый 18 входной регистр записываются значение Ч , во второй 19 - значение г, в третий 20 - значение йЧ которое определяется младшими разрядами аргумента. Так как на втором выходе распределителя 5 импульсов нулевой уровень (фиг.25), первый 13, второй 14 и третий 5 коммутаторы открыты, т.е. на первом блоке 11 умножения образуется значение г втором блоке 12 у1-1Ножения - значение г sin, которые в момент t| записываются соответственно в второй 10 и первый 9 (фиг, ЗЬ) буферные регистры и поступают на первый 7 и второй 8 сумматоры, в которых по сигналам на входах суммирования (фиг, 4г,е ) запоминаются в этих блоках, т.е. в первом 7 и втором 8 сумматорах записываются соответственно г-cos ч и г sinM ,

35

После этого в момент t на втором выходе распределителя 5 импульсов устанавливается единичный уровень, по которому на первом блоке I1 умно- уленкя образуется значение а Ч sin Ч .

о

на втором блоке 12 умножения аЧ г cos f

которые записьюаются в

момент t в буферные регистры 10

3

и 9 (фиг. 2е) и по сигналу вьгчи- тания (фиг. 2г) на первом 7 сумматоре по сигналу суммирования (фиг.2 на втором 8 сумматоре происходят соответственно вычисления функций

X г cos sin Ч ,

У г -sin + дчт .

Одновременно с пятого выхода распределителя 5 импульсов поступает сигнал на выход 22, указывающий, что устройство обработало данные, и на синхровход счетчика 1, который по заднему фронту сигнала устанавливается в нулевое состояние. Нулевой перепад через элемент ИЛИ 2 устанавливает в единичное состояние триггер 6, выход которого -указьшает, что устройство закончило работу и запрещает прохождение импульсов с генератора 3 тактовых импульсов через элемент И 4.

Работа устройства по обработке преобразований по формуле (4) происходит аналогично. Различия заключаются в том, что предварительно в счетчик 1 по сигналу на входе 21 записьшается п. В первь) 18, второй 19, третий 20 входные регистры записываются в момент t соответственно значения Ч ,,, cos Ч , sin f. В момент t, на блоках 7 и 8 сут 1мирования после первого этапа сформированы значения .

К, A, - B sinM ,

К В„со8ч + .

Сигнал на пятом выходе (фиг. 2а,

Ч)

к, B,cos4; + а в момент t,

h

А„31пЧ

+ В совч ,

указывает внешним устройствам , что устройство закончило одно вычисление и к моменту t второго цикла ему необходимо выставить на информационные входы (не показаны) входных регистров значения cos Ч, В, , А,. Кроме того, этот сигнал уменьшает на единицу содержимое счетчика 1 . В момент t, второго цикла на сумматорах 7 и 8 сформированы значенияК, B, A,cos,,

Ц (AjCosV,- Bj sin Ч .),

I :O

Kj (В. cos4. + A.sinM.).

.

Так продолжается до момента обработки всех значений. После чего, как и в обработке преобразований

t5

20

25

364664

по формуле (3) счетчик I устанавливается в нулевое состояние и на

выходе триггера 5 формируется признак конца работы,

, В общем случае при вычислении других функций выход конца вычислений функций может быть соединен с одним из выходов 4-7.

10 Формула изобретения

Устройство для преобразования координат, содержащее два блока умножения, три коммутатора, три входных регистра, два сумматора, два блока памяти и два буферных регистра, причем выхода первого и второго блоков памяти соединены с первыми информационными входами первого и второго коммутаторов соответственно, вторые информационные входы которых соединены с выходами первого и второго буферных регистров соответственно, вьгходы первого и второ- . го коммутаторов соединены с первыми входами соответственно первого и второго блоков умножения, вторые, входы которых соединены с выходом третьего коммутатора, выходы первого и второго блоков умножения соединены с информационными входами соответственно первого и второго сумматоров и информационными входами соответственно второго и первого буферных регистров, выход первого входного регистра соединен с адресными входами первого и второго блоков памяти, вьгходы второго и третьего входных регистров соединены соответственно с первым и вторым информационными входами третьего коммутатора, отличающееся тем, что, с целью расширения класса решаемых задач за счет возможности вычисления когерентных сумм, в него введены реверсивный счетчик, элемент И, элемент ИЛИ распределитель импульсов, генератор импульсов и триг- гер, причем вход записи устройства соединен С установочным входом реверсивного счетчика и входом установки в О триггера, вход установки в 1 которого соединен с выхо- дом элемента ИЛИ и первым входом элемента И, второй вход и выход ко- 5 торого соединены соответственно с выходом генератора импульсов и тактовым входом распределителя импульсов, первый выход которого соединен

30

5

0

5

0

с входами разрешения записи с первого по третий входных регистров, второй выход распределителя имгсуль- сов соедииен .с управляющими входами первого, второго и третьего коь1му- таторов, третий выход распределителя импульсов соединен с входами разрешения записи первого и второго буферных регистров, четвертый и пятый выходы распределителя импульсов со- единень с входами разрешения суммирования и разрешения вычитания первого сумматора соответственно, шесСоставитель А.Зорин Редактор Н.Гунько Техред М.Ходанич

3091/51

Тираж 671Подписное

ВНИШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

2364666

той и седьмой выходы распределителя импульсов соединены соответственно с входом разрешения суммирования и входом разрешения вычитания второго сумматора, пятый выход пятого разряда распределителя импульсов соединен с входом синхронизации реверсивного счетчика и выходом готовности )0 преобразования устройства, выход готовности суммирования которого соединен с выходом триггера, выходы разрядов реверсивного счетчика соединены с входами элемента ИЛИ.

Корректор В.Бутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой генератор периодической функции | 1987 |

|

SU1432491A1 |

| Устройство для вычисления функции | 1985 |

|

SU1280614A1 |

| Устройство для преобразования координат | 1983 |

|

SU1141405A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

| Векторный процессор | 1979 |

|

SU849228A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

| Цифровой функциональный преобразователь | 1982 |

|

SU1027732A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

Изобретение относится к вычислительной технике и предназначено для одновременного вычисления функций FJ (х, у), F,.,(x, у), в частности, для аппаратного преобразования полярных координат в декартовые и -.и функций YH F (х, у, z), Е.(х, y,z), froi o 8частности, для когерентного накопления . Цель изобретения - расширение функциональных возможностей за счет вычисления когерентных сумм. Устройство содержит реверсивный счетчик 1, элемент ИЛИ 2, генератор 3 импульсов, элемент И 4, распределитель 5 импульсов, триггер 6, сумматоры 7 и 8, буферные регистры 9и 10, блоки И и 12 умножения, коммутаторы 13 - 15, блоки 16 и 17 памяти и входные регистры 18-20, 2 ил. i (Л

| Устройство для вычисления функций синуса и косинуса | 1977 |

|

SU622090A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления функций | 1982 |

|

SU1078427A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1986-06-07—Публикация

1984-11-19—Подача