Изобретение относится к вычислительной технике и может быть HcnovibsosaHo в запоминающих устройствах для усиления сигналов считываемой информации.

Цель изобретения - повышение чувствительности усилителя считывания.

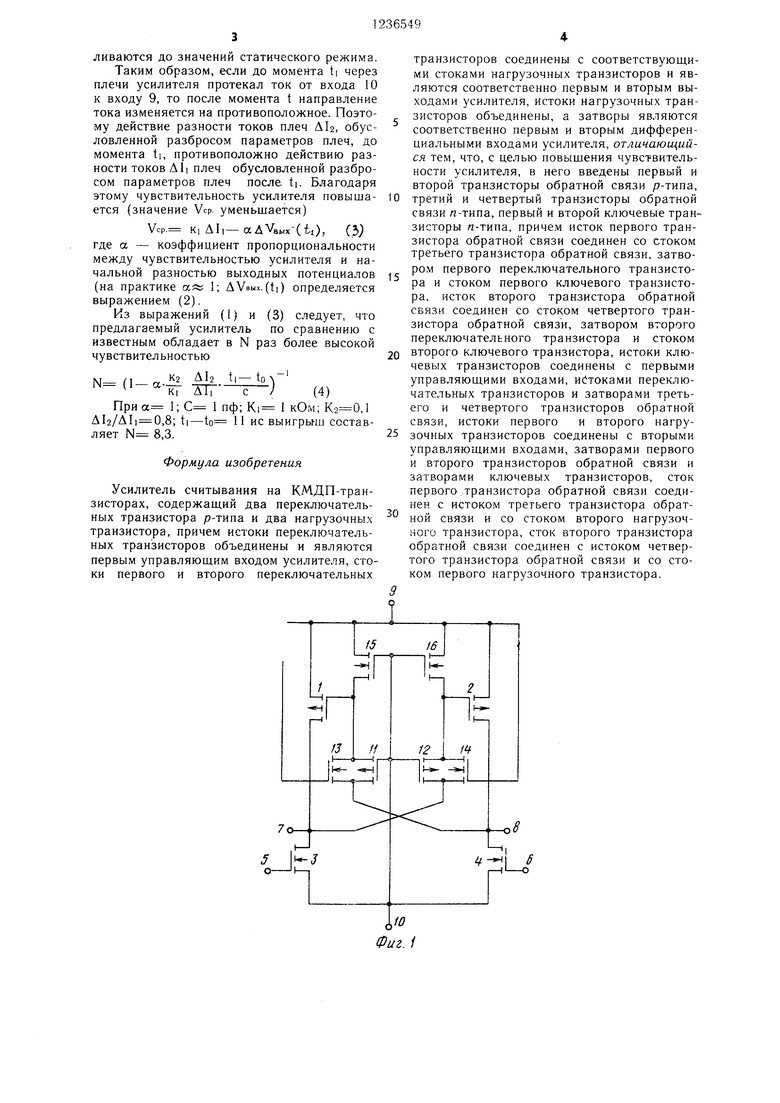

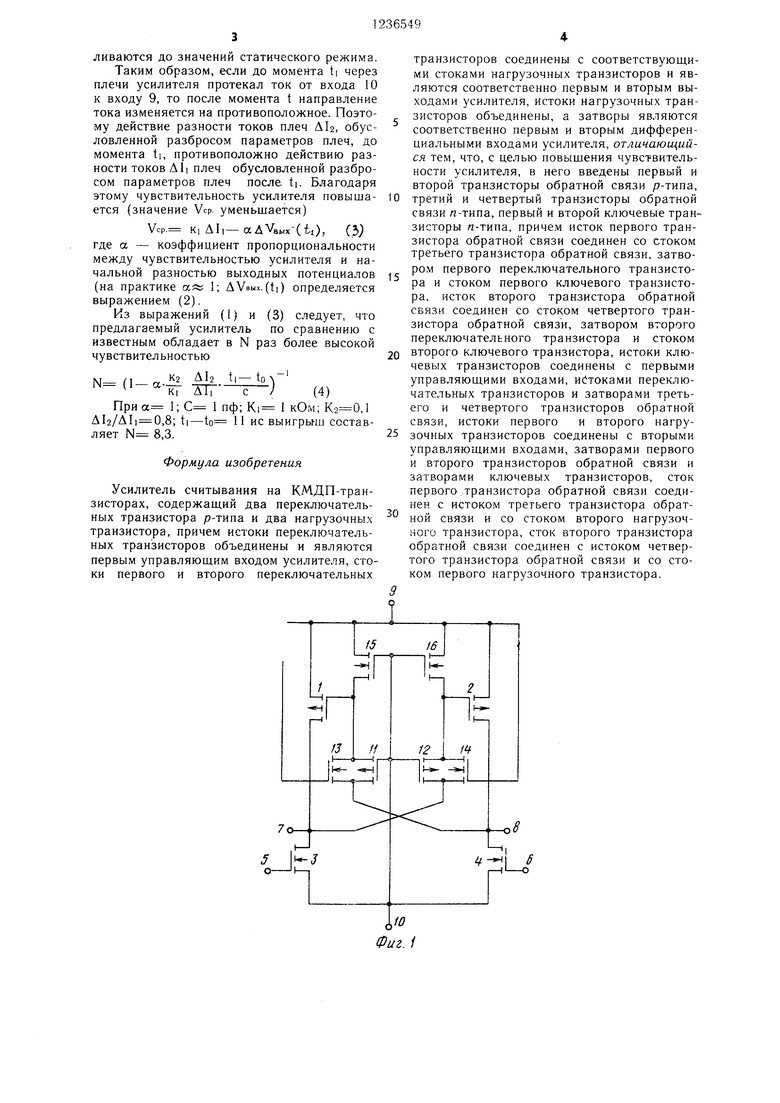

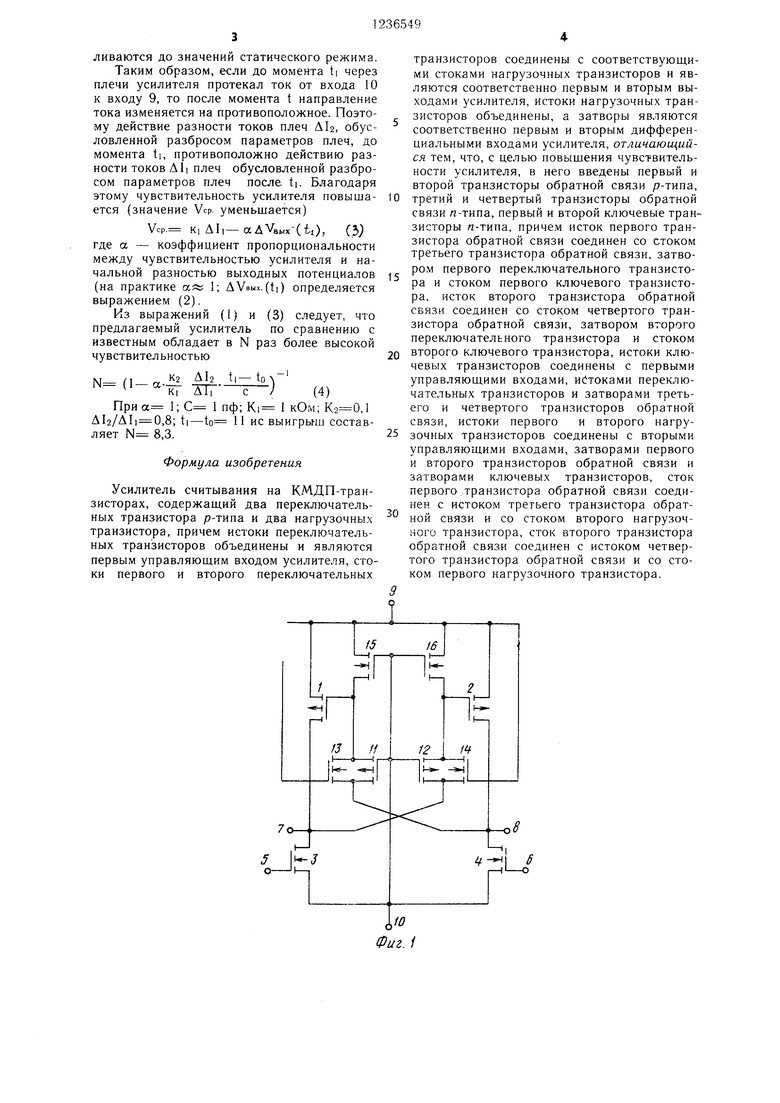

Схема усилителя считывания показана на фиг. 1, на фиг. 2 - временная диаграмма работы усилителя.

Усилитель содержит первый 1 и второй 2 переключательные транзисторы р-типа, первый и второй нагрузочные транзисторы 3 и 4 л-типа, первый 5 и второй 6 дифференциаль ные входы, первый 7 и второй 8 выходы, первый 9 и второй 10 управляющие входы, первый 11 и второй 12 транзисторы обратной связи р-типа, третий 13 и четвертый 14 транзисторы обратной связи д-типа, первый 15 и второй 16 ключевые транзисторы п-типа, причем истоки первого 1 и второго 2 переключательных транзисторов объединены, сто ки соединены соответственно с первым 7 и вторым 8 выходами, которые соединены соответственно со стоками первого 3 и второго 4 нагрузочных транзисторов, истоки которых объединены, а затворы являются первым 5 и вторым 6 дифференциальными входами, исток первого транзистора 11 обратной связи соединен со стоком третьего транзистора 13 обратной связи, затвором пер вого переключательного транзистора 1 и стоком первого ключевого транзистора 15, исток второго транзистора 12 обратной связи соединен со стоком четвертого транзистора 14 обратной связи, затвором второго переключательного транзистора 2 и стоком второго ключевого транзистора 16, истоки ключевых транзисторов 15 и 16 соединены с первым управляющим входом 9, исто ками переключательных транзисторов 1 и 2 и затворами третьего 13 и четвертого 14 транзисторов обратной связи, истоки первого 3 и второго 4 нагрузочных транзисторов соединены с вторым управляющим входом 10, затворами первого 11 и второго 12 транзисторов обратной связи и затворами ключевых транзисторов 15 и 16, сток первого транзистора 11 обратной связи соединен с истоком третьего транзистора 13 обратной связи и со стоком второго нагрузочного транзистора 4, сток второго транзистора 12 обратной связи соединен с истоком четвертого транзистора 14 обратной связи, а также со стоком первого нагрузочного транзистора 3.

Усилитель считывания работает следующим образом.

В статическом режиме на управляющих входах 9 и 10 поддерживаются низкие уровни напряжения, соответствующие напряжению логического «О, а на дифференциальных входах 5 и 6 - напряжение логической «1. При этом транзисторы 3 и 4 открыты, а транзисторы 1, 2, 11 -16 закры10

15

20

25

30

35

ТЫ. в результате на выходах 7 и 8 также под держиьается напряжение логического «О. Поскольку транзисторы 11 и 12 оказываются в диодном включении (затворы объединены со стоками через открытые транзисторы 1 и 2), то напряжение на затворах транзисторов 1 и 2 находится в диапазоне от значения напряжения логического «О до порогового напряжения транзисторов 11 и 12 р-типа.

В режиме считывания информации (временная диаграмма на фиг. 2) в момент времени to на вход 10 подается высокий уровень напряжения Vio, равный логической «1. Начинается первый этап - формирование компенсирующей разности выходных напряжений AVnux.(t) V (t|)-V8(ti) с целью компенсации разброса параметров плеч усилителя. В известном устройстве реализация этого этапа без дополнительных элементов и связей невозможна, и чувствительность усилителя равна

Уср.кЛ1,(1)

где All - разность токов плеч известного усилителя, обусловленная разбросом параметров плеч усилителя, при разомкнутой обратной связи, когда затворы транзисторов I и 2 соединены со своими стоками;

Ki - коэффициент, зависящий от параметров транзисторов усилителя.

При этом транзисторы 11-14 обратной связи закрыты, а транзисторы 3, 4, 15 и 16 оказываются в диодном включении. К моменту ti разность выходных напряжения становится равной

.,(t,) V7(t,)-V8(ti)

К2

(2;

где Ala - средняя за время (ti - to) разность

токов плеч усилителя; с - емкость выходов усилителя; К2 - коэффициент, зависящий от параметров транзисторов усилителя.

В момент ti начинается собственно считывание информации: на дифференциальные входы 5 и 6 подается разность потенциалов, соответствующая считываемой информации, напряжение V9 устанавливается равным логической 1, а Ую - логическому 0. При этом транзисторы 11 -14 обратной связи открываются, а транзисторы 15 и 16 закрываются. В схеме начинается регенеративный процесс, в результате которого на выходах 7 и 8 усилителя устанавливаются напряжения логического О и логической 1 в соответствии со считываемой информацией ( в соответствии со знаком входной разности потенциалов). В момент tg начинается этап восстановления, и потенциалы устанавливаются до значений статического режима. Таким образом, если до момента ti через плечи усилителя протекал ток от входа 10 к входу 9, то после момента t направление тока изменяется на противоположное. Поэтому действие разности токов плеч ДЬ, обусловленной разбросом параметров плеч, до момента ti, противоположно действию разности токов Д1| плеч обусловленной разбросом параметров плеч после ti. Благодаря этому чувствительность усилителя повышается (значение Vcp. уменьшается)

Vcp. к, Д1|-aAV8Mx-(t,), (3) где а - коэффициент пропорциональности между чувствительностью усилителя и начальной разностью выходных потенциалов (на практике а 1; ДУвых.(11) определяется выражением (2).

Из выражений (1) и (3) следует, что предлагаемый усилитель по сравнению с известным обладает в N раз более высокой чувствительностью

N « -f ) ,4)

Приа 1; С 1 пф; Ki 1 кОм; ,1 Д12/Д11 0,8; t|-to 11 ис выигрыш составляет N 8,3.

Формула изобретения

Усилитель считывания на КМДП-тран- зисторах, содержаш,ий два переключательных транзистора р-типа и два нагрузочных транзистора, причем истоки переключательных транзисторов объединены и являются первым управляюш,им входом усилителя, стоки первого и второго переключательных

0

5

0

5

транзисторов соединены с соответствующими стоками нагрузочных транзисторов и являются соответственно первым и вторым выходами усилителя, истоки нагрузочных транзисторов объединены, а затворы являются соответственно первым и вторым дифференциальными входами усилителя, отличающийся тем, что, с целью повышения чувствительности усилителя, в него введены первый и второй транзисторы обратной связи /7-типа, третий и четвертый транзисторы обратной связи л-типа, первый и второй ключевые транзисторы п-типа, причем исток первого транзистора обратной связи соединен со стоком третьего транзистора обратной связи, затвором первого переключательного транзистора и стоком первого ключевого транзистора, исток второго транзистора обратной связи соединен со стоком четвертого транзистора обратной связи, затвором второго переключательного транзистора и стоком второго ключевого транзистора, истоки ключевых транзисторов соединены с первыми управляющими входами, истоками переключательных транзисторов и затворами третьего и четвертого транзисторов обратной связи, истоки первого и второго нагрузочных транзисторов соединены с вторыми управляющими входами, затворами первого и второго транзисторов обратной связи и затворами ключевых транзисторов, сток первого .транзистора обратной связи соединен с истоком третьего транзистора обратной связи и со стоком второго нагрузочного транзистора, сток второго транзистора обратной связи соединен с истоком четвертого транзистора обратной связи и со стоком первого нагрузочного транзистора.

%

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания для запоминающего устройства на МДП-транзисторах | 1981 |

|

SU989583A1 |

| Усилитель считывания для матрицы однотранзисторных запоминающих элементов | 1976 |

|

SU661605A1 |

| Усилитель записи-считывания на КМДП-транзисторах | 1988 |

|

SU1571673A1 |

| Усилитель считывания на КМДП транзисторах | 1984 |

|

SU1241285A1 |

| Усилитель-формирователь для оперативного запоминающего устройства на КМДП транзисторах | 1981 |

|

SU999104A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1993 |

|

RU2043665C1 |

| Усилитель считывания | 1983 |

|

SU1134965A1 |

| Усилитель считывания на КМОП-транзисторах | 1983 |

|

SU1149310A1 |

Изобретение относится к вычислите,,1ь- ной технике и .может быть использовано в запоминающих устройствах для усиления сигналов считывания информации. Цель изобретения состоит в повышении чувствительности усилителя. Усилитель содержит два переключательных, нагрузочные транзисторы транзисторь обратной связи, ключевые транзисторы. Введение в устройство транзисторов обратной связи и ключевых транзисторов позволяет компенсировать разброс параметров плеч усилителя считывания, что позволяет повысить его чувствительность 2 ил. ю W № О1 4: XD

Редактор A. Сабо Заказ 3014/55

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП «Патент, г. Ужгород, ул. Проектная, 4

Составитель В. Гордонова

Техред И. ВересКорректор С. Черни

Тираж 543Подписное

| Патент Англии № 2004715, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Патент США N° 4247791, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1986-06-07—Публикация

1984-08-25—Подача