(5) УСТРОЙСТВО для КОНТРОЛЯ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1989 |

|

SU1667159A2 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Устройство для контроля полупроводниковой оперативной памяти | 1982 |

|

SU1051586A1 |

| Устройство для контроля памяти | 1981 |

|

SU1001180A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Запоминающее устройство | 1985 |

|

SU1249594A1 |

| УСТРОЙСТВО ТЕСТОВОГО КОНТРОЛЯ | 2014 |

|

RU2565474C1 |

| Устройство тестового контроля | 1989 |

|

SU1691842A1 |

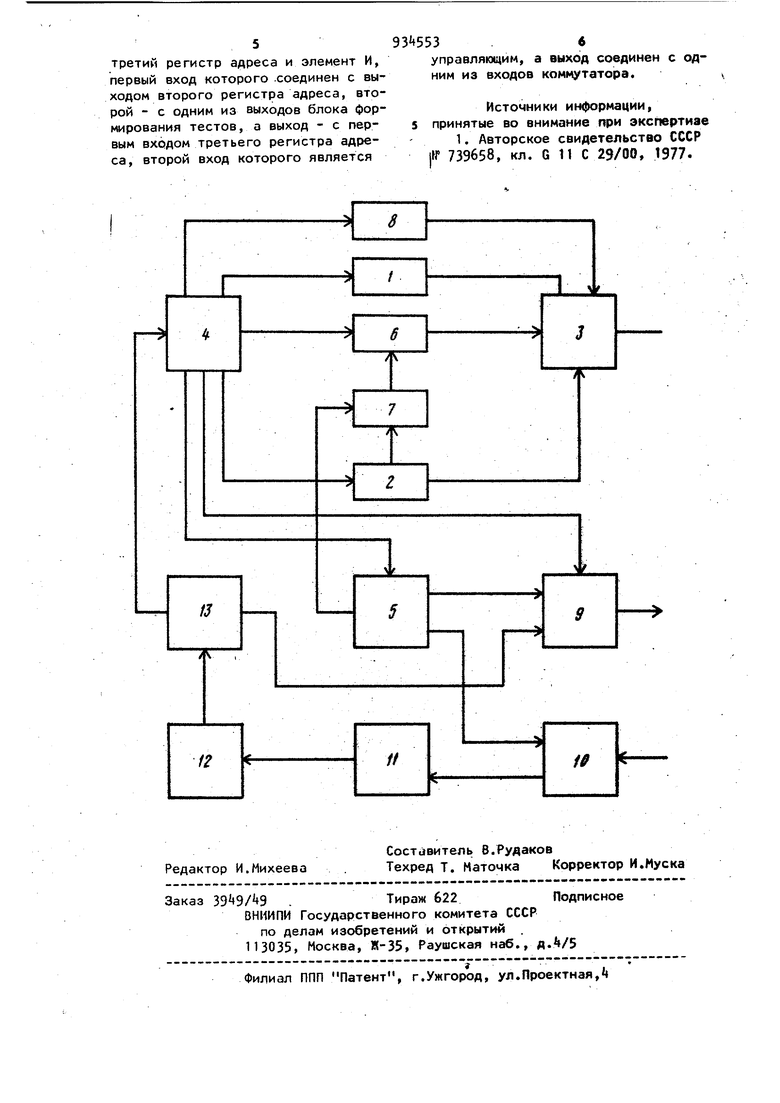

Изобретение относится к запоминаю щим устройствам. По основному авт.св. N° 739658 известно устройство для контроля памяти, содержащее блок Сформирования тестов, выходы которого подключены к одним входам блока формирования импу сов записи и чтения, регистра числа и блока сравнения, другие входы кото рых соединены соответственно с выходом блока местного управления, входом устройства и выходом регистра числа, первый регистр адреса, блок управления, второй регистр адреса, триггер и коммутатор, выход которого соединен с выходом устройства, а входы подключены соответственно к вы ходам триггера и регистров адреса, входы триггера и второго регистра адреса соединены с выходами блока управления 1J. Недостатком описанного устройства является то, что оно не позволяет формировать адресные переходы внут ри креста, строки или столбца матрицы информации, позволяющие генерировать сокращенные тесты, что вызывает увеличение времени контроля и, следовательно, снижает быстродействие устройства. цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для контроля памяти введены третий регистр адреса и элемент И, первый вход которого соединен с выходом второго регистра адреса, второй - с одним из выходов блока формирования тестов, а выход - с первым входом третьего регистра адреса, второй вход которого является управляющим, а выход соединен с одним из входов коммутатора. На черте ; е изображена структурная схема устройства для контроля памяти. Устройство содержит первый 1 и второй 2 регистры адреса, коммутатор 3, блок 1 управления, блок 5 формирования тестов, третий регистр 6 адреса, элемент И 7, триггер 8, блок 9 формирования импульсов записи и чтения, регистр 10 числа, блок 11 сравнения, блок 12 останова и блок 13 местного управления. Разрядность адреса р проверяемого блока оперативной памяти состоит из количества строк m и столбцов л в мат рице памяти p-m+n. Разрядность регистра 2 равна числу строк т, а разрядность регистра 6 рав на числу столбцов п. Выходные сигналы реги стров 2 и 6, поступая на соответствуюи ие входы коммутатора 3 на его выходе образуют полный адрес проверяемого блока памяти. Устройство работает следующим образом. При формировании адресных переходов типа крест из блока k управления на блок 5 и регистры 1, 2 и 6 поступйют установочные сигналы. Блок 5 выдает на элемент И 7 запрещающий потенциал. Проверка наминается с исходного нулевого адреса, который устанавлива ется на регистре 1. В регистре 2 уста навливается первый адрес, соответствующий первой строке, а в регистре 6 устанавливается адрес нулевого столб ца. По сигналам из блоков и 5 запускаются триггер 8 и блок 9 формирования импульсов записи и чтения, и по двум адресам, определяемым состояниями регистра 1 и суммой адресов регистров 2 и 6, выполняется обращение, соответствующее заданному тесту. Далее добавляется единица в регистр 2 и аналогичное обращение производится по следующей паре адресов: адрес регистра 1 и новый адрес регист ров 2 и 6. I Аналогичным образом производятся обращения по остальным адресам столбца до достижения регистром 2 адреса на единицу меньшего исходного, т.е. нулевого. Прекращается добавление еди ницы в регистр 1 и начинается подача этих сигналов в регистр 6, который устанавливается в состояние первого адреса - адреса первого столбца. После обращения по данной новой паре адресов производится обращение по ДРУГОЙ паре адресов, отлйчающейся состоянием регистра 6 ( адрес второго столбца), и т.д. до достижения регистром 6 исходного состояния, равного состоянию регистра 1. Первый такт формирования адресных переходов окончен. Второй и последующий такты производятся аналогично с добавлением единицы в регистры 2 и 6 до достижения ими исходного состояния, равного состоянию части п регистра 1 ( для регистра 6) и части т регистра 1 ( для регистра 2}. Характер обращения по каходому из адресов в проверяемой паре определяется блоком 9, а обращение к тому или иному адресу в паре определяется триггером 8 в зависимости от заданного проверяющего теста. Для формирования адресных переходов внутри строки или столбца в такте обращения перебор адресов производится только одним из регистров, второй хе постоянно находится в состоянии, равном соответствующей части m или п регистра 1. При формировании адресных переходов для тестов типа N (где N емкость проверяемого блока памяти} из блока 5 выдается разрешающий потенциал на элемент И 7 через который регистр 6 запускается сигналами переполнени)ч регистра 2. Добавление единицы из блока ( в регистр 6 не производится. Триггер 8 по сигналам из блока в коммутаторе 3 производит требуемый выбор выходов регистров 1 или 2 и 6 по типу генерируемого теста. Считанная из проверяемого блока памяти информация принимается на регистр 10,сравнивается с эталонной в блоке 11 и при обнаружении ложной запускает блок 12 останова, который выдает сигнал Останов в блок 1 местного управления. Предлагаемое устройство позволяет формировать адресные переходы для более коротких тестов типа N«, что приводит к снижению времени проверки полупроводниковых блоков памяти большой информационной емкости. формула изобретения Устройство для контроля памяти поавт.св. № 739658, отличающееся тем, что, с целью повышения быстродействия, оно содержит

Авторы

Даты

1982-06-07—Публикация

1980-12-18—Подача