Изобретение относится к вычисли- тельной технике и может быть применено в системах, в которых один блок памяти одновременно используется несколькими процессорами.

Цель изобретения - увеличение быстродействия устройства.

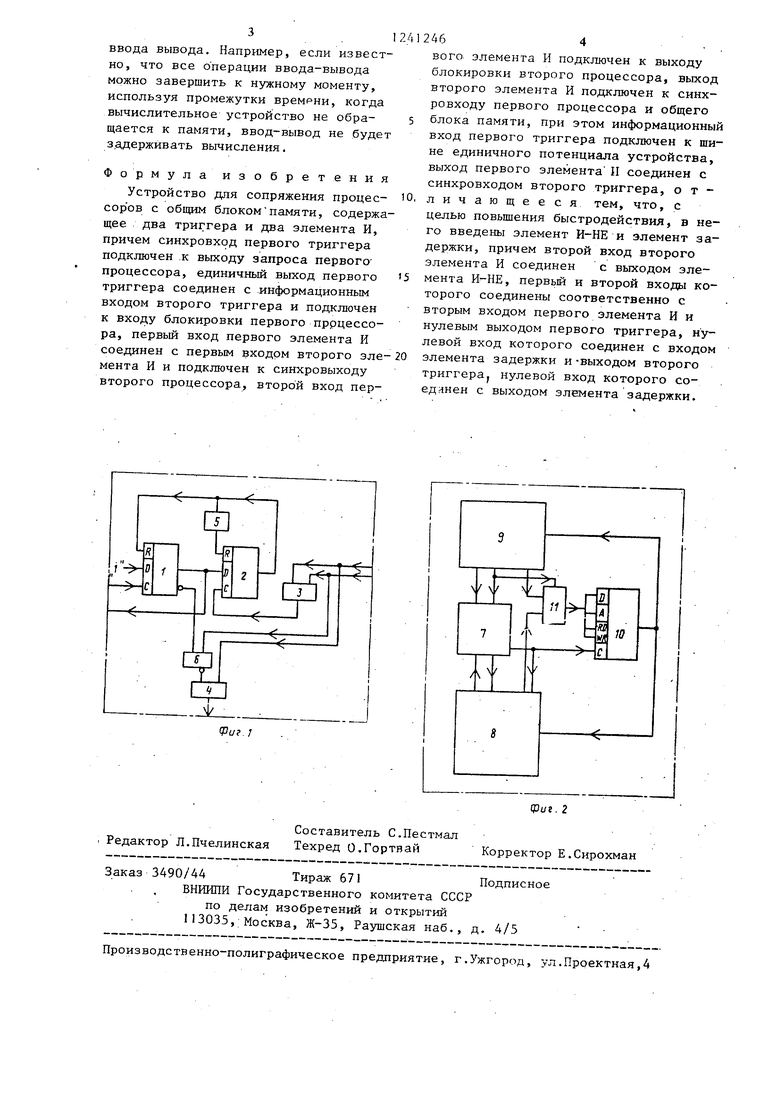

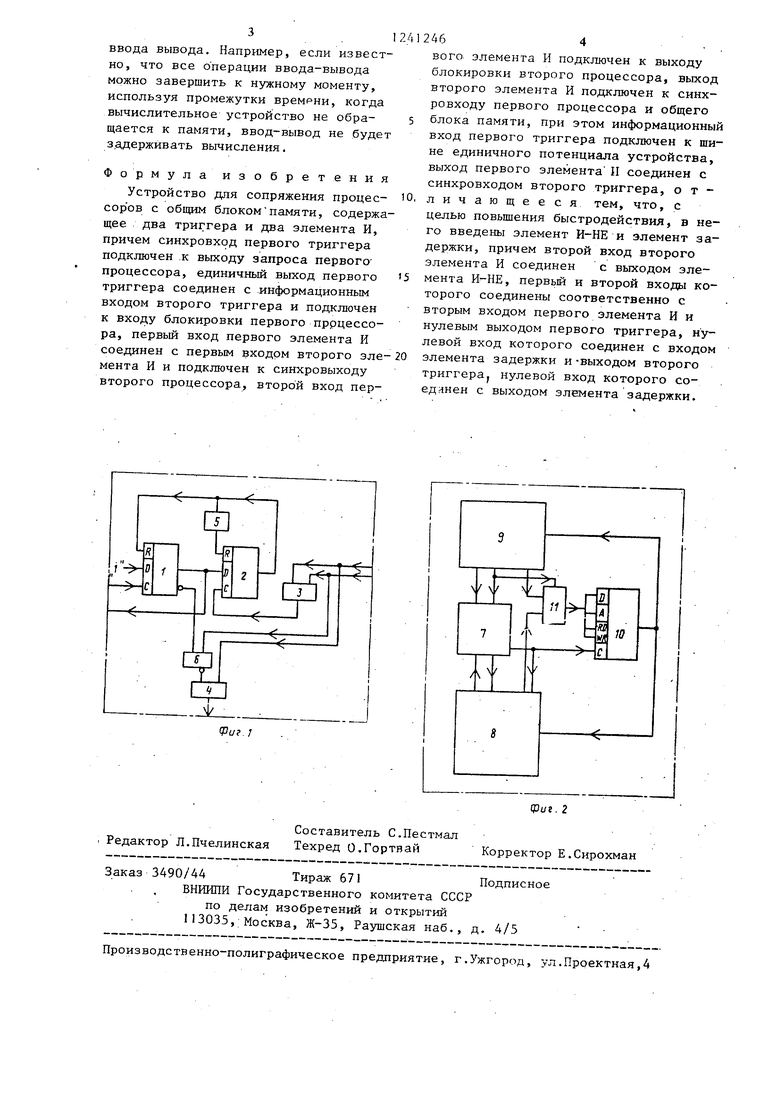

На фиг.1 приведена схема устройства, а на фиг.2 - мсхема использования устройства совместно с двумя процессорами и общим блоком памяти.

Устройство (фиг.1) содержит первый 1 и второй 2 триггеры, первьий 3 и второй 4 элементы И, элемент 5 задержки и элемент И-НЕ 6. На фиг.2 приведены устройство 7 для сопряжения, процессоры 8 и 9, блок 10 памяти и мультиплексор 11.

Устройство работает следующим образом. .

Пусть в начальньй момент времени первый триггер 1 находится в состоянии о, при этом отсутствует блокировка первого процессора 8, и прохождением синхронизирующего сигнала с входа Синхронизации устройства на выход синхронизации управляет второй процессор 9. При поступлении от первого процессора 8 запроса на обслуживание по входу запроса устройства 7 первый триггер 1 переходит в состояние I, вызывающее блокировку по синхронизирующему выходу следующего запроса от первого процессора 8. Обслуживание запроса первого процессора 8 осуществляется при отсутствии запроса от процессора 9. При этом на входе блокировки устройства 7 устанавливается потенциал 1, тем самым управление прохождением синхронизирующего сигнала, от процессора 9 по синхронизирующему входу устройства возлагается на триггер 1, -а мультиплексор 11 настраивается на передачу к устройству памяти информации

от процессора 8.

.Второй триггер 2 и первый элемецт Р 3 обеспечивают установку триггера 2 в состояние 1 при условии прохождения синхронизирующего импульса через устройство 7 под управлением первого триггера 1, Появление потенциала 1 на выходе второго триггера 2 приводит к сбросу первого 1 и второ- .го.2 триггеров, при этом элемент задержки 5 обеспечивает сброс второго триггера 2 с задержкой, достаточной PfiH броса первого триггера 1 .

Если в начальный момент времени первьй триггер 1 находится в состоянии I, первый процессор 8 не может обратиться с. очередным запросом на обслуживание до тех пор, пока при отсутствии запроса от второго процессора 9 обработки через устройство 7 не пройдет синхронизирующий импульс, который задним фронтом сбросит первый триг гер 1

в состояние

НА

О. Сброс триггера 1 в О осуществляется посредством триггера 2 и элемента ИЗ., .

Установкой потенциала О на входе блокировки устройства 7 второй процессор 9. обеспечивает монопольное использование устройства памяти, при этом и мультиплексор 11 настраивается на пер.едачу информации от процессора 9.

Предлагаемое техническое решение обеспечивает- работу одного из про- шессоров с общей памятью с минималь- ной задержкой, что особенно важно, когда частота обращений этого процессора преобладает над частотой обращений другого. Б этом варианте задержка минимальна дпя второго- процессора и ее величина для стробирую- щих импульсов определяется быстродействием одного элемента И. Время регистрации запроса от первого процессора определяется временем срабатывания одного триггера. При совпадении во времени запросов двух процессоров работа первого процессора приостанавливается до тех пор, пока в работе второго процессора с устройством памяти не будет свободного временного окна. Если второй процессор выполнен с применением микропрограммирования, процент операцт выполняемых над данными без обращения к памяти достаточно велик я совмещения работы канала ввода-вывода и вычислительного устройства. При этом повышение быстродействия достигается за счет, более полного совмещения операций работы с памятью и перенесением блокировки на устройство, реже использующее память,. Наиболее эффективно применение устройс ва в специализированных системахi ориентированных на решение задач с определенным соотноше- нием процента вычислительных операций, использующих память и операций ,

3,

ввода вывода. Например, если известно, что все операции ввода-вывода можно завершить к нужному моменту, используя промежутки времрни, когда вычислительное устройство не обра- щается к памяти, ввод-вывод не будет з.адержйвать вычисления,

Формула изобретения

Устройство для сопряжения процес- сор ов с общим блоком памяти, содержащее два триггера и два элемента И, причем синхровход первого триггера подключен .к выходу запроса первого процессора, единичный выход первого триггера соединен с информационным входом второго триггера и подключен к входу блокировки первого пррцессо- ра, первый вход первого элемента И соединен с первым входом второго эле мента И и подключен к синхровыходу второго процессора, второй вход пер464. .

вого элемента И подключен к выходу блокировки второго процессора, выход второго элемента И подключен к синх- ровходу первого процессора и общего блока памяти, при этом информационный вход первого триггера подключен к шине единичного потенциала устройства, выход первого элемента II соединен с синхровходом второго триггера, отличающееся тем, что, с целью повьшения быстродействия, в него введены элемент И-НЕ и элемент задержки, причем второй вход второго элемента И соединен с выходом элемента И-НЕ, первьй и второй входы которого соединены соответственно с вторым входом первого элемента И и нулевым выходом первого триггера, нулевой вход которого соединен с входом элемента задержки и-выходом второго триггера нулевой вход которого со- ец лкен с выходом элемента задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРОЦЕССОРОВ С ОБЩИМ БЛОКОМ ПАМЯТИ | 1991 |

|

RU2006925C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1995 |

|

RU2094842C1 |

| Селекторный канал | 1983 |

|

SU1103218A1 |

| Устройство управления взаимным доступом процессора многопроцессорной системы | 1989 |

|

SU1631548A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ОПЕРАТИВНОЙ ПАМЯТЬЮ | 1992 |

|

RU2060538C1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство для сопряжения двух процессоров | 1990 |

|

SU1709325A1 |

| Устройство для ввода аналоговой информации | 1988 |

|

SU1501026A1 |

| Устройство для анализа частоты использования блоков информации в вычислительных комплексах | 1990 |

|

SU1793442A1 |

| Устройство для обращения двух процессоров к общему блоку памяти | 1990 |

|

SU1784986A1 |

Изобретение относится к вьгаисли- тельной технике и может быть применено в системах, в которых один блок памяти одновременно используется несколькими процессорами. Основной це- целью изобретения является увеличение быстродействия при работе двух процессоров с общим блоком памяти. Устройство содержит два триггера, два элемента И, элемент И-НЕ, элемент задержки. 2 ил. iNd 1Й. Од

Ptf.;

(Put. г

Составитель С.Пестмал Редактор Л.Пчелинская Техред О.Гортван Корректор Е.Сирохман

Заказ 3490/44 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раущская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| Патент США № 4240138, | |||

| кл | |||

| Устройство для сопряжения блоков обработки данных | 1980 |

|

SU993235A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-30—Публикация

1984-12-07—Подача