112

Изобретение относится к цифровой вычислительной технике, может быть использовано для построения арифметических устройств и является усовершенствованием изобретения по авт.св. № 581470.

Цель изобретения - расширение функциональных возможностей устройства, заключающееся в возможности вы

полнения операции вычитания.

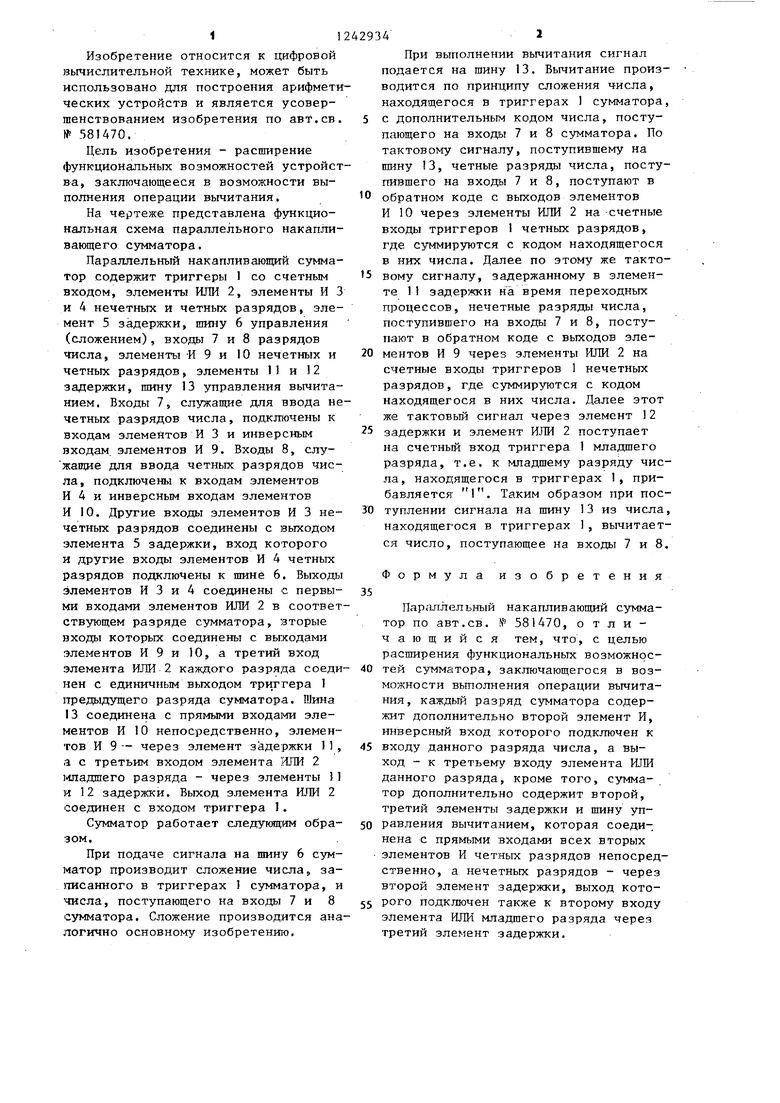

На чертеже представлена функциональная схема параллельного накапливающего cjT MaTopa.

Параллельный накапливающи й сумматор содержит триггеры 1 со счетным входом, элементы ИЛИ 2, элементы И 3 и 4 нечетных и четных разрядов, элемент 5 задержки, шину 6 управления (сложением), входы 7 и 8 разрядов числа, элементы И 9 и 10 нечетных и четных разрядов, элементы 11 и 12 задержки, шину 13 управления вычитанием. Входы 7, служащие для ввода нечетных разрядов числа, подключены к входам элементов И 3 и инверсным входам, элементов И 9. Входы 8, слу- жащие для ввода четных разрядов числа, подключены к входам элементов И 4 и инверсным входам элементов И 10, Другие входы элементов И 3 нечетных разрядов соединены с выходом элемента 5 задержки, вход которого и другие входы элементов И 4 четных разрядов подключены к шине 6. Выходы элементов И 3 и 4 соединены с первыми входами элементов ИЛИ 2 в соответствующем разряде сумматора, вторые входы которых соединены с выходами элементов И 9 и 10, а третий вход элемента ИЛИ 2 каждого разряда соединен с единичным выходом триггера 1 предыдущего разряда сумматора. Шина 13 соединена с прямыми входа1чи элементов И 10 непосредственно, элементов И 9 - через элемент задержки 11, а с третьим входом элемента ЛПИ 2 1чладшего разряда - через элементы 11 и 12 задержки. Выход элемента ИЛИ 2 соединен с входом триггера 1.

Сумматор работает следукщим образом.

При подаче сигнала на шину 6 сумматор производит сложение числа записанного в триггерах 1 сумматора, и числа, поступающего на входы 7 и 8 сумматора. Сложение производится аналогично основному изобретению.

При выполнении вычитания сигнал подается на шину 13. Вычитание производится по принципу сложения числа, находящегося в триггерах 1 сумматора,

с дополнительньпч кодом числа, поступающего на входы 7 и 8 сумматора. По тактовому сигналу, поступившему на шину 13, четные разряды числа, поступившего на входы 7 и 8, поступают в

обратном коде с выходов элементов И 10 через элементы ИЛИ 2 на -счетные входы триггеров 1 четных разрядов, где суммируются с кодом находящегося в них числа. Далее по этому же тактовому сигналу, задержанному в элементе 1I задержки на время переходных процессов, нечетные разряды числа, поступившего на входы 7 и 8, поступают в обратном коде с выходов элементов И 9 через элементы ИЛИ 2 на счетные входы триггеров 1 нечетных разрядов, где суммируются с кодом находящегося в них числа. Далее этот же TaKTOBbDi сигнал через элемент 12

задержки и элемент ИЛИ 2 поступает на счетный вход триггера 1 младшего разряда, т.е. к младшему разряду числа, находящегося в триггерах 1, прибавляется: 1. Таким образом при поступлении сигнала на шину 13 из числа, находящегося в триггерах 1, вычитается число, поступающее на входы 7 и 8.

Формула изобретения

Параллельный накапливающий сумматор по авт.св. № 581470, отличающийся тем, что, с целью расширения функциональных возможнрстей сумматора, заключающегося в возможности вьтолнения операции вычитания, каждый разряд сумматора содержит дополнительно второй элемент И, инверсный вход которого подключен к

входу данного разряда числа, а выход - к третьему входу элемента ИЛИ данного разряда, кроме того, сумматор дополнительно содержит второй, третий элементы задержки и шину управления вычитанием, которая соеди-,

нена с прямыми входами всех вторых элементов И четных разрядов непосредственно, а нечетных разрядов - через второй элемент задержки, выход которого подключен также к второму входу элемента ИЛИ младшего разряда через третий элемент задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования @ -разрядных последовательно поступающих чисел | 1982 |

|

SU1075260A1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2006 |

|

RU2308801C1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2278411C1 |

| Устройство для измерения суточного хода часов | 1988 |

|

SU1613998A1 |

| Делитель частоты следования импульсов | 1982 |

|

SU1045400A1 |

| ЦИФРОВОЕ УСТРОЙСТВО для ОПРЕДЕЛЕНИЯ ДИСПЕРСИИ ОРДИНАТ СЛУЧАЙНЫХ ПРОЦЕССОВ | 1973 |

|

SU369573A1 |

| Устройство для вычисления тангенса | 1984 |

|

SU1187162A1 |

| Устройство для вычисления квадрата числа | 1983 |

|

SU1115051A1 |

| Цифроаналоговый преобразователь | 1983 |

|

SU1152091A1 |

Изобретение относится к цифровой вычислительной технике, может быть использовано для построения арифметических устройств и является дополнительным к основному авт. св. № 581470. Целью изобретения является расширение функщунальных возможностей устройства, заключающееся в возможности вьтолнения операции вычитания. Поставленная цель достигается тем, что в каждый разряд сумматора дополнительно введен второй элемент И, инверсный вход которого подключен к входу данного разряда числа, а выход - к- третьему входу элемента ИЛИ данного разряда, кроме того, в сумматор также введены второй, третий элементы задержки и шина управления вычитанием, которая соединена с прямыми входами всех вторых элементов И четных.разрядов непосредственно, а нечетных разрядов - через второй элемент задержки, выход которого подключен также к второму входу элемента ИЛИ младшего разряда. I ил. i (Л ю и N9 09

Редактор Е.Папп

Составитель А.Клюев

Техред Н.Бонкало Корректор М.Пожо

3705/47

Тираж 6-71Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Параллельный накапливающий сумматор | 1975 |

|

SU581470A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-07—Публикация

1984-09-21—Подача