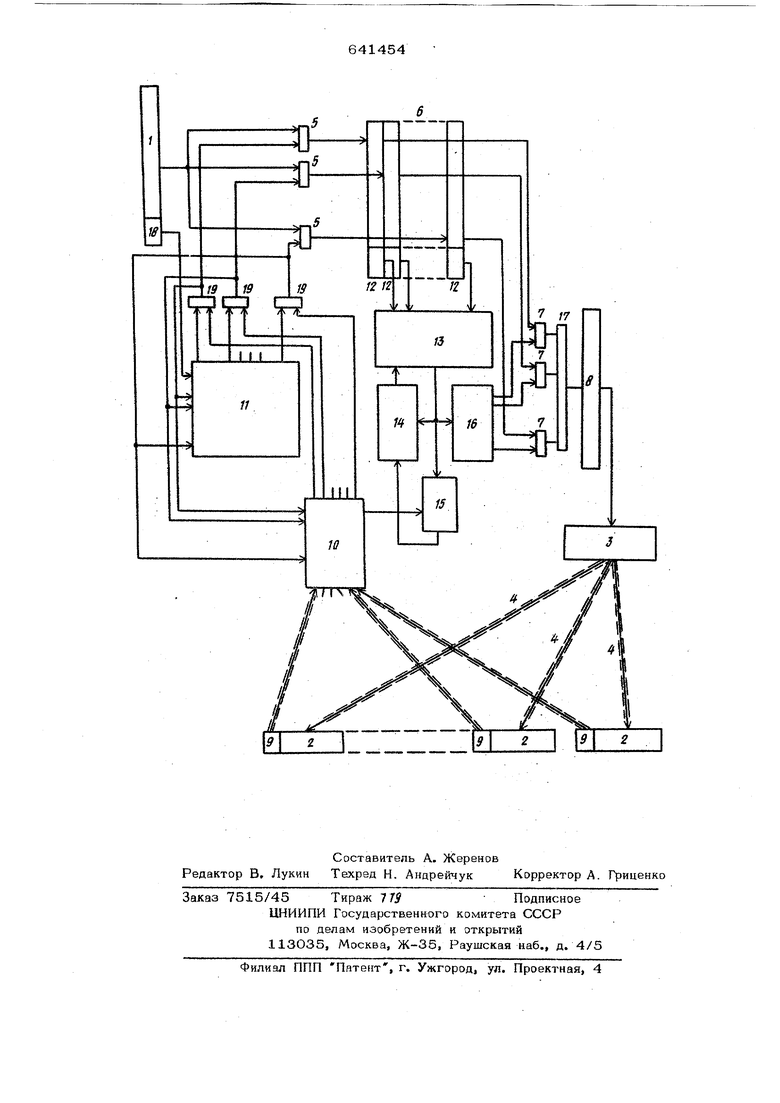

оШразцением в оперативную память, которое содержит регистр обращения к памяти, узлы ответа, адресные регистры, вхоцы которых подключены к выходу коммутатора r2;j. В таком устройстве применены счетчи ки цикла памяти, и очередное обращение не может поступить на выходной регистр, пока счетчик необходимого для него блока .высчитывает цикл,, т.е. блок занят. Каждый новый запрос, поступивший на выходной регистр, занимает соответствующий блок ОП и запускает его счетчик цикла. Адрес очередного обращения к ОП от одного из запцосчиков: буфера операндов, буфера команд или буфера записи в соответствии с приоритетом и при условии свободы соответствующего блока ОП поступает на регистр обращения к ОП и с него на регистр адреса одного из блоков ОПо При этом запускается соответствуюХИИЙ этому блоку счетчик цикла, блокирую щий обращение к данному блоку до конца его работы. Если имеются обращения к другим блокам ОП, которые в это времясвободны, то они проходят на регистр обращения к ОП и с него на свои блоки, запуская соответствую:щие счетчики цикла При такой организации всегда известно, по состоянию счетчиков, какие блоки ОП заняты, и адрес очередного обращения может поступить на регистр обращения только при условии свободы необходимого ему блока ОП.Поэтому, если адрес обра адения поступил на регистр обращения, то обязательно через строго фиксированный промежуток времени запрос на обращение будет удовлетворен. Однако подобное решение снижает пропускную способнос.ъ канала связи процес сора с ОП и степень использования обору дования оперативной памяти. Целью изобретения является увеличение пропускной способности и повышение эффективности использования оборудования Поставленная цель достигается тем, что в устройство введены блоки хранения оче реди запросов, хранения таблицы занятости, приоритетного выбора запросов, формирования запросов, управления приемом запросов, дешифратор, узел сдвига, регистр выдачи, группы элементов И, элемент ИЛИ, причем первый выход регистра обращения к памяти подключен к входам первой группы элементов И, ко вторым .входам которых подключены соответственно выходы элементов И второй группы, выходы элементов И первой группы соединены со входом блока хранения очереди запросов, первый выход которого через последовательно соединенные третью группу элементов И, элемент ИЛИ и регистр выдачи подключен к входу коммутатора, второй выход блока хранения очереди запросов, подключен к первому входу блока формирования запросов, второй вход которого соединен с вь1ходом блока хранения таблицы занятости, а выход подключен ко входу дешифратора и кпервым входам узла сдвига и блока хранения таблицы Занятости, второй вход которого соединен с выходом узла сдвига, второй вход узла сдвига подключен к первому выходу 6Jioka управления приемом запросов, второй выход которого подключен к первым входам элементов И второй группы, вторые входы которых соединены соответственно с выходами блока приоритетного выбора запросов, а выходы - подключены к первым входам блока приоритетного выбора запросов и блока управления приемом запросов, вторые входы которых соединены соответственно со вторым выходом регистра обращения к памяти и с выходами узлов ответа, выход дешифратора соединен с соответствующими входами элементов И третьей группы. Схема устройства представлена на чертеже, где обозначено: регистр обращения к памяти 1; адресные регистры 2; группа элементов И для вьщачи кода адреса обращения в ОП 3; кабели связи процессора с ОП 4j группа элем -нтов И для приема кода в буфер запросов 5; блок хранения очереди запросов 6j группа элементов И для приема на регистр выдачи 7; регистр вьщачи 8; узлы ответа о приеме запроса на обслуживание в блок ОП 9; блок управления приемом запросов 10; блок приоритетного выбора запросов 11; группы разрядов 12 регистров блока 6, указывающие номер блока ОП, к которому должно быть обращение от данного запроса, блок формирования запроса 13; блок хранения таблицы занятости 14; узел сдвига 15j дешифратор 16; элемент ИЛИ 17; группа разрядов 18 регистра 1, характеризук щая тип обращения к ОП; группа элементов И 19 для выработки сигнала управления приемом в регистры блока 6. Работает .устройство следующим образом. Код адреса очередного запроса к ОП с регистра 1 поступает на один из регистров блока хранения очереди запросов 6. Определение регистра, на которой осуществляется прием очередного запроса, производится на основе анализа типа обращения, определяемого, кодом группы разрядов регистра 1, состоянием блока 11 и состоянием блока 1О, Запросы, принятые на регистры блока б поступают на блок 13, формирующий на основанш; приоритетов запросов и лосостоянию блоков ОП, занятым ранее данным процессором запрос к ОП, что определяется таблицей бло ка 14. Этот запрос через дешифратор 16 группу элементов И 7 и элемент ИЛИ 17 подключает к регистру 8 один из регистров блока 6 хранения очереди запросов, определяемый блоком 13. Одновременно устанавливают в I. триггер занятости блока ОП, к которому адресован запрос, а номер блока ОП пост тупает на вход временного имитатора обращения к ОП, который связан со входам установки в О всех триггеров блока 14 хранения таблицы занятости. Код на регистре 8 выдерживается минимальное время, необходимое для его приема в блок ОП при, условии его свободы, затем на регистр 8 выставляется следующий по приоритету запрос, мированный блоком 13. Если через строго фиксированное время от блока ОП не поступает ответа о принятии запроса, выставленного на регистр 8, такой запрос считается неудовлетворительным, триггер занятости его блока, установленный ранее в 1, устанавливается узлом 15 в О, запрос формируется снова блоком 13 и процесс повторяется. Если запрос на обращение принят блоком ОП, т.е. через фиксированное время после выдачи его на регистр 1 от блока ОП из узла 9 приходит подтверждение о его исполнении, то по истечении цикла ОП узел 15 осушест,вляет сброс триггера таблицы блока 14, соответствующего данному блоку ОП. Кро ме того, по сигналу от узла 9 через блок 10 осуществляется освобождение регист- ра блока 6, обращение которого находится в стадии исполнения блоком ОП. Таким образом, каждое обращение, периодически поступает на шины обращения к ОП, занимая и.х и регистр 8 на короткое время, до тах пор, пока не окажет ся свободным блок ОП. Формула изобретения Устройство для управления обращением в оперативную память, содер кащее регистр обращения к памяти, узлы ответа. адресные регистры, входы которых подключены к выходу коммутатора, отличающееся тем, что, с целью увеличения пропускной способности и повышения эффективности использования оборудования, в него введены блоки .хранения очереди запросов, .хранения таблицы занятости, приоритетного выбора запросов, формирования запросов, управления приемом запросов, дeшифpaтopt узел сдвига, регистр выдачи, группы элеэлементов И, элемент ИЛИ, причем первый выход регистра.обращения к памяти подключен к первым входам первой группы элементов И, ко вторым входам которых подключены соответственно вы.ходы элементов И второй группы, .ходы элементов И первой группы соединены со входами блока .хранения очере- пи запросов, первый выход которого через последовательно соединенные третью группу элементов И, элемент ИЛИ и ре:Г 1Стр .выдачи подключен ко аходу коммутатора, второй вьрсод блока хранения очереди запросов подключен к первому входу блока формирования запросов, второй вход которого соединен с выходом блока хранения таблшда занятости, а ход по.цключен ко аходу дешифратора и к первым входам узла сдвига и блока хранения таблицы занятости, второй вход которого соединен с выходом узла сдвига, второй вход узла сдвига подключен к первому выходу блока управления приемом запросов, второй выход которого подключен к первым входам элементов И второй группы, вторые аходы которых соединены соответственно с выходами блока приоритетного выбора запросов, а выходы подключены к первым входам блока приоритетвого выбора запросов и блока управления приемом запросов вторые входы которых соединеш:. соотБетс1 венно со вторым выходом регистра обращения к памяти и с выходами узлов от вета, выход дешифратора соединен с соответствуюшнми входами элементов И третьей группы. Источники информации, принятые во внимание при экспертизе; 1.Патент США № 3905023, кл. 340-172.6, 235-153 АР, кло G06 F 11/06; G06 F 15/16, 1975. 2.Королев Л. Н. Структуры ЭВМ и ях математическое обеспечение, ДА., Наука-, 1974, с. 72-76.

2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1987 |

|

SU1587521A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Процессор ввода-вывода | 1980 |

|

SU934465A1 |

| Устройство для сопряжения каналов ввода-вывода с устройством управления оперативной памятью | 1984 |

|

SU1265788A1 |

| Устройство управления обменом | 1977 |

|

SU771655A1 |

| Устройство для выбора и переадресации каналов | 1986 |

|

SU1390820A1 |

| Система доступа к памяти | 1983 |

|

SU1151974A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

Авторы

Даты

1979-01-05—Публикация

1976-08-13—Подача