«Дождь. Для этого счетчик адресов дол}кен быть организован как счетчнк но модулю и связан со схемамн нмпликацин вместо счетчиков адресов.

Изменением связей между входами и выходами счетчика циклов можно нолучить п различных динамических тестов тина «Дождь. При фиксации счетчика циклов можно иолучить 2 различных статических тестов.

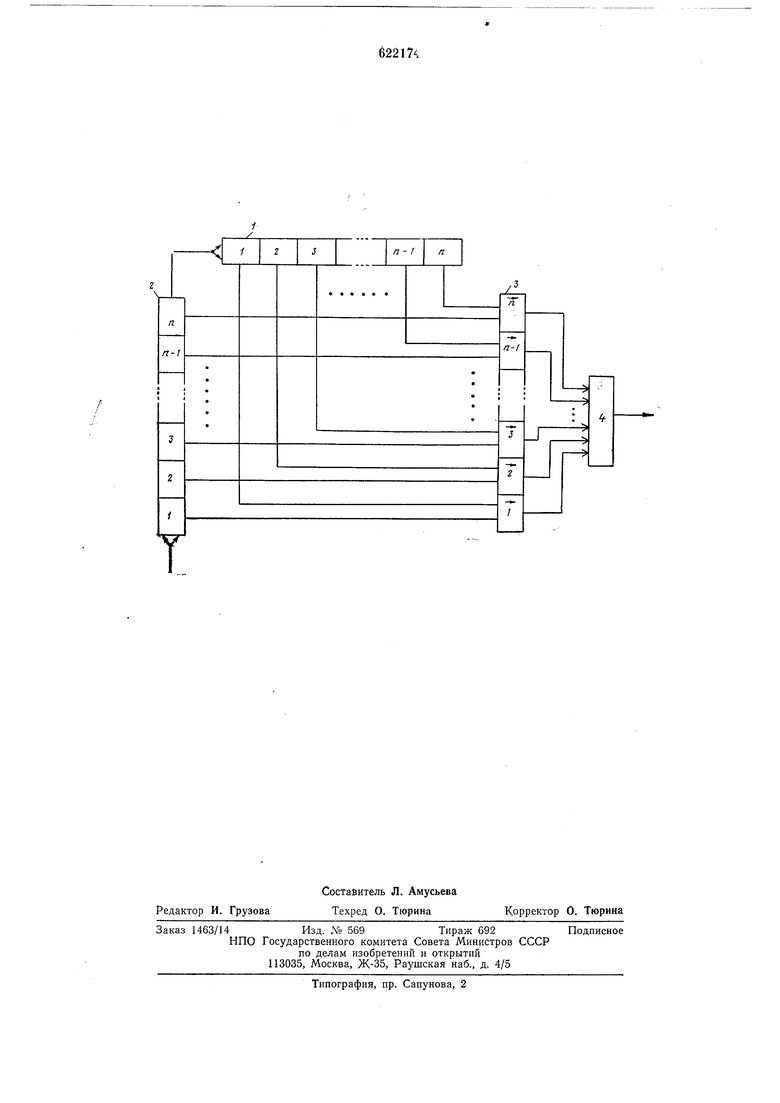

Устройство работает следующим образом.

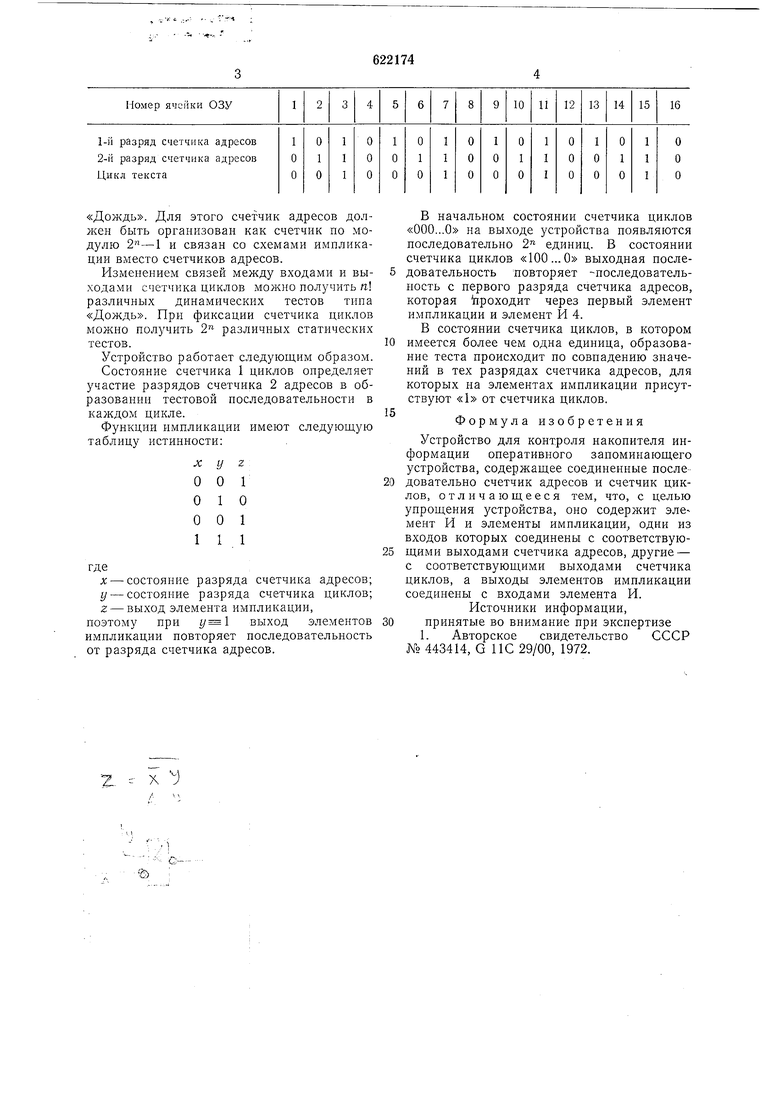

Состояние счетчика 1 циклов определяет участие разрядов счетчика 2 адресов в образовании тестовой носледовательностн в каждом цикле.

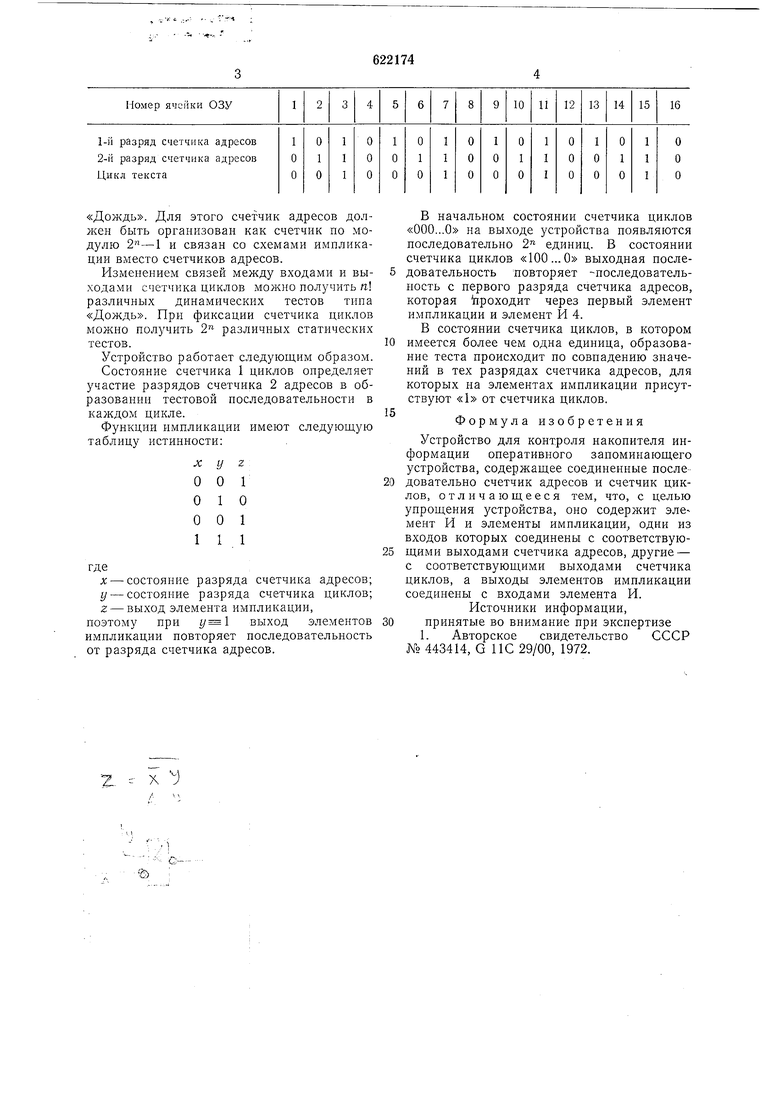

Функции импликации имеют следующую таблицу истинности:

X у Z 001 О 1 о

0о 1

11.1

где

X - состояние разряда счетчика адресов;

у - состояние разряда счетчика циклов;

Z - выход элемента имнликации, поэтому при выход элементов имнликации повторяет последовательность от разряда счетчика адресов.

В начальном состоянии счетчика циклов «000...О на выходе устройства ноявляются последовательно 2 единиц. В состоянии счетчика циклов «100 ...О выходная последовательность повторяет -последовательность с нервого разряда счетчика адресов, которая проходит через первый элемент импликации и элемент И 4.

В состоянии счетчика циклов, в котором имеется более чем одна единица, образование теста происходит по совпадению значений в тех разрядах счетчика адресов, для которых на элементах импликации присутствуют «Ь от счетчика циклов.

Формула изобретения

Устройство для контроля накопителя информации оперативного запоминающего устройства, содержащее соединенные после

довательно счетчик адресов и счетчик циклов, отличающееся тем, что, с целью унрощения устройства, оно содержит эле мент И и элементы импликации, одни из входов которых соединены с соответствующими выходами счетчика адресов, другие - с соответствующими выходами счетчика циклов, а выходы элементов импликации соединены с входами элемента И. Источники информации,

принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 443414, G ПС 29/00, 1972.

п - п

| название | год | авторы | номер документа |

|---|---|---|---|

| Датчик кодов для устройства контроля запоминающих блоков | 1974 |

|

SU521608A1 |

| Устройство для контроля полупроводниковой оперативной памяти | 1981 |

|

SU991516A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1022225A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1001182A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| Устройство таймеров | 1983 |

|

SU1163309A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Запоминающее устройство с тестовым самоконтролем | 1988 |

|

SU1695394A1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU955210A1 |

п-1

гг-1

Авторы

Даты

1978-08-30—Публикация

1976-12-14—Подача