Изобретение относится к металлообрабатывающей -технике и может быть ис- пользовагю в станках с числовым программным управлением для регулирола- ия нанряжения нитания. ,

Цель изобретения - повьцнение точности и быстродействия.

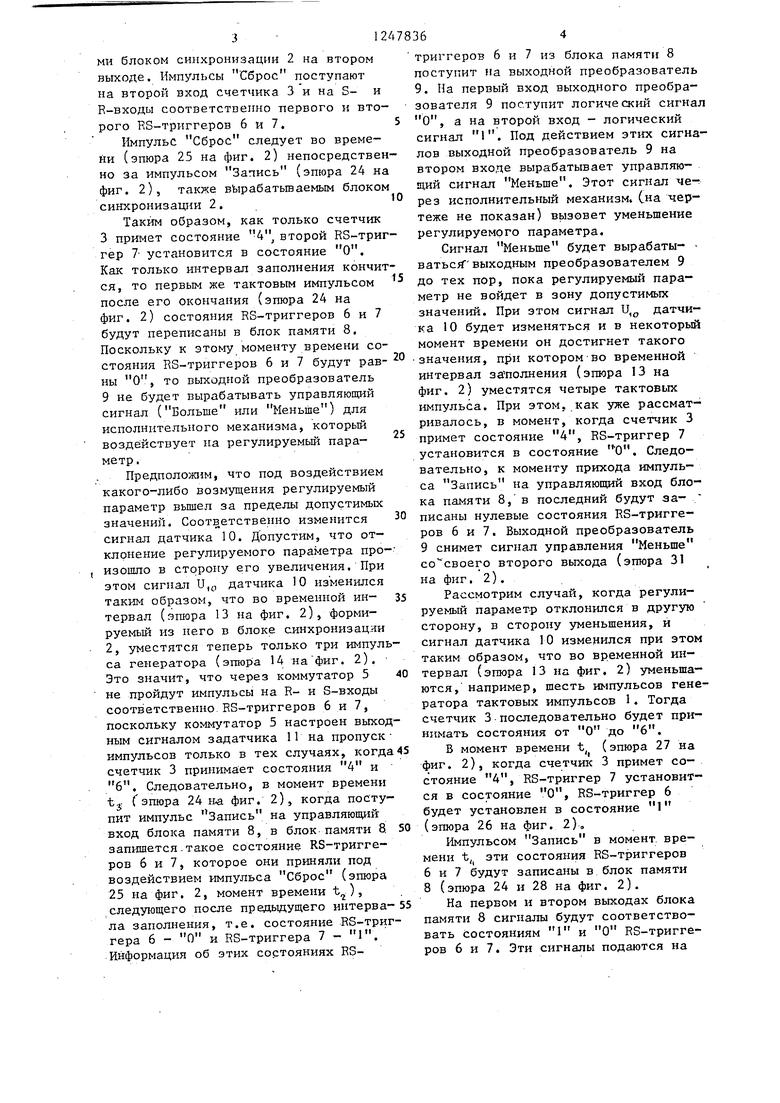

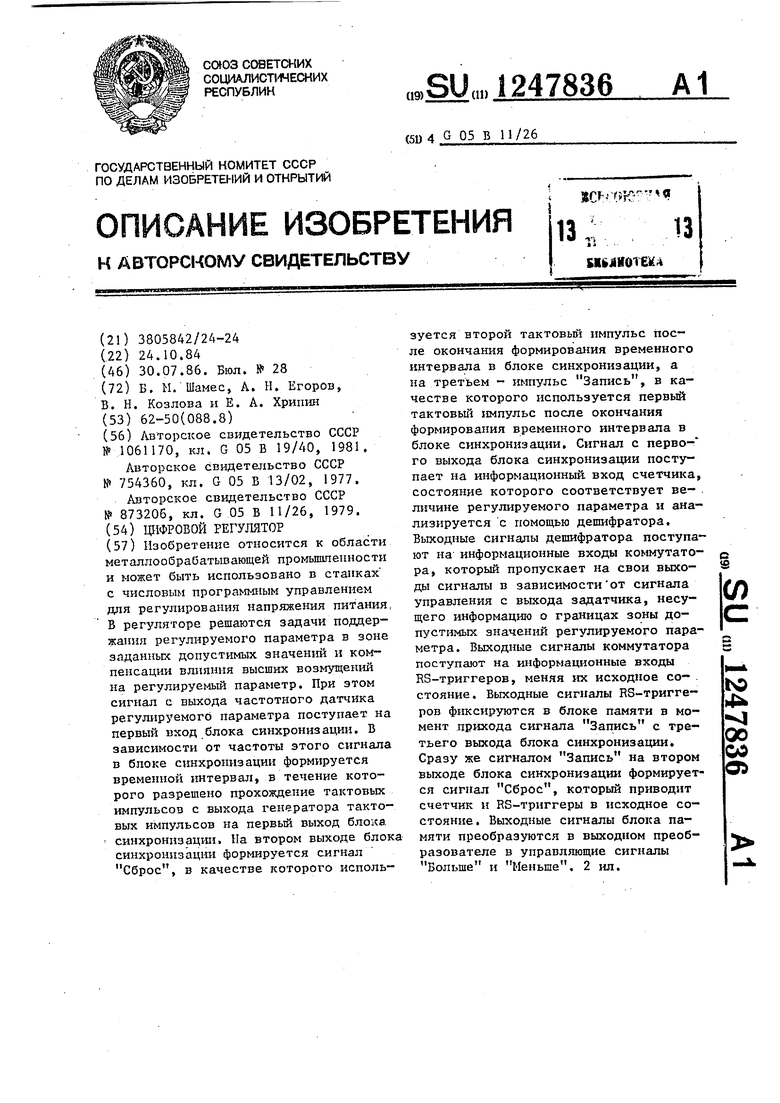

Па фиг, .1 представлена структурная схема регулятора; на фиг. 2 - энюры сигналов, характеризующие работу регулятора . , ;:

Цифровой регулятор.содержит генератор тактовых импульсов I, блок синхронизации 2,, счетчик 3, дешифратор 4, коммутатор 5, первый и второй КЗ-тр.нггеры 6 и 7, блок памяти 8, выходной нреобразователь 9, датчик Ю, зада1 Ч1пс i 1 .

На фиг, 2 введены обозначения: эпюры 12-31 .сигналов, и. - сигнал на ,)--ом выходе i-oro блока, Ц выходной сигнал i-oro блока.

Регулятор работает следующим образом, :

Генератор 1 генерирует ненрерыв- иуга п.оследовательность импульсов (эпюр 12 на фиг. 2.), которая поступает на второй вход блока синхронизации 2. На первый вход блока синхронизации 2 поступает выходной сигнал датчика 10 (обратной связи). Частота выходного сигнала датчика 10 зависит от величи 1 ы регулируемого параметра, В блоке С1и1кропизации 2 из сигнала U|y датчи- 1-:а 10 вырабатывается временной интервал (эпюра 13 па фиг. 2) и заполняется импульсами U., генератора тактовых мпульсов (зпюра 14 на фиг, 2), Эти шпгульсы с первого выхода блока син- хропизации-2 поступают на первый вход счетчика 3,

Рассмотрим частный случай трехраз- рядпого счетчика 3. С выходов счетчика 3 импульсы (.эпюры 15-17 на фиг, 2 поступают па входы дешифратора 4, а с выходов дeIШiфpaтopa 4 импульсы (эпюры 18-23. на фиг. 2) поступают на информационный вход коммутатора 5. Коммутатор 5 пропускает на своп выходы импульсы только от определенных, заранее выбранных выходов дешифратора 4, Этот выбор осуществляется ycTanoBKoii коммутатора по управляющему входу, исходя из заданных верхПй11 и нижней. 1фаниц зоны допусти {ых значений регулируемого нараметр а, информация о которых содержится в вызсэдпом сигнале U, задатчика . I 1 .

0

Пусть эта зона будет такова, что нижней ее границе соответствует заполнение временного интервала (эпюра 13 на фиг. 2) пятью импульсами

генератора 1 тактовых импульсов, верхней - четырьмя импульсами (эпюра 14 на фиг, 2), В соответствии с этим производится установка коммутатора 5 таким образом, чтобы он пропускал импульсы только с тех выходов дешифратора 4, которые соответствзпот состояниям 4 и 6 счетчика 3.

PaccMOTpiiM случай, когда регулируемый параметр находится в зоне

допустимых значений (в.допуске). Тогда временной интервал (эпюра 12 на фиг 2), формируемый из сигнала датчика 10, будет TaKiiM, что в него уместятся четыре или пять импульсов

генератора тактовых импульсов 1. Пусть их, например, будет четыре (эпюра 14 па фиг. 2), Эти импульсы поступают па счетчик 3, и оп последовательно принимает состояния от

О до 4.

В момент, когда счетчик 3 примет состояпия 4, дешифратор 4 выделит это состояние. Коммутатор 5 пропустит импульс, соответствующий этоьгу

0 значению, на второго RS-триг- гера 7. Этим импульсом второй RS- триггер 7 установится в состояние О, ИсхО|Цное состояние второго RS-триггера 7 - I. Сигнал с выхода

5 второго RS-триггера 7 подается на второй информационный вход блока памяти 8. Первый же импульс (момент t, эпюра 24 на фиг. 2) генератора тактовых импульсов 1 после окончания

0 временного интервала (эпюра 13 на фиг, 2) с третьего выхода блока синхронизации 2 подается в качестве импульса Запись на управляющий вход блока памяти 8. Этим 1-1мнульсом состо45 яния RS- триггеров 6 и 7 записываются в блок памяти В, Исходные состояния первого ВВ-триггера 6 - О, второго RS-триггера 7 - 1, Б эти состояния они устанавливаются после каждого

50 очередного временного интервала заполнения (эпюра 13 па фиг, 2) или, что то же самое, перед началом каж- . дого следующего интервала заполнения. Эта установка RS-триггеров 6 и 7 в

55 исходное состояние и одновременно с этим сброс счетчика 3 в нулевое состояние осуществляется импульсами (эпюра 25 на фиг. 2), вырабатываемыми блоком синхронизации 2 на втором выходе. Импульсы Сброс поступают на второй вход счетчика 3 и на S- и R-входы соответственно первого и второго RS-триггеров 6 и 7.

Импульс Сброс следует во времени (эпюра 25 на фиг. 2) непосредственно за импульсом Запись (эпюра 24 на фиг. 2), также вЫрабатьшаемьш блоком синхронизации 2.

Таким образом, как только счетчик 3 примет состояние 4, второй RS-триг- гер 7- установится в состояние О. Как

ся,

только интервал заполнения кончит- то первым же тактовым импульсом

после его окончания (эпюра 24 на фиг. 2) состояния RS-триггеров 6 и будут переписаны в блок памяти 8. Поскольку к этому моменту времени сотриггеров 6 и 7 из блока памяти 8 поступит на выходной преобразовател 9. На первый вход выходного преобра зователя 9 поступит логический сигн О, а на второй вход - логический сигнал 1. Под действием этих сигн лов выходной преобразователь 9 на втором входе вырабатывает управляющий сигнал Меньше. Этот сигнал че рез исполнительный механизм Сна чер теже не показан) вызовет уменьшение регулируемого параметра.

Сигнал Меньше будет вырабаты- ватьсй выходным преобразователем 9 до тех пор, пока регулируемый параметр не войдет в зону допустимых значений. При этом сигнал U,;, датчи ка 10 будет изменяться и в некоторы момент времени он достигнет такого

10

стояния RS-триггеров 6 и 7 будут -значения, при котором-во временной

интервал за полнения (эпюра 13 на фиг. 2) уместятся четыре тактовых импульса. При этом, как уже рассмат ривалось, в момент, когда счетчик 3 примет состояние 4, RS-триггер 7 установится в состояние О. Следовательно, к моменту прихода импульса Запись на управляющий вход бло ка памяти 8, в последний будут за- писаны нулевые состояния RS-триггеров 6 и 7. Выходной преобразователь 9 снимет сигнал управления Меньше со своего второго выхода (эшора 31 на фиг, 2).

ны О, то выходной преобразователь 9 не будет вырабатывать управляющий сигнал (Больше или Меньше) для исполнительного механизма, который воздействует на регулируемьш параметр.

Предположим, что под воздействием какого-либо возмущения регулируемый параметр вьш1ел за пределы допустимых значений. Соответственно изменится сигнал датчика 10. Допустим, что отклонение регулируемого параметра произошло в сторону его увеличения. При этом сигнал U,;, датчика 10 изменился таким образом, что во временной интервал (эпюра 13 на фиг. 2), формируемый из него в блоке синхронизации 2, уместятся теперь только три импулса генератора (эпюра 14 на фиг. 2). Это значит, что через коммутатор 5 не пройдут импульсы на R- и S-входы соответственно RS-триггеров 6 и 7, поскольку коммутатор 5 настроен выходным сигналом задатчика 11 на пропуск импульсов только в тех случаях, когд

3 принимает состояния 4 и Следовательно, в момент времени tj { эпюра 24 Ни фиг. 2), когда поступит импульс Запись на управляющий вход блока памяти 8, в блок памяти 8 запишется.такое состояние RS-триггеров 6 и 7, которое они приняли под воздействием импульса Сброс (эпюра 25 на фиг. 2, момент времени t), следующего после предьщущего интервала заполнения, т.е. состояние RS-триг гера 6 - О и RS-триггера 7 - 1. .Информация об этих состояниях RSсчетчикл

78364

триггеров 6 и 7 из блока памяти 8 поступит на выходной преобразователь 9. На первый вход выходного преобразователя 9 поступит логический сигнал О, а на второй вход - логический сигнал 1. Под действием этих сигналов выходной преобразователь 9 на втором входе вырабатывает управляющий сигнал Меньше. Этот сигнал че-; рез исполнительный механизм Сна чертеже не показан) вызовет уменьшение регулируемого параметра.

Сигнал Меньше будет вырабаты- - ватьсй выходным преобразователем 9 до тех пор, пока регулируемый параметр не войдет в зону допустимых значений. При этом сигнал U,;, датчика 10 будет изменяться и в некоторый момент времени он достигнет такого

0

-значения, при котором-во временной

интервал за полнения (эпюра 13 на фиг. 2) уместятся четыре тактовых импульса. При этом, как уже рассматривалось, в момент, когда счетчик 3 примет состояние 4, RS-триггер 7 установится в состояние О. Следовательно, к моменту прихода импульса Запись на управляющий вход блока памяти 8, в последний будут за- писаны нулевые состояния RS-триггеров 6 и 7. Выходной преобразователь 9 снимет сигнал управления Меньше со своего второго выхода (эшора 31 на фиг, 2).

Рассмотрим случай, когда регулируемый парамет-р отклонился в другую сторону, в сторону уменьшения, и сигнал датчика 10 изменился при этом таким образом, что во временной интервал (эпюра 13 на фиг. 2) уменьшаются, например, шесть импульсов генератора тактовых импульсов 1. Тогда счетчик 3 последовательно будет принимать состояния от О до 6.

В момент времени t, (эпюра 27 на фиг. 2), когда счетчик 3 примет состояние 4, RS-триггер 7 установится в состояние О, RS-триггер 6 будет установлен в состояние 1 (эпюра 26 на фиг. 2),

Импульсом Запись в момент, времени t, эти состояния RS-триггеров 6 и 7 будут записаны в блок памяти 8 (эпюра 24 и 28 на фиг. 2).

На первом и втором выходах блока памяти 8 сигналы будут соответствовать Состояниям 1 и О RS-триггеров 6 и 7. Эти сигналы подаются на

itepHbii i н второй входы выходного преобразователя 9, Выходной преобразователь 9 под воздействием этих сигналов вырабатьшае т на своем пер- )зом выходе сигнал Больше (эпюра 30 на фиг. 2). Этот сигнал будет присутствовать до тех пор, пока регулируемый параь5етр не войдет в зону допустимых значений. Это произойдет тогда, когда сигнал U,o датчика 10 будет таким3 что во временной интервал (эпюра 13 на фиг. 2) уместятся пять импульсов (шш четыре). Бри этом не Наступи-г состояние счетчика 3, равное 6, м RS-триггер б ке установится в состояние 1.

К моменту оче.редного имиульса Запись (эпюра 24 на фиг. 2, момент времени t,) состояния Р8.триггеров б и 7 будут Пулевые, н, следовательно, выходной преобразователь 9 снимет со своего первого выхода сигнал Больше (эпюра 30 на фгич 2).

В качестве генератора 1 может быт использовал кварцевый генератор.

ГГервый и второй RS-триггерЫ-б и 7 могут быть BunoJHieia i, например, на микросхеме 564Т.Р2.

Блок памяти 8 может быть выпол- leiij например, на микросхеме 564Т1 12,

Дешифратор 4 может быть выполнен, например. На микросхеме 564ПЛ1.

Блок синхронизации 2 представляет собой устройство, состоящее из инвер- тора, выполненного, например, на микросхеме 564ЛП2, на вход которого подается сигн,ал и,,с, 5 а выход которого соединеп с первьп-га входами первого н второго элементов 2Н, выполненных, например, на микросхемах 564JIA7. Иа вторые входы элементов 2И поступают сигналы с выходов дешифратора-сче - чнка, на выходы которого лостунает

фив. 1

0

5

0

5

0

5

0

сигнал и, с выхода генератора тактовых импульсов, в качестве дешифратора-счетчика может быть использована микросхема . 564ИЕ9.

Счетчик 3 представляет собой дво- ично-десятичньй счетчик, выполненный например, на микросхеме 564ИЕ14,

Выходной преобразователь 9 может быть реализован, например, на микросхеме 564ЛУ4.

( ормула изобретения

Цифровой регулятор, содержащий выходной преобразователь, блок памяти, задатчик, коммутатор И-датчик, соеди- пеппый выходом с первым, входом блока синхронизации, подключенного вторым входом к выходу генерато ра тактовых импульсов, а первым и вторым выходами - к первому и второму входам счетчика, соединенного выходом с входом дешифратора, .отличающий- с я тем, что, с целью повышения точ- ност-и и быстродействия регулятора, в нем дополнительно установлены первый и второй КЗ-триггеры, причем выход задатчика соедннеп с управляюиц м входом коммутатора, подключеппого информационным входом к выходу дешифратора, нервым выходом - к S-входу первого RS-триггера, а вторым выходом - к Н-входу второго RS-триггера, R-вход первого RS-триггера и В-вход второго RS-триггера соединены с вторым выходом блока синхронизации, выходы первого и второго RS-триггеров подклю- чепы к первому и второму информа- ционным входам блока памяти, соеди- нениого управляющим входом с третьим выходом блока синхронизации, а первым и вторым выходами - с первым и вторым входами выходного преобразователя .

болше

fiSHbuje

Составитель Ю, Гладков Редактор И. Сегляник Техред;В.Кадар Корректор В. Бутяга

4124/47

Тираж 836 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Прое ктная, 4

сриг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство для приема дискретной информации | 1989 |

|

SU1693735A1 |

| Устройство для программного управления | 1981 |

|

SU976428A1 |

| Система управления многопозиционной индукционной нагревательной установкой | 1983 |

|

SU1121789A1 |

| Устройство для ввода-вывода полутоновой информации | 1984 |

|

SU1164717A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Синхронный фильтр | 1988 |

|

SU1644366A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2004 |

|

RU2281549C1 |

| Многотактное микропрограммное устройство управления | 1986 |

|

SU1332318A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

Изобретение относится к области металлообрабатывающей промьполеиности и может быть использовано в станках с числовым программным управлением для регулирования напряжения питания, В регуляторе решаются задачи поддержания регулируемого параметра в зоне заданных допустимых значений н компенсации влияния высших возмущений на регулируемый параметр. При этом сигнал с выхода частотного датчика регулируемого параметра поступает на первый вход блока синхронизации. В зависимости от частоты этого сигнала в блоке синхронизации формируется временной интервал, в течение которого разрешено прохождение тактовых импульсов с выхода генератора тактовых импульсов на первьй выход блока синхронизации. На втором выходе блока синхронизации формируется сигнал Сброс, в качестве которого используется второй тактовьй импульс после окончания формирования временного интервала в блоке синхронизации, а на третьем - импульс Запись, в качестве которого используется первьй тактовьй импульс после окончания формирования временного интервала в блоке синхронизации. Сигнал с перво- го выхода блока синхронизации поступает на информационный, вход счетчика, состояние которого соответствует ве- . личине регулируемого параметра и анализируется с помощью дешифратора. Выходные сигналы дешифратора поступают на информационные входы коммутатора, который пропускает на свои выходы сигналы в зависимости от сигнала управления с выхода задатчика, несущего информацию о границах зоны допустимых значений регулируемого параметра. Выходные сигналы коммутатора поступают на информационные входы RS-триггеров, меняя их исходное состояние. Вьпсодные сигналы RS-триггеров фиксируются в блоке памяти в момент прихода сигнала Запись с третьего выхода блока синхронизации Сразу же сигналом Запись на втором выходе блока синхронизации формируется сигнал Сброс, который приводит счетчик и RS-триггеры в исходное состояние . Выходные сигналы блока памяти преобразуются в выходном преобразователе в управляющие сигналы Больше и Меньше. 2 нл. i О) to 4 к 00 оо О:

| Адаптивный коммутатор | 1982 |

|

SU1061170A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Авторское свидетельство СССР № 754360, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Цифровой регулятор | 1979 |

|

SU873206A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-07-30—Публикация

1984-10-24—Подача