bi

О5 0

со

Јь

31566341

анализа, блок 39 начальной установки. При этом блок управления снабжен узлом совпадения, элементом задержки,

а блок согласования - двумя коммутаторами, двумя регистрами и триггером. 7 ил,, 2 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметический расширитель | 1989 |

|

SU1661758A1 |

| Устройство для умножения | 1987 |

|

SU1472899A1 |

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU940155A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

| УСТРОЙСТВО СОВМЕСТНОГО КОДИРОВАНИЯ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ | 2012 |

|

RU2497180C1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство кадровой синхронизации | 1989 |

|

SU1817084A1 |

| Устройство для вычисления тригонометрических функций | 1980 |

|

SU928348A1 |

Изобретение относится к вычислительной технике, в частности к вычислительным системам со знакоразрядным кодированием информации, и может быть использовано в управляющих, моделирующих и вычислительных комплексах в качестве сопроцессора. Цель изобретения - расширение функциональных возможностей арифметического расширителя в части обеспечения выполнения операции деления. В арифметический расширитель, содержащий N K-разрядных вычислительных модулей 1, блок 2 управления, блоки 3, 4 управления первым и вторым параллельными сумматорами, блок 5 согласования, введены блоки 37, 38 анализа, блок 39 начальной установки, При этом блок управления снабжен узлом совпадения, элементом задержки, а блок согласования - двумя коммутаторами, двумя регистрами и триггером. 7 ил., 2 табл.

Изобретение относится к цифровой вычислительной технике, в частности к вычислительным системам со знако- разрядным кодированием информации, и может быть использовано в управляющих, моделирующих и вычислительных машинах в качестве сопроцессора

Цель изобретения - расширение функциональных возможностей арифметического расширителя в части обеспечения операции деления.

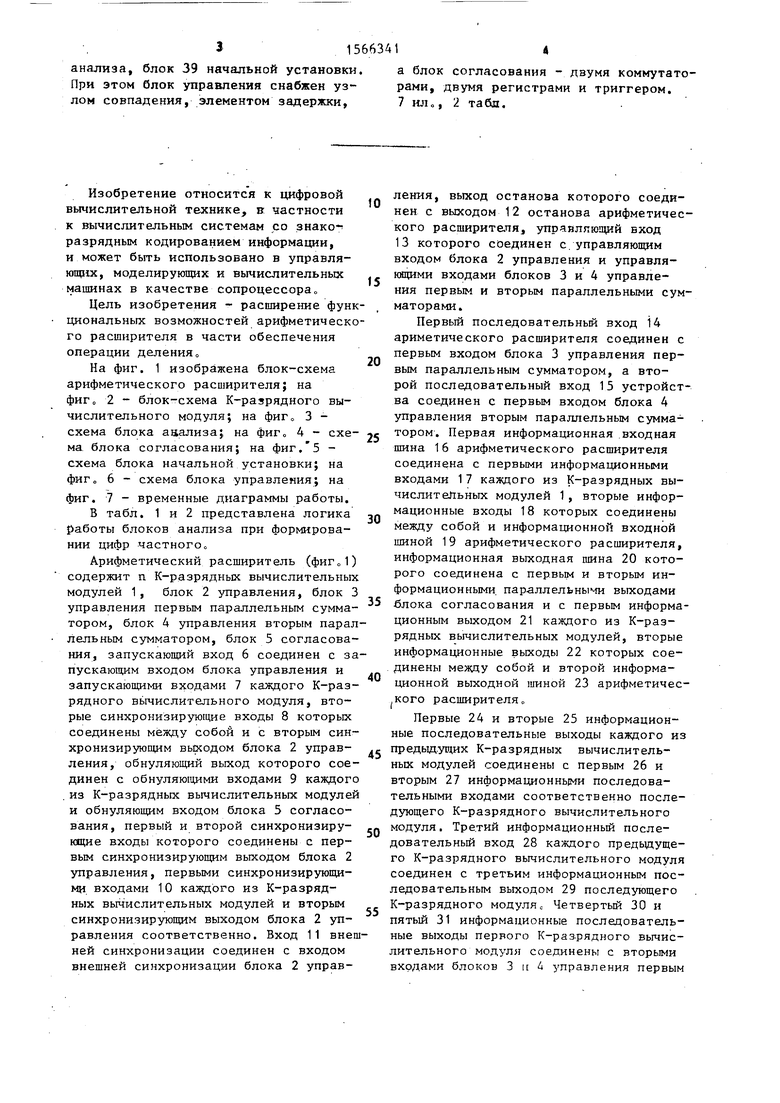

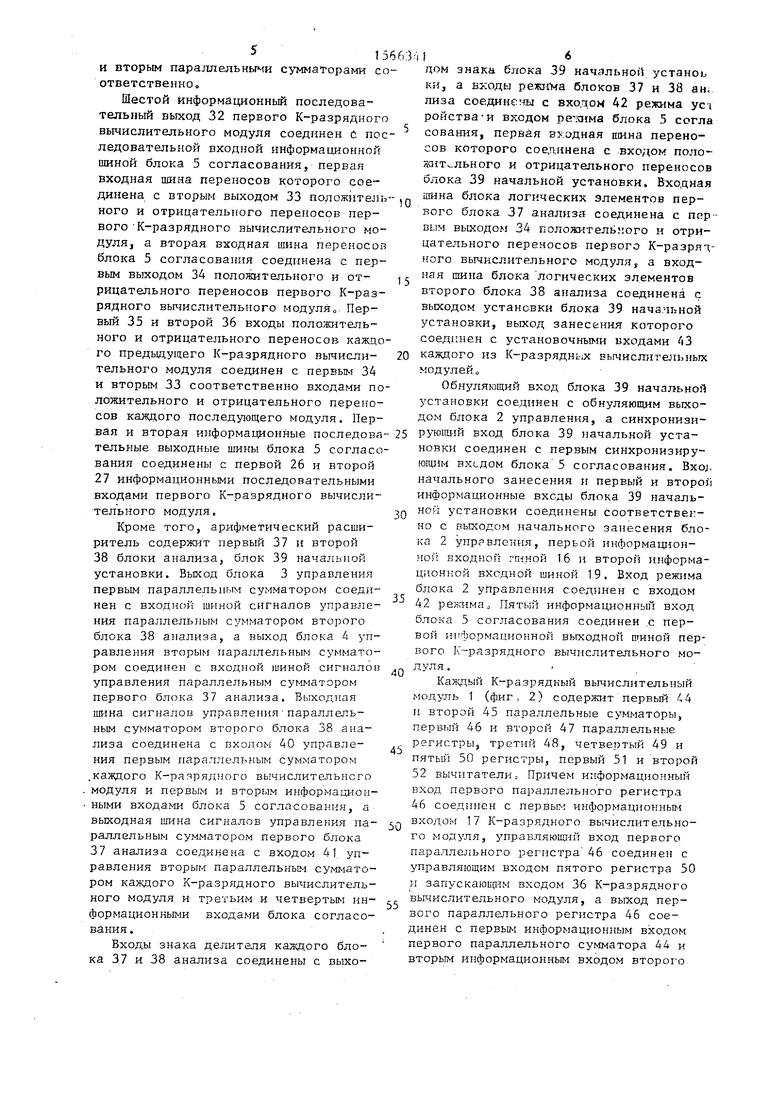

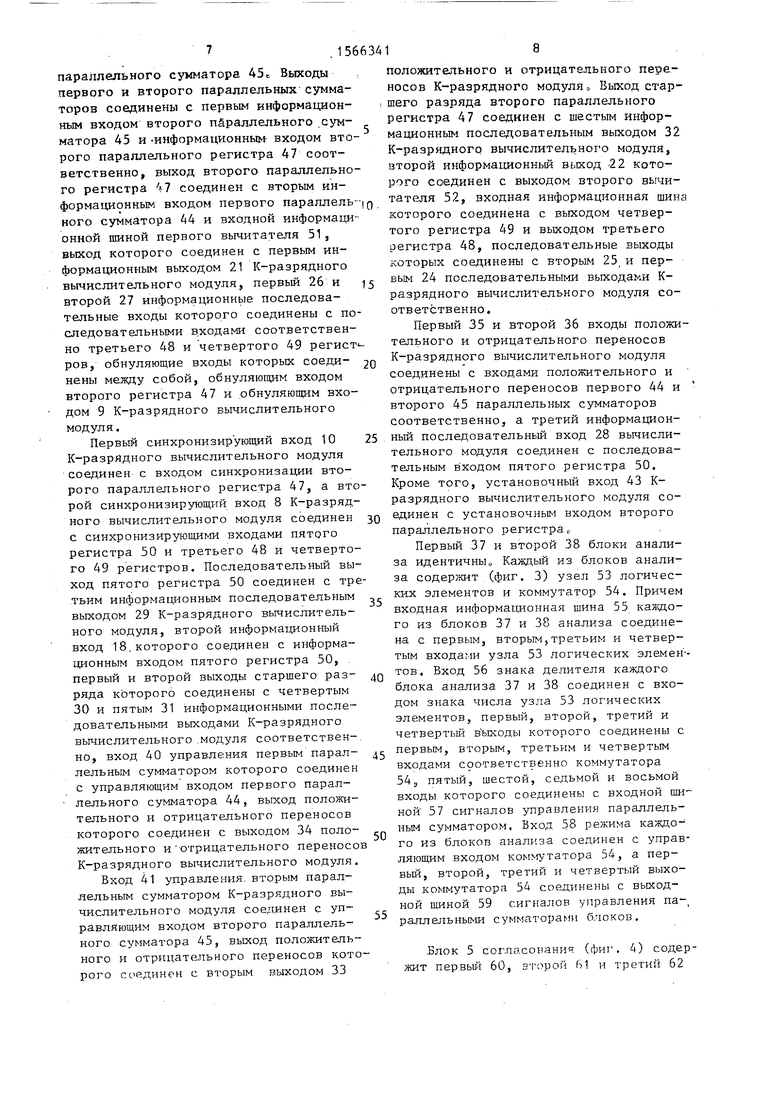

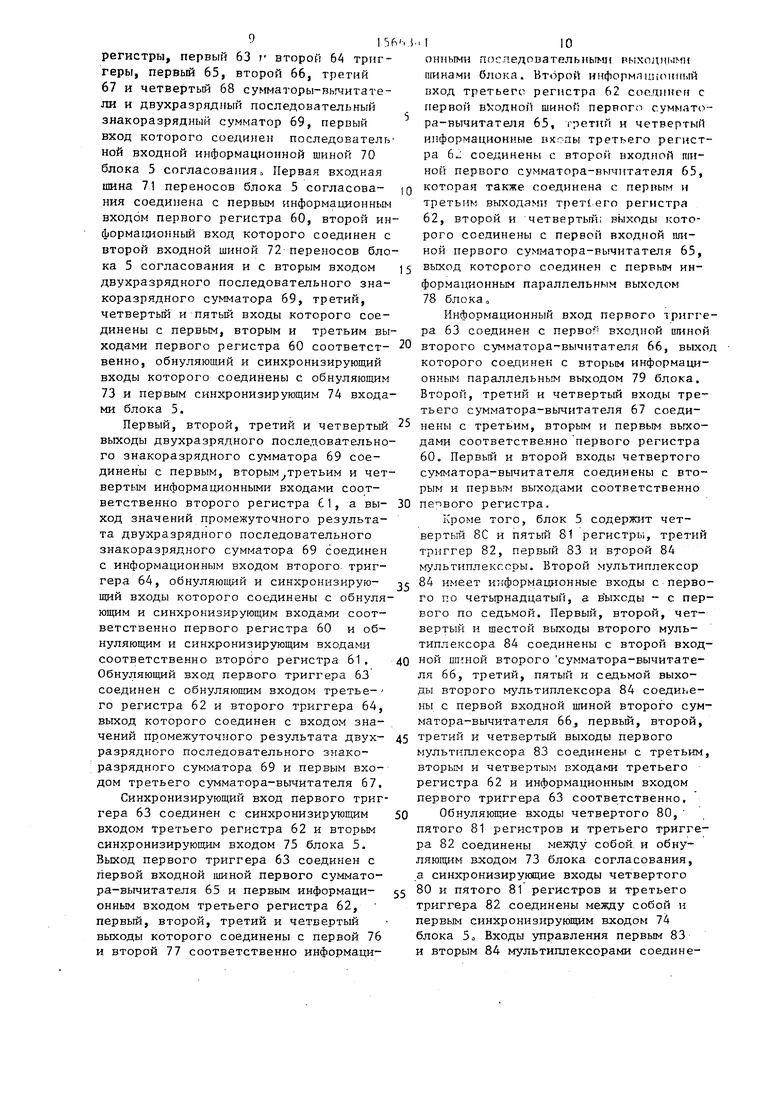

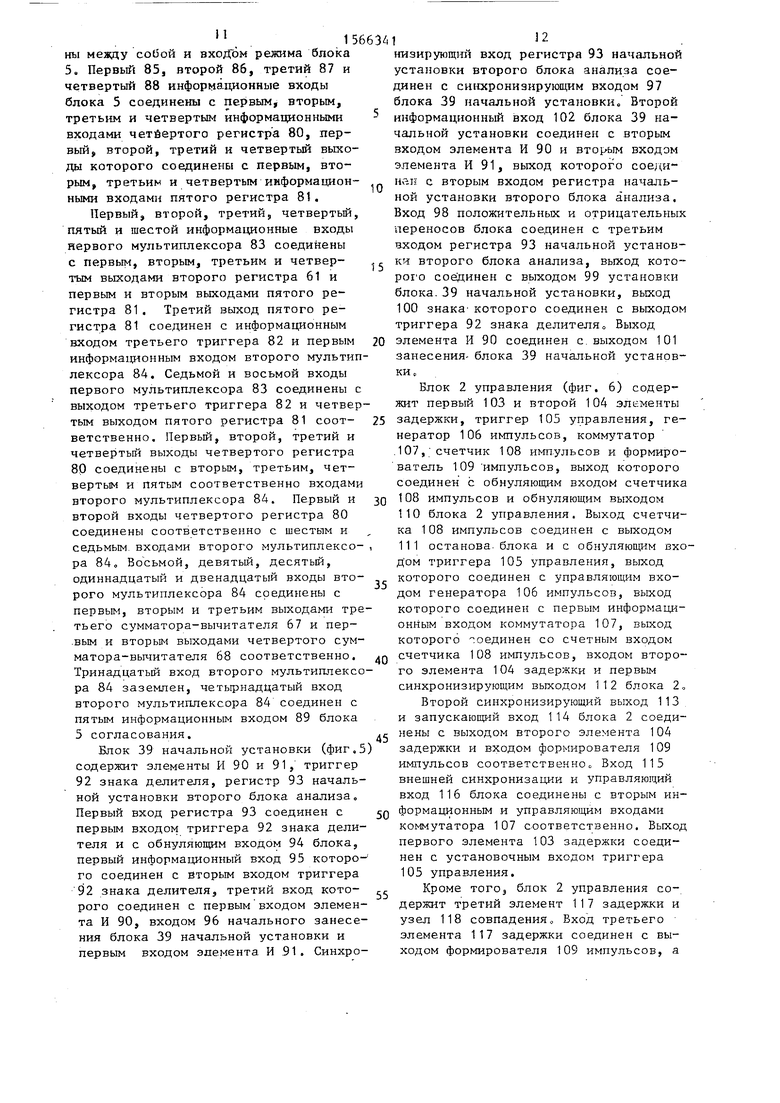

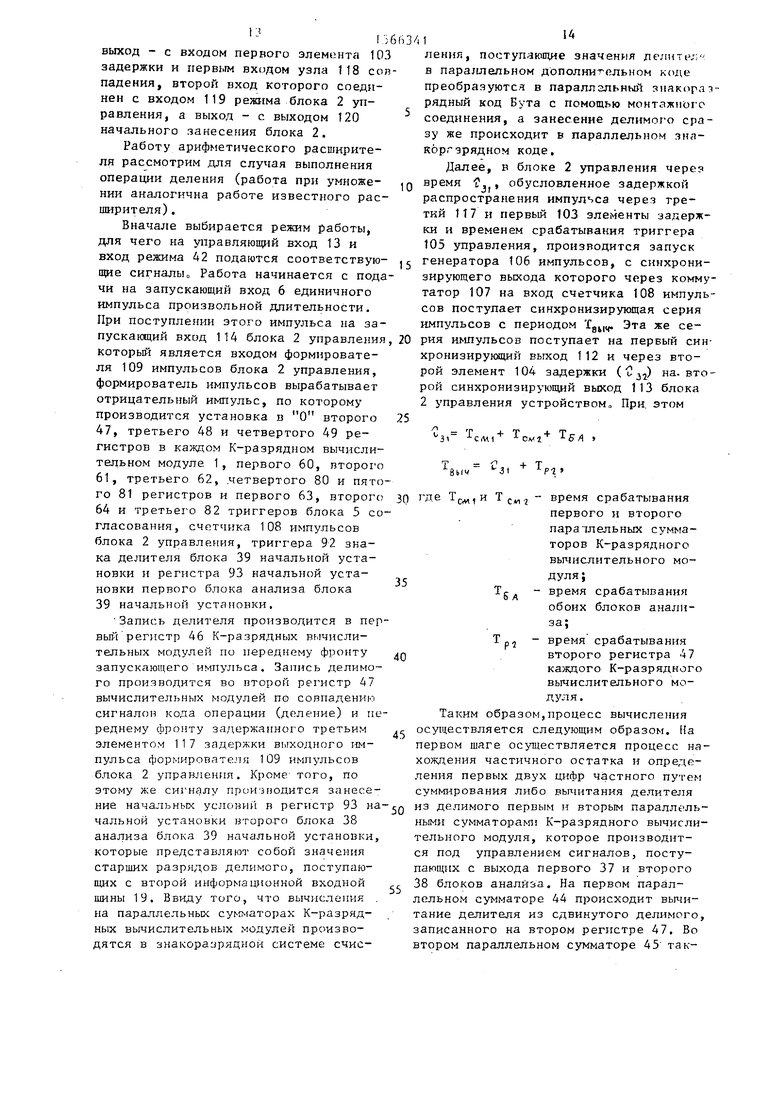

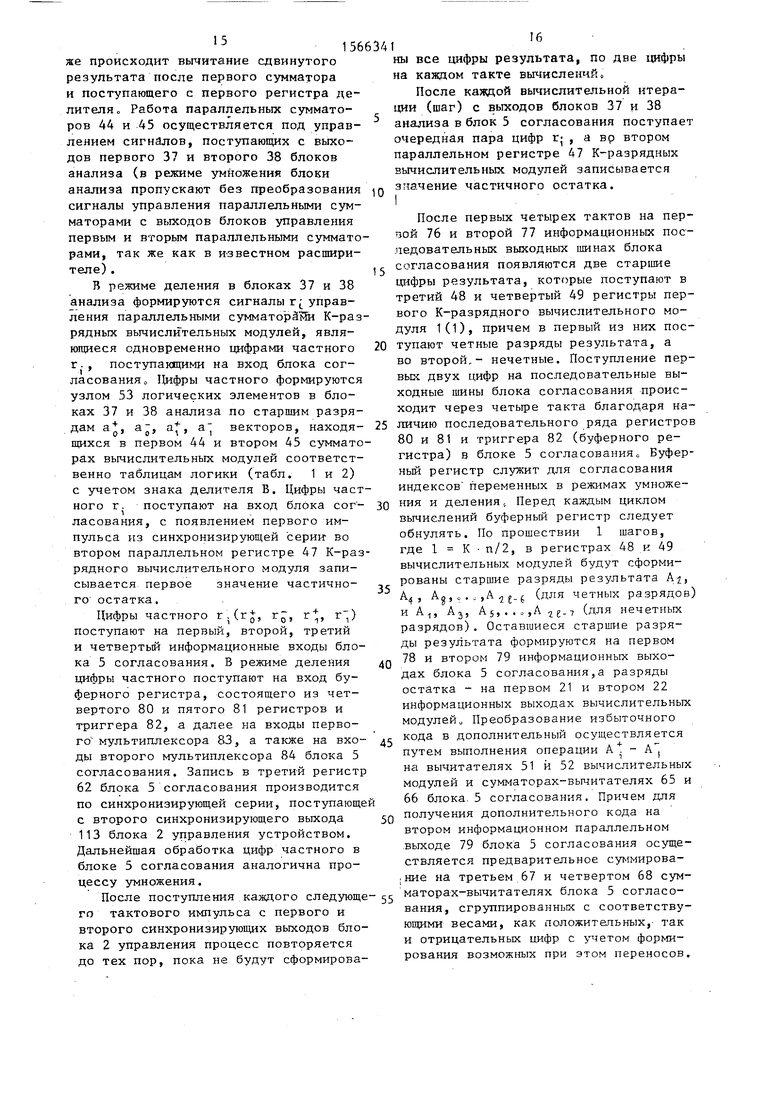

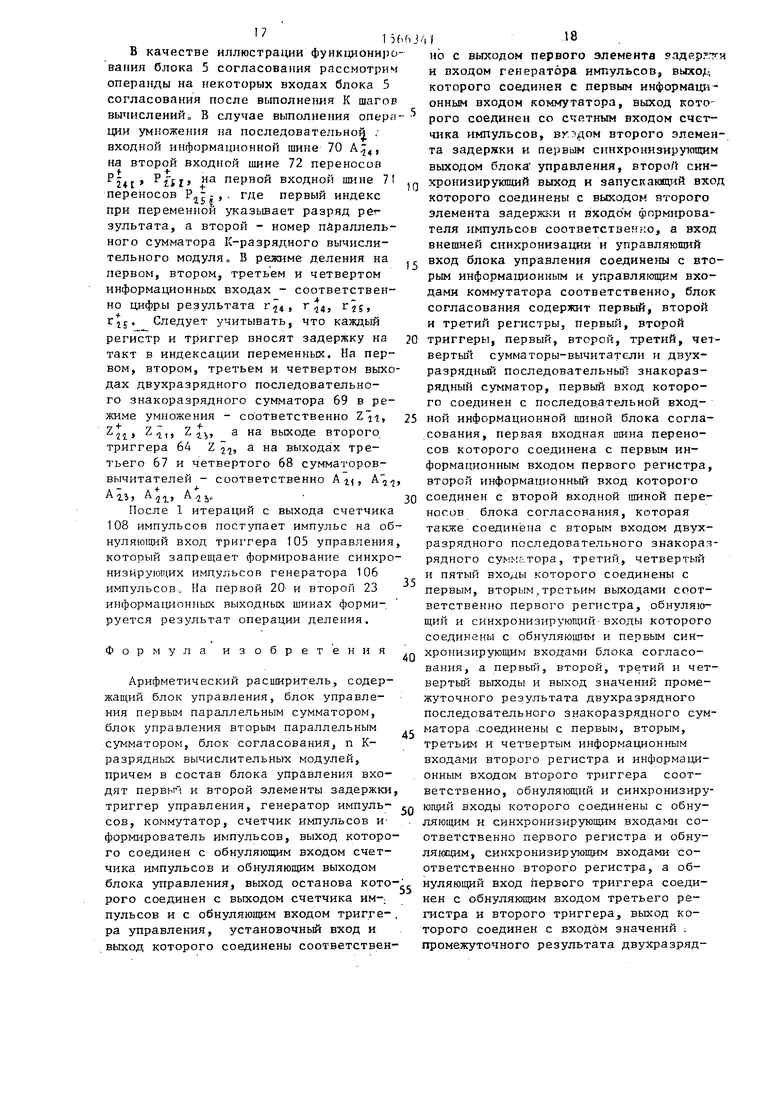

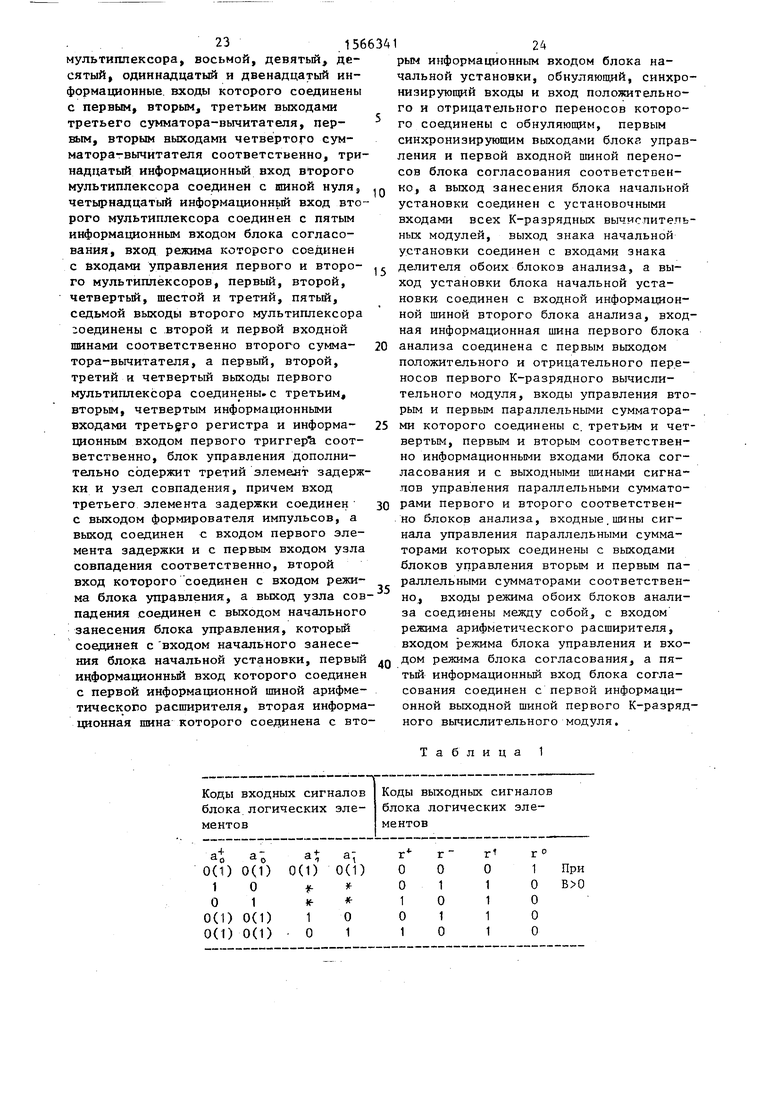

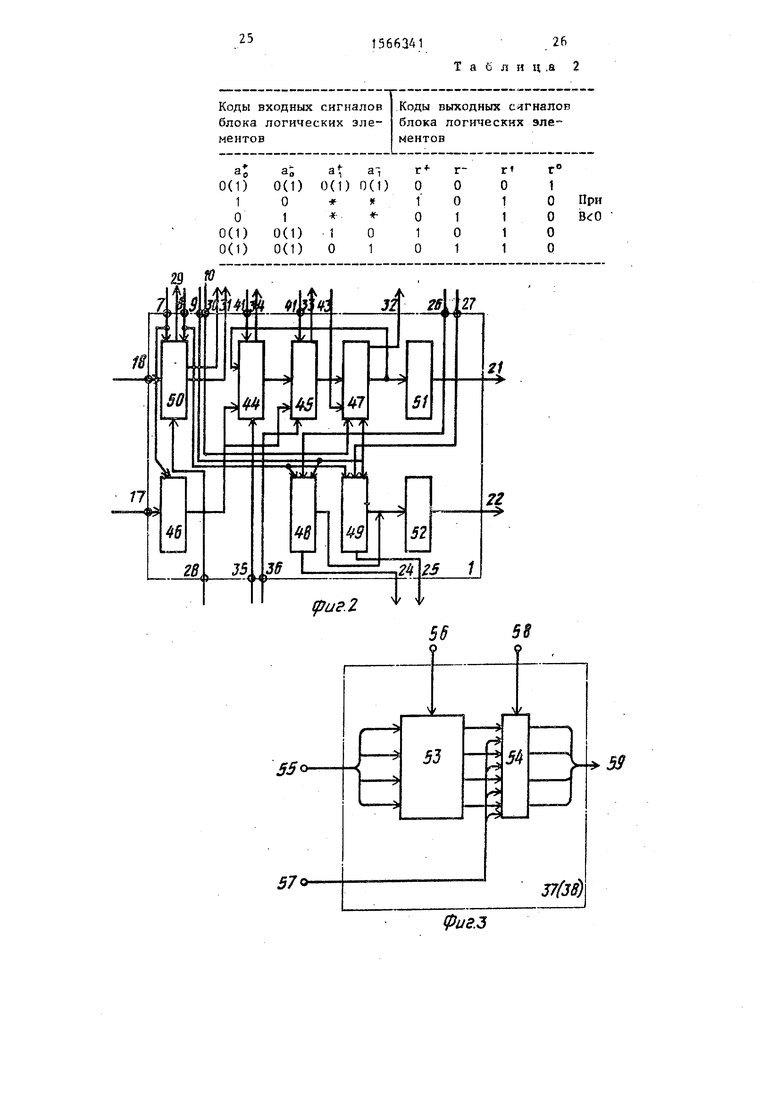

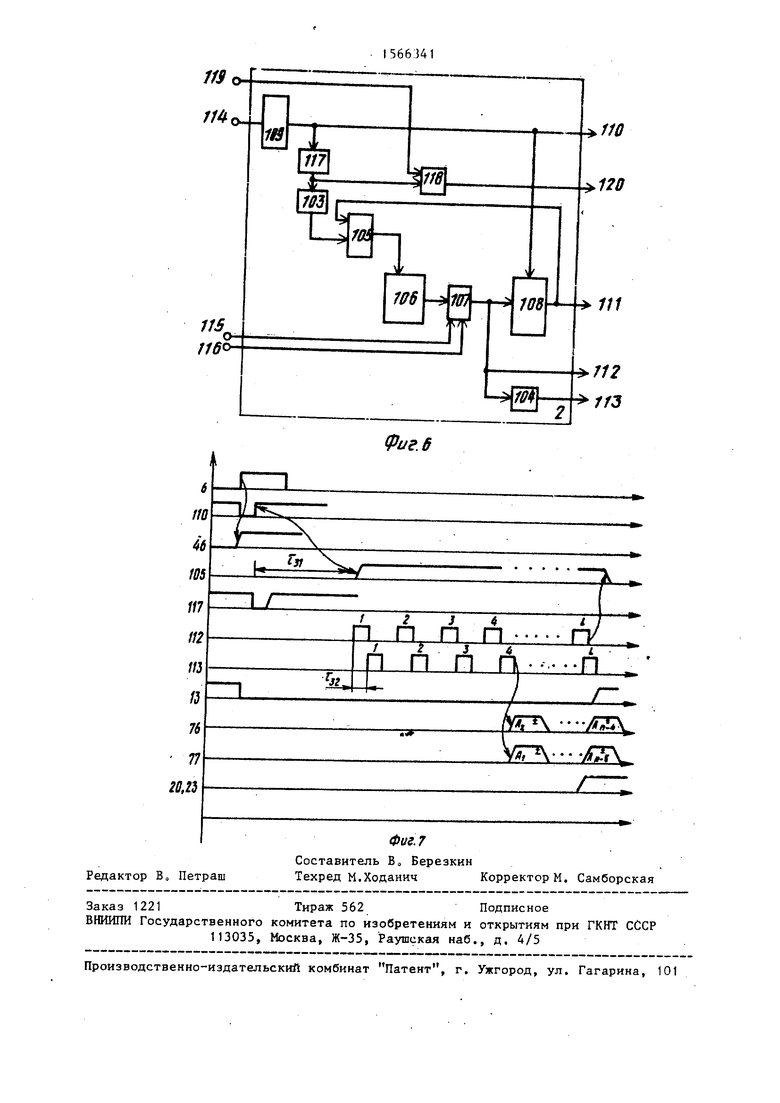

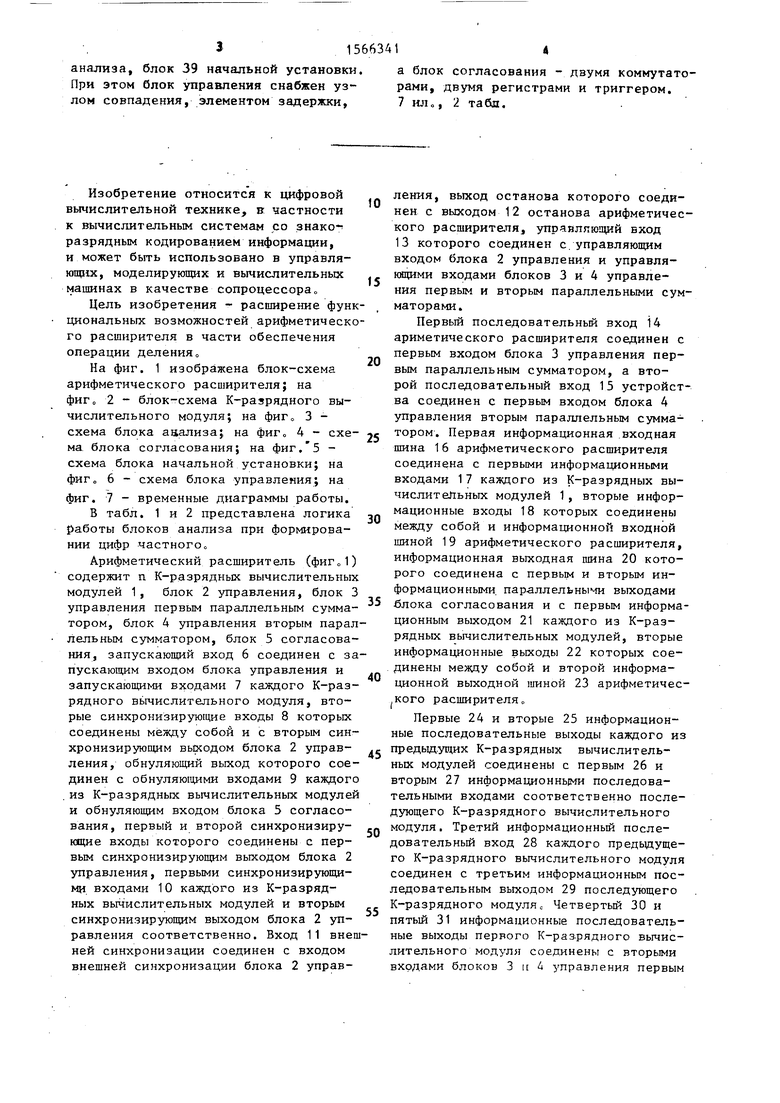

На фиг. 1 изображена блок-схема арифметического расширителя; на фиг„ 2 - блок-схема К-разрядного вычислительного модуля; на фиг0 3 - схема блока анллиза; на фиг„ 4 - схема блока согласования; на фиг.5 - схема блока начальной установки; на фиг„ 6 - схема блока управления; на

фиг. 7 - временные диаграммы работы.

В табл. 1 и 2 представлена логика работы блоков анализа при формировании цифр частного„

Арифметический расширитель (фиг01) содержит п К-разрядных вычислительных модулей 1, блок 2 управления, блок 3 управления первым параллельным сумматором, блок 4 управления вторым параллельным сумматором, блок 5 согласования, запускающий вход 6 соединен с запускающим входом блока управления и запускающими входами 7 каждого К-разрядного вычислительного модуля, вторые синхронизирующие входы 8 которых соединены между собой и с вторым синхронизирующим выходом блока 2 управления, обнуляющий выход которого соединен с обнуляющими входами 9 каждого из К-разрядных вычислительных модулей и обнуляющим входом блока 5 согласования, первый и второй синхронизирующие входы которого соединены с первым синхронизирующим выходом блока 2 управления, первыми синхронизирующими входами 10 каждого из К-разрядных вычислительных модулей и вторым синхронизирующим выходом блока 2 управления соответственно. Вход 11 внешней синхронизации соединен с входом внешней синхронизации блока 2 управ0

5

0

5

0

5

0

5

0

5

ления, выход останова которого соединен с выходом 12 останова арифметического расширителя, управляющий вход 13 которого соединен с управляющим входом блока 2 управления и управляющими входами блоков 3 и 4 управления первым и вторым параллельными сумматорами.

Первый последовательный вход 14 ариметического расширителя соединен с первым входом блока 3 управления первым параллельным сумматором, а второй последовательный вход 15 устройства соединен с первым входом блока 4 управления вторым параллельным сумматором. Первая информационная входная шина 16 арифметического расширителя соединена с первыми информационными входами 17 каждого из К-разрядных вычислительных модулей 1, вторые информационные входы 18 которых соединены между собой и информационной входной шиной 19 арифметического расширителя, информационная выходная шина 20 которого соединена с первым и вторым информационными параллельными выходами блока согласования и с первым информационным выходом 21 каждого из К-раэ- рядных вычислительных модулей, вторые информационные выходы 22 которых соединены между собой и второй информационной выходной шиной 23 арифметического расширителя,,

Первые 24 и вторые 25 информационные последовательные выходы каждого из предыдущих К-разрядных вычислительных модулей соединены с первым 26 и вторым 27 информационными последовательными входами соответственно последующего К-разрядного вычислительного модуля. Третий информационный последовательный вход 28 каждого предыдущего К-разрядного вычислительного модуля соединен с третьим информационным последовательным выходом 29 последующего К-разрядного модуля с Четвертый 30 и пятый 31 информационные последовательные выходы первого К-разрядного вычислительного модуля соединены с вторыми входами блоков 3 и 4 управления первым

515

и вторым параллельными сумматорами соответственно.

Шестой информационный последовательный выход 32 первого К-разрядного вычислительного модуля соединен с последовательной входной информационной шиной блока 5 согласования, первая входная шина переносов которого соединена с вторым выходом 33 положи т ель ного и отрицательного переносов первого К-разрядного вычислительного модуля, а вторая входная шина переносов блока 5 согласования соединена с первым выходом 34 положительного и от- рицательного переносов первого К-разрядного вычислительного модуля Первый 35 и второй 36 входы положительного и отрицательного переносов каждого предыдущего К-разрядного вычисли- тельного модуля соединен с первым 34 и вторым 33 соответственно входами положительного и отрицательного переносов каждого последующего модуля. Первая и вторая информационные последопп тельные выходные шины блока 5 согласования соединены с первой 26 и второй 27 информационными последовательными входами первого К-разрядного вычислительного модуля.

Кроме того, арифметический расширитель содержит первый 37 и второй 38 блоки анализа, блок 39 начальной установки. Выход блока 3 управления первым параллельным сумматором соединен с входной шиной сигналов управления параллельным сумматором второго блока 38 анализа, а выход - управления вторым параллельным сумма о- ром соединен с входной шиной сигналом управления параллельным оучмат ор -м первого блока 37 анализа. Вмхолпая шина сигналсь управпенш; параллельным сумматором второго блока ЗР анализа соединена с вх JJ;OM АО управле- ния первым парамчечьним сумматором .каждого К-раярядн го вычислптелыц го модуля и первым и вторым информационными входами блока 5 согласования, а выходная шина сигналов управления па- раллельным сумматором первого блика 37 анализа соединена с входом М управления вторым параллельным сумматором каждого К-разрядного вычислительного модуля и третьим и четвертым ин- формационными входами блока согласования.

Входы знака делителя каждого блока 37 и 38 анализа соединены с выхо,)

дом знака блока 39 начальной устаноь

ки, а входы режима блоков 37 и 38 ан. лиза соединены с входом 42 режима усi ронства-и входом ре-кима блока 5 согла сования, первая в эдная пина переносов которого соединена с входом поло- жит льного и отрицательного переносов блока 39 начальной установки. Входная 1шна блока логических элементов первого блока 37 анализа соединена с пор BLIM выходом 34 положительного и отрицательного переносов первого К-разряд- н.;го вычислительного модуля, а входная шина блока логических элементов второго блока 38 анализа соединена с выходом установки блока 39 начальной установки, выход занесения которого соединен с установочными входами 43 каждого из К-разрядных вычислительных модулей

Обнуляющий вход блока 39 начальной установки соединен с обнуляющим выходом блока 2 управления, а синхронизирующий вход блока 39 начальной установки соединен с первым синхронизирующим входом блока 5 согласования. Bxoj, начального занесения и первый и второй информационные входы блока 39 начальной установки соединены соответственно с выходом начального занесения блока 2 управления, ncpiон информационной входной :чнной 16 и второй информационной входной шиной 19. Вход режима блока 2 управления соединен с входом 42 Пятый информационный вход Схтока 5 согласования соединен о первой информационной выходной шиной первого I -разрядного вычислительного модуля.

Каждый К-разрядный вычислительный модуль 1 (фиг, 2) содержит первый 4 и второй 45 параллельные сумматоры, первый 46 и второй 47 параллельные регистры, третий 48, четвептый 49 и пятый 50 регистры, первый 51 и второй )-. вычитатели., Причем информационный вход первого параллельного регистра 46 соединен с первьгч информационным входом 17 К-разрядного вычислительного молуля, управляющий вход первого параллельного регистра 46 соединен с управляющим входом пятого регистра 50 и запускающем входом 36 К-разрядного вычислительного модуля, а вьгход первого параллельного регистра 46 соединен с первым информационным входом первого параллельного сумматора 44 и вторым информационным входом второго

7156

параллельного сумматора 45 Выходы первого и второго параллельных сумматоров соединены с первым информационным входом второго параллельного сумматора 45 и-информационным входом второго параллельного регистра 47 соответственно, выход второго параллельного регистра соединен с вторым информационным входом первого параллельного сумматора 44 и входной информационной шиной первого вычитателя 51, выход которого соединен с первым информационным выходом 21 К-разрядного вычислительного модуля, первый 26 и второй 27 информационные последовательные входы которого соединены с последовательными входами соответственно третьего 48 и четвертого 49 регистров, обнуляющие входы которых соеди- йены между собой, обнуляющим входом второго регистра 47 и обнуляющим входом 9 К-разрядного вычислительного модуля.

Первый синхронизирующий вход 10 К-разрядного вычислительного модуля соединен с входом синхронизации второго параллельного регистра 47, а второй синхронизирующий вход 8 К-разрядного вычислительного модуля соединен с синхронизирующими входами пятого регистра 50 и третьего 48 и четвертого 49 регистров. Последовательный выход пятого регистра 50 соединен с третьим информационным последовательным выходом 29 К-разрядного вычислительного модуля, второй информационный вход 18 которого соединен с информационным входом пятого регистра 50, первый и второй выходы старшего раз- ряда которого соединены с четвертым 30 и пятым 31 информационными последовательными выходами К-разрядного вычислительного модуля соответственно, вход 40 управления первым парал- лельным сумматором которого соединен с управляющим входом первого параллельного сумматора 44, выход положительного и отрицательного переносов которого соединен с выходом 34 поло- жительного и отрицательного переносов К-разрядного вычислительного модуля.

Вход 41 управления вторым параллельным сумматором К-разрядного вычислительного модуля соединен с уп- равляющим входом второго параллельного сумматора 45, выход положительного и отрицательного переносов которого соединен с вторым выходом 33

8

положительного и отрицательного переносов К-разрядного модуля. Выход старшего разряда второго параллельного регистра 47 соединен с шестым информационным последовательным выходом 32 К-разрядного вычислительного модуля, второй информационный выход 22 которого соединен с выходом второго вычитателя 52, входная информационная шин которого соединена с выходом четвертого регистра 49 и выходом третьего регистра 48, последовательные выходы которых соединены с вторым 25 и первым 24 последовательными выходами К- разрядного вычислительного модуля соответственно.

Первый 35 и второй 36 входы положительного и отрицательного переносов К-разрядного вычислительного модуля соединены с входами положительного и отрицательного переносов первого 44 и второго 45 параллельных сумматоров соответственно, а третий информационный последовательный вход 28 вычислительного модуля соединен с последовательным входом пятого регистра 50. Кроме того, установочный вход 43 К- разрядного вычислительного модуля соединен с установочным входом второго параллельного регистрас

Первый 37 и второй 38 блоки анализа идентичны Каждый из блоков анализа содержит (фиг. 3) узел 53 логических элементов и коммутатор 54. Причем входная информационная шина 55 каждого из блоков 37 и 38 анализа соединена с первым, вторым,третьим и четвертым входами узла 53 логических элементов. Вход 56 знака делителя каждого блока анализа 37 и 38 соединен с входом знака числа узла 53 логических элементов, первый, второй, третий и четвертый выходы которого соединены с первым, вторым, третьим и четвертым входами соответственно коммутатора 54, пятый, шестой, седьмой и восьмой входы которого соединены с входной шиной 57 сигналов управления параллельным сумматором. Вход 58 режима каждого из блоков анализа соединен с управляющим входом коммутатора 54, а первый, второй, третий и четвертый выходы коммутатора 54 соединены с выходной шиной 59 сигналов мтравления па-, раллельными сумматорами бчоков.

Блок 5 согплссминия (фиг. 4) содержит первый 60, P i.ip -ж М и третий 62

регистры, первый 63 т- второй 64 триггеры, первый 65, второй 66, третий 67 и четвертый 68 сумматоры-вычитате- ли и двухразрядмый последовательный знакоразрядный сумматор 69, первый вход которого соединен последовательной входной информационной шиной 70 блока 5 согласования, Первач входная шина 71 переносов блока 5 согласова- ния соединена с первым информационным входом первого регистра 60, второй информационный вход которого соединен с второй входной шиной 72 переносов блока 5 согласования и с вторым входом двухразрядного последовательного зна- кораэрядного сумматора 69, третий, четвертый и пятый входы которого соединены с первым, вторым и третьим выходами первого регистра 60 соответст- венно, обнуляющий и синхронизирующий входы которого соединены с обнуляющим 73 и первым синхронизирующим 74 входами блока 5.

Первый, второй, третий и четвертый выходы двухразрялного последовательного знакоразрядного сумматора 69 соединены с первым, вторым третьим и четвертым информационными входами соответственно второго регистра i 1, а вы- ход значений промежуточного результата двухразрядного последовательного знакоразрядного сумматора 69 соединен с информационным входом второго триггера 64, обнуляющий и синхронизирую- щий входы которого соединены с обнуляющим и синхронизирующим входами соответственно первого регистра 60 и обнуляющим и синхронизирующим входами соответственно второго регистра 61. Обнуляющий вход первого триггера 63 соединен с обнуляющим входом третьего регистра 62 и второго триггера 64, выход которого соединен с входом значений промежуточного результата двух- разрядного последовательного знакоразрядного сумматора 69 и первым входом третьего сумматора-вычитателя 67.

Синхронизирующий вход первого триггера 63 соединен с синхронизирующим входом третьего регистра 62 и вторым синхронизирующим входом 75 блока 5. Выход первого триггера 63 соединен с первой входной шиной первого сумматора-вычитателя 65 и первым информаци- онным входом третьего регистра 62, первый, второй, третий и четвертый выходы которого соединены с первой 76 и второй 77 соответственно информационными последовательными выходными тинами блока. Второй информационный нход третьего регистра 62 соппнгн с первой входной шнноГ) первого гуммато- ра-вычитателя 65, 1ретий и четвертый информационные их пы третьего регистра 6- соединены с второй входной шиной первого сумматора-вычптателя 65, которая также соединена с первым и третьим выходами третlего регистра 62, второй и четвертый, выходы которого соединены с первой входной шиной первого сумматора-вычитателя 65, выход которого соединен с первым информационным параллельным выходом 78 блока,

Информационный вход первого триггера 63 соединен с перво- входной шиной второго сумматора-вычитателя 66, выхо которого соединен с вторым информационным параллельным выходом 79 блока. Второй, третий и четвертый входы третьего сумматора-вычитателя 67 соединены с третьим, вторым и первым выходами соответственно первого регистра 60. Первый и второй входы четвертого сумматора-вычитателя соединены с вторым и первым выходами соответственно первого регистра.

Кроме того, блок 5 содержит четвертый 8С и пятый 81 регистр, третий триггер 82, первый 83 и второй 84 мультиплексоры. Второй мультиплексор 84 имеет информационные входы с первого по четырнадцатый, а в ыхгды - с пер- РОГО по седьмой. Первый, второй, четвертый и шестой выходы второго мультиплексора 84 соединены с второй входной шиной второго сумматора-вычитателя 66, третий, пятый и седьмой выходы второго мультиплексора 84 соедиье- ны с первой входной шиной второго сумматора-вычитателя 66, первый, второй, третий и четвертый выходы первого мультиплексора 83 соединены с третьим, вторым и четвертым входами третьего регистра 62 и информационным входом первого триггера 63 соответственно.

Обнуляющие входы четвертого 80, пятого 81 регистров и третьего триггера 82 соединены между собой и обнуляющим входом 73 блока согласования, а синхронизирующие входы четвертого 80 и пятого 81 регистров и третьего триггера 82 соединены между собой и первым синхронизирующим входом 74 блока 5о Входы управления первым 83 и вторым 84 мультиплексорами соеднне11 .156

ны меаду собой и входом режима блока

Первый, второй, третий, четвертый, пятый и шестой информационные входы первого мультиплексора 83 соединены с первым, вторым, третьим и четвер- тым выходами второго регистра 61 и первым и вторым выходами пятого регистра 81. Третий выход пятого регистра 81 соединен с информационным входом третьего триггера 82 и первым информационным входом второго мультиплексора 84. Седьмой и восьмой входы первого мультиплексора 83 соединены с выходом третьего триггера 82 и четвертым выходом пятого регистра 81 соот- ветственно. Первый, второй, третий и четвертый выходы четвертого регистра 80 соединены с вторым, третьим, четвертым и пятым соответственно входами второго мультиплексора 84. Первый и второй входы четвертого регистра 80 соединены соответственно с шестым и седьмым входами второго мультиплексо- ра 84. Восьмой, девятый, десятый, одиннадцатый и двенадцатый входы второго мультиплексора 84 соединены с первым, вторым и третьим выходами третьего сумматора-вычитателя 67 и первым и вторым выходами четвертого сумматора-вычитателя 68 соответственно. Тринадцатый вход второго мультиплексора 84 заземлен, четырнадцатый вход второго мультиплексора 84 соединен с пятым информационным входом 89 блока 5 согласования.

Блок 39 начальной установки (фиг. 5 содержит элементы И 90 и 91, триггер 92 знака делителя, регистр 93 начальной установки второго блока анализа. Первый вход регистра 93 соединен с первым входом триггера 92 знака делителя и с обнуляющим входом 94 блока, первый информационный вход 95 которого соединен с вторым входом триггера 92 знака делителя, третий вход кото- рого соединен с первым входом элемента И 90, входом 96 начального занесения блока 39 начальной установки и первым входом элемента И 91. Синхро

, 0 5 0 Q

0 с

5

112

визирующий вход регистра 93 начальной установки второго блока анализа соединен с синхронизирующим входом 97 блока 39 начальной установки. Второй информационный вход 102 блока 39 начальной установки соединен с вторым входом элемента И 90 и вторым входом элемента И 91, выход которого соединен с вторым входом регистра начальной установки второго блока анализа. Вход 98 положительных и отрицательных переносов блока соединен с третьим входом регистра 93 начальной установки второго блока анализа, выход которого соединен с выходом 99 установки блока 39 начальной установки, выход 100 знака которого соединен с выходом триггера 92 знака делителя,, Выход элемента И 90 соединен с выходом 101 занесения, блока 39 начальной установки.

Блок 2 управления (фиг. 6) содержит первый 103 и второй 104 элементы задержки, триггер 105 управления, генератор 106 импульсов, коммутатор 107, счетчик 108 импульсов и формирователь 109 импульсов, выход которого соединен с обнуляющим входом счетчика 108 импульсов и обнуляющим выходом

110блока 2 управления. Выход счетчика 108 импульсов соединен с выходом

111останова блока и с обнуляющим входом триггера 105 управления, выход которого соединен с управляющим входом генератора 106 импульсов, выход которого соединен с первым информационным входом коммутатора 107, выход которого -оединен со счетным входом счетчика 108 импульсов, входом второго элемента 104 задержки и первым синхронизирующим выходом 112 блока 2,

Второй синхронизирующий выход 113 и запускающий вход 114 блока 2 соединены с выходом второго элемента 104 задержки и входом формирователя 109 импульсов соответственно Вход 115 внешней синхронизации и управляющий вход 116 блока соединены с вторым информационным и управляющим входами коммутатора 107 соответственно. Выход первого элемента 103 задержки соединен с установочным входом триггера 105 управления.

Кроме того, блок 2 управления содержит третий элемент 117 задержки и узел 118 совпадения Вход третьего элемента 117 задержки соединен с выходом формирователя 109 импульсов, а

выход - с входом первого элемента 103 задержки и первым входом узла 118 con- падения, второй вход которого соединен с входом 119 режима блока 2 управления, а выход - с выходом 120 начального занесения блока 2.

Работу арифметического расширителя рассмотрим для случая выполнения операции деления (работа при умножении аналогична работе известного расширителя) .

Вначале выбирается режим работы, для чего на управляющий вход 13 и

лепил, поступающие значения делите; в параллельном дополнительном коде преобразуются в параллельный знакорач- рядный код Бута с помощью монтажного соединения, а занесение делимого сразу же происходит в параллельном зня- коргзрядном коде.

Далее, в блоке 2 управления через jg время Ј, , обусловленное задержкой распространения импульса через третий 117 II первый 103 элементы задержки и временем срабатывания триггера

105 управления, производится запуск вход режима 42 подаются соответствую- ,5 генератора 106 импульсов, с синхрони- щие сигналы Работа начинается с пода- зирующего выхода которого через комму- чи на запускающий вход 6 единичного импульса произвольной длительности. При поступлении этого импульса на зататор 107 на вход счетчика 108 импульсов поступает синхронизирующая серия импульсов с периодом Т841Ч. Эта же сепускакщий вход 114 блока 2 управления, 20 рия импульсов поступает на первый син

который является входом формирователя 109 импульсов блока 2 управления, формирователь импульсов вырабатывает отрицательный импульс, по которому производится установка ц О второго

TCMI+ тсмг+ ТБА

31

Lt c

31

+ Т

PI

47, третьего 48 и четвертого 49 регистров в каждом К-разрядном вычислительном модуле 1, первого 60, второго 61, третьего 62, четвертого 80 и пятого 81 регистров и первого 63, второго 30 Де ТС(М7 - время срабатывания 64 и третьего 82 триггеров блока 5 согласования, счетчика 108 импульсов блока 2 управления, триггера 92 знака делителя блока 39 начальной установки и регистра УЗ начальной установки первого блока анализа блока 39 начальной установки.

Запись делителя производится в первый регистр 46 К-рачрядных вычислительных модулей по переднему фронту запускающего импульса. Запись делимого производится РО пторои регистр 47 вычислительных модулей по совпаденпы сигналов кола операции (деление) и переднему фронту задержанного третьим .,- осуществляется следующим образом. На элементом 117 задержки выкидного им- первом шаге осуществляется процесс на- пульса формирователя 109 импульсов хождения частичного остатка и опреде- блока 2 управления. Кроме того, по ления первых двух цифр частного путем этому же сигналу производится занесе- суммирования либо вычитания делителя ние начальных условий в регистр 93 из делимого первым IT вторым параллель- чальнои устаниики второго блока 38

35

40

первого и второго пара тельных сумматоров К-разрядного вычислительного модуля;

время срабатывания обоих блоков анализа;

время срабатывания второго регистра 47 каждого К-разрядного вычислительного модуля. Таким образом,процесс вычисления

6л

pi

ными сумматорами К-разрядного вычислительного модуля, которое производится под управлением сигналов, поступающих с выхода первого 37 и второго 38 блоков анализа. На первом параллельном сумматоре 44 происходит вычитание делителя из сдвинутого делимого, записанного на втором регистре 47. Во втором параллельном сумматоре 45 таканализа блока 39 начальной установки, которые лрицстаншяют собой значения старших разрядов делимого, поступающих с второй информационной входной шины 19. Ввиду того, ч го вычисления на параллельных сумматорах К-разряд- ных вычислительных модулей производятся в знакораиряднои системе счислепил, поступающие значения делите; в параллельном дополнительном коде преобразуются в параллельный знакорач- рядный код Бута с помощью монтажного соединения, а занесение делимого сразу же происходит в параллельном зня- коргзрядном коде.

Далее, в блоке 2 управления через время Ј, , обусловленное задержкой распространения импульса через третий 117 II первый 103 элементы задержки и временем срабатывания триггера

105 управления, производится запуск генератора 106 импульсов, с синхрони- зирующего выхода которого через комму-

татор 107 на вход счетчика 108 импульсов поступает синхронизирующая серия импульсов с периодом Т841Ч. Эта же сехронизирующий выход 112 и через второй элемент 104 задержки () на. второй синхронизирующий выход 113 блока 2 управления устройством, При этом

25

TCMI+ тсмг+ ТБА

31

е ТС(М7 - время с

Lt c

31

+

ТС(М7

Де ТС(М7 - время срабатывания

осуществляется следующим образом. На первом шаге осуществляется процесс на- хождения частичного остатка и опреде- ления первых двух цифр частного путем суммирования либо вычитания делителя из делимого первым IT вторым параллель-

первого и второго пара тельных сумматоров К-разрядного вычислительного модуля;

время срабатывания обоих блоков анализа;

время срабатывания второго регистра 47 каждого К-разрядного вычислительного модуля. Таким образом,процесс вычисления

6л

pi

,- осуществляется следующим образом. На первом шаге осуществляется процесс на- хождения частичного остатка и опреде- ления первых двух цифр частного путем суммирования либо вычитания делителя g из делимого первым IT вторым параллель-

5

ными сумматорами К-разрядного вычислительного модуля, которое производится под управлением сигналов, поступающих с выхода первого 37 и второго 38 блоков анализа. На первом параллельном сумматоре 44 происходит вычитание делителя из сдвинутого делимого, записанного на втором регистре 47. Во втором параллельном сумматоре 45 так15156

же происходит вычитание сдвинутого

результата после первого сумматора и поступающего с первого регистра делителя Работа параллельных сумматоров 44 и 45 осуществляется под управлением сигналов, поступающих с выходов первого 37 и второго 38 блоков анализа (в режиме умножения блоки анализа пропускают без преобразования сигналы управления параллельными сумматорами с выходов блоков управления первым и вторым параллельными сумматорами, так же как в известном расширителе) .

В режиме деления в блоках 37 и 38 анализа формируются сигналы г управления параллельными сумматорйми К-раз рядных вычислительных модулей, являющиеся одновременно цифрами частного г. , поступающий на вход блока согласования, Цифры частного формируются узлом 53 логических элементов в блоках 37 и 38 анализа по старшим разрядам а, а, а, а векторов, находя- щихся в первом 44 и втором 45 сумматорах вычислительных модулей соответственно таблицам логики (табл. 1 и 2) с учетом знака делителя В. Цифры частного г. поступают на вход блока сог- ласования, с появлением первого импульса из синхронизирующей серии во втором параллельном регистре 47 К-раз рядного вычислительного модуля записывается первое значение частично- го остатка.

Цифры частного r.((rj, г, г + , г) поступают на первый, второй, третий и четвертый информационные входы блока 5 согласования. В режиме деления цифры частного поступают на вход буферного регистра, состоящего из четвертого 80 и пятого 81 регистров и триггера 82, а далее на входы первого мультиплексора 83, а также на вхо- ды второго мультиплексора 84 блока 5 согласования. Запись в третий регистр 62 блока 5 согласования производится по синхронизирующей серии, поступающе с второго синхронизирующего выхода 113 блока 2 управления устройством. Дальнейшая обработка цифр частного в блоке 5 согласования аналогична процессу умножения.

После поступления каждого следующе го тактового импульса с первого и второго синхронизирующих выходов блока 2 управления процесс повторяется до тех пор, пока не будут сформирова16

ны все цифры результата, по две цифры на каждом такте вычислений

После каждой вычислительной итерации (шаг) с выходов блоков 37 и 38 анализа в блок 5 согласования поступае очередная пара цифр г; , а вр втором параллельном регистре 47 К-разрядных вычислительных модулей записывается значение частичного остатка. I

После первых четырех тактов на первой 76 и второй 77 информационных последовательных выходных шинах блока согласования появляются две старшие цифры результата, которые поступают в третий 48 и четвертый 49 регистры первого К-разрядного вычислительного модуля 1(1), причем в первый из них поступают четные разряды результата, а во второй,- нечетные. Поступление первых двух цифр на последовательные выходные шины блока согласования происходит через четыре такта благодаря наличию последовательного ряда регистро 80 и 81 и триггера 82 (буферного регистра) в блоке 5 согласования„ Буферный регистр служит для согласования индексов переменных в режимах умножения и деления, Перед каждым циклом вычислений буферный регистр следует обнулять. По прошествии 1 шагов, где 1 К п/2, в регистрах 48 и 49 вычислительных модулей будут сформированы старшие разряды результата А, А-4 Ая - - А 11-1 (лля четных разрядов и А.,, А3, А5,.., (для нечетных разрядов). Оставшиеся старшие разряды результата формируются на первом 78 и втором 79 информационных выходах блока 5 согласования,а разряды остатка - на первом 21 и втором 22 информационных выходах вычислительных модулей., Преобразование избыточного кода в дополнительный осуществляется путем выполнения операции А . - А ( на вычитателях 51 и 52 вычислительных модулей и сумматсрах-вычитателях 65 и 66 блока 5 согласования. Причем для получения дополнительного кода на втором информационном параллельном выходе 79 блока 5 согласования осуществляется предварительное суммирова- iние на третьем 67 и четвертом 68 сум- маторах-вычитателях блока 5 согласования, сгруппированных с соответствующими весами, как лоложитетьных, так и отрицательных цифр с учетом формирования возможных при этом переносов.

17

В качестве иллюстрации функционирования блока 5 согласования рассмотрим операнды на некоторых входах блока 5 согласования после выполнения К шагов вычислений,, В случае выполнения опера- ции умножения на последовательной . входной информационной шине 70 , на второй входной шине 72 переносов Pni pfn а пеРвой входной шине 7 переносов Р где первый индекс при переменной указывает разряд зультата, а второй - номер параллельного сумматора К-разрядного вычислительного модуля. В режиме деления на первом, втором, третьем и четвертом информационных входах - соответственно цифры результата , г 4, , tj;. Следует учитывать, что каждый регистр и триггер вносят задержку на такт в индексации переменных. На первом, втором, третьем и четвертом выходах двухразрядного последовательного знакоразрядного сумматора 69 в режиме умножения - соответственно , Z21, Z,, Z г, а на выходе второго триггера 64 Z ц, а на выходах третьего 67 и четвертого 68 сумматоров- вычитателей - соответственно А ц , , Аг А 31 A,JS.

После 1 итераций с выхода счетчика 108 импульсоп поступает импульс на обнуляющий вход триггера 105 управления, который запрещает формирование синхронизирующих HMnyjibcoB генератора 106 импульсов Па первой 20 и второй 23 информационных выходных шинах формируется результат операции деления.

Формула изобретения

4

Арифметический расширитель, содержащий блок управления, блок управления первым параллельным сумматором, блок управления вторым параллельным сумматором, блок согласования, n K- разрядных вычислительных модулей, причем в состав блока управления входят первым и второй элементы задержки, триггер управления, генератор импуль- , сов, коммутатор, счетчик импульсов и формирователь импульсов, выход которого соединен с обнуляющим входом счетчика импульсов и обнуляющим выходом блока управления, выход останова кото- рого соединен с выходом счетчика импульсов и с обнуляющим входом тригге- , ра управления, установочный вход и выход которого соединены соответствен

15

202530

40

45

,Q

но с выходом первого элемента задергай н входом генератора импульсов, выход которого соединен с первым информационным входом коммутатора, выход которого соединен со счетным входом счетчика импульсов, ВУДОМ второго элемента задержки и первом синхронизирующим выходом блока1 управления, втором синхронизирующий выход и запускающий вход которого соединены с выходом второго элемента задержки и входом формирователя импульсов соответственно, а вход внешней синхронизации и управляющий вход блока управления соединены с вторым информационным и управляющим входами коммутатора соответственно, блок согласования содержит первый, второй и третий регистры, первый, второй триггеры, первый, второй, третий, четвертый сумматоры-вычитатслн н двухразрядный последовательный знакораз- ряднын сумматор, первый вход которого соединен с последовательной входной информационной шиной блока согласования, первая входная шина переносов которого соединена с первым информационным входом первого регистра, второй информационный вход которого соединен с второй входной шиной переносов блока согласования, которая также соединена с вторым входом двухразрядного последовательного энакорач- рядного сумм- -.тора, третий, четвертый и пятый входы которого соединены с первым, вторым,третьим выходами соответственно первого регистра, обнуляющий и синхронизирующий входы которого соединены с обнуляющим и первым синхронизирующим входами блока согласования, а первый, второй, третий и чет- нертый выходы и выход значений промежуточного результата двухраэрядного последовательного знакоразрядного сумматора соединены с первым, вторым, третьим и четвертым информационным входами второго регистра и информационным входом второго триггера соответственно, обнуляющий и синхронизирующий входы которого соединены с обнуляющим и синхронизирующим входами соответственно первого регистра и обнуляющим, синхронизирующим входами соответственно второго регистра, а обнуляющий вход первого триггера соединен с обнуляющим входом третьего регистра и второго триггера, выход которого соединен с входом значений промежуточного результата двухразряд19156

ного последовательного энакоразрядно- го сумматора и передо входом третьего сумматора-вычитателя, причем синхронизирующий вход первого триггера соединен с синхронизирующим входом третьего регистра и вторым синхронизирующим входом блока согласования, а выход первого триггера соединен с первой входной шиной первого суммато- ра-вычитателя и первым информационным входом третьего регистра, первый, второй, третий и четвертый выходы которого соединены с первой и второй соответственно информационными последова- тельными выходными шинами блока согласования, а второй информационный вход третьего регистра соединен с первой входной шиной первого сумматора- вычитателя, третий и четвертый инфор- мационные входы третьего регистра соединены с второй входной шиной первого сумматора-вычитателя,.которая также соединена с первым и третьим выходами третьего регистра, второй ичетвер тый выходы которого соединены t первой рходной шиной первого сумматора- вычитателя, выход которого срединен с первым информационным параллельным выходом блока, а информационный вход первого триггера соединен с первой входной шиной второго сумматора-вычитателя, выход которого соединен с вторым информационным параллельным выходом блока, причем второй, третий и четвертый входы третьего сумматора- вычитателя соединены с третьим, вторым и первым выходами соответственно первого регистра, а первый и второй входы четвертого сумматора-вычитателя соединены с вторым и первым выходами соответственно первого регистра, кроме того,обнуляющие входы всех п К-раз- рядных вычислительных модулей соединены между собой, с обнуляющим выхо- дом блока управления и с обнуляющим входом блока согласования, первый синхронизирующий вход которого соединен с первым синхронизирующим выходом блока управления и первыми синхрони- зирующими входами всех К-разрядных вычислительных модулей, вторые синхронизирующие входы которых соединены между собой, вторым синхронизирующим входом блока согласования и вторым синхронизирующим выходом блока управления, запускающий вход которого соединен с запускающими входами всех К- разрядных вычислительных модулей и

120

запускающим входом арифметического расширителя, вход внешней синхронизации которого соединен с входом внешней синхронизации блока управления, управляющий вход к орого соединен с управляющими входами блоков управления первым и вторым параллельными сумматорами и с управляющим входом арифметического расширителя, а выход останова которого соединен с выходом останова ,блока управления, причем первый и второй последовательные входы арифметического расширителя соединены с первыми входами блоков управления первым и вторым соответственно параллельными сумматорами, первая и вторая информационные входные шины арифметического расширителя соединены с первым и вторым информационными входами всех К- разрядных вычислительных модулей, первый и второй информационные последовательные входы первого К-разрядного вычислительного модуля соединены с первой и второй информационными последовательными выходными шинами блока согласования, первый и второй информационные параллельные выходы которого соединены с первой информационной выходной шиной арифметического расширителя, которая соединена с первыми информационными выходами всех К-разрядных вычислительных модулей, вторые информационные выходы которых соединены с второй информационной выходной шиной арифметического расширителя, первый и второй информационные последовательные входы каждого последующего К- разрядного вычислительного модуля соединены с первым и вторым информационными последовательными выходами соответственно предыдущего К-разрядного вычислительного модуля, третий информационный последовательный выход каждого последующего К-разрядиого вычислительного модуля соединен с третьим информационным последовательным входом предыдущего К-разрядного вычислительного модуля, четвертый и пятый информационные погледоватедрные выходы первого К-разрядного вычислительного модуля соединены с вторыми входами блоков управления первым и вторым параллельными сумматорами соответственно, а шестой информационный последовательный выход первого К-разрядного вычислительного модуля соединен с последовательно i информационной шинт блок,; согп.к о шил , первая н вторая входные шины переносов которого соединены с вторыми первым выходами положительного и отрицательного переносов первого К-разрядного вычислительного модуля соответственно, а первыр и вторые входы положительного и отрицательного переносов каждого предыдущего модуля соединены с первым и вторым соответственно выходами положительного и отрицательного переносов последующего модуля, входы управления первым и вторым параллельными сумматорами первого Кразрядного вычислительного модуля со- 15 ВЫХ°ДОМ занесения блока, начальной ус

тановки, второй информационный вход которого соединен с вторым входом пер вого элемента И и вторым входом второ го элемента И, а блок согласования 20 дополнительно содержит четвертый, пятый регистры, третий триггер, первый и второй мультиплексоры, причем второй мультиплексор имеет информационные входы с первого по четырнадцатый 25 ,и выходы с первого по седьмой, первый второй, третий и четвертый, пятый, шестой, седьмой, восьмой информационные входы первого мультиплексора соединены с первым, вторым, третьим и 30 четвертым выходами второго регистра, первым, вторым выходами пятого регист ра, выходом третьего триггера и четвертым выходом пятого регистра соответственно, обнуляющий вход когорслс соединен с обнуляющими входами третье го триггера, четвертого регистра и обнуляющим входом блока согласования, первый синхронизирующий пход которого соединен с синхронизирующими входами четвертого, пятого регистров и синхронизирующим входом третьего триггера, информационный вход которого соединен с первым информационным входом второго мультиплексора и с третьим ПЫХР- ,г дом пятого регистра, первый, второй, третий и четвертый информационные входы которого соединены соответственно с вторым, третьим, четвертым, пятым информационными входами второго мультиплексора и первым, вторым, третьим и четвертым выходами четвертого регистра, первый, второй ;третчи и четвертый информационные входы которого соединены с первым, вторым, третьим и четвертым информационными входами блока согласования соответственно, первый и второй информационные входы которого соединены с шестым и седьмым информационными входами второго

единены с входами управления первым и вторым соответственно параллельными сумматорами всех К-разрндных вычислительных модулей отличающий- с я тем, что, с целью расширения функциональных возможностей в части обеспечения операции деления, он содержит первый и второй блоки анализа, каждый из которых состоит из узла логических элементов и коммутатора, причем входная шина узла логических элементов каждого из блоков анализа соединена с первым, вторым, третьим и четвертым входами узла логических элементов, вход знака числа которого соединен с входом знака делителя блока, а первый, второй, третий и четвгр

тыи выходы узла логических элементов соединены с первым, вторым, третьим и четвертым входами коммутатора соответственно, пятый, шестой, седьмой, восьмой входы которого соединены с входной шиной сигналов управления параллельным сумматором блока, вход режима которого соединен с управляющим входом коммутатора, первый, второй, третий и четвертый выходы которого соединены с выходной шиной сигналов управления параллельными сумматорами блока, блок начал ной установки, состоящий из первого и второго элементов И, трип ера знака делителя, регистра начальной установки второго блока анализа, -сррый вход которого соединен с первым входом триггера знака делителя н с обнуляющим входом блока начальной установки, первый информационный вход которого соединен с вторым входом триггера знака делителя, третий вход которого соединен с первым входом первого элемента И, входом начального занесения блока начальной установки и первым входом второго элемента И, выход которого соединен с

вторым входом регистра начальн- -,.: тановки второго блока анализа, синхронизирующий нход которого соединен с синхронизирующим входом блока начальной установки, вхс-гт положительных и отрицательных переносов которого соединен с третьим входом регистра начальной установки второго блока анализа, выход которого соединен с выходом установки блока начальной установки, выход знака которого соединен с выходом триггера знака делителя, а выход первого элемента И соединен с

15 ВЫХ°ДОМ занесения блока, начальной ус

5

0

тановки, второй информационный вход которого соединен с вторым входом первого элемента И и вторым входом второго элемента И, а блок согласования 20 дополнительно содержит четвертый, пятый регистры, третий триггер, первый и второй мультиплексоры, причем второй мультиплексор имеет информационные входы с первого по четырнадцатый 5 ,и выходы с первого по седьмой, первый, второй, третий и четвертый, пятый, шестой, седьмой, восьмой информационные входы первого мультиплексора соединены с первым, вторым, третьим и 0 четвертым выходами второго регистра, первым, вторым выходами пятого регистра, выходом третьего триггера и четвертым выходом пятого регистра соответственно, обнуляющий вход когорслс соединен с обнуляющими входами третье го триггера, четвертого регистра и обнуляющим входом блока согласования, первый синхронизирующий пход которого соединен с синхронизирующими входами четвертого, пятого регистров и синхронизирующим входом третьего триггера, информационный вход которого соединен с первым информационным входом второго мультиплексора и с третьим ПЫХР- г дом пятого регистра, первый, второй, третий и четвертый информационные входы которого соединены соответственно с вторым, третьим, четвертым, пятым информационными входами второго мультиплексора и первым, вторым, третьим и четвертым выходами четвертого регистра, первый, второй ;третчи и четвертый информационные входы которого соединены с первым, вторым, третьим и четвертым информационными входами блока согласования соответственно, первый и второй информационные входы которого соединены с шестым и седьмым информационными входами второго

0

23156

мультиплексора, восьмой, девятый, десятый, одиннадцатый и двенадцатый информационные входы которого соединены с первым, вторым, третьим выходами третьего сумматора-вычитателя, пер- вым, вторым выходами четвертого сумматора-вычитателя соответственно, тринадцатый информационный вход второго мультиплексора соединен с шиной нуля, четырнадцатый информационный вход второго мультиплексора соединен с пятым информационным входом блока согласования, вход режима которого соединен с входами управления первого и второго мультиплексоров, первый, второй, четвертый, шестой и третий, пятый, седьмой выходы второго мультиплексора соединены с второй и первой входной шинами соответственно второго сумматора-вычитателя, а первый, второй, третий и четвертый выходы первого мультиплексора соединены.с третьим, вторым, четвертым информационными входами треть§го регистра и информационным входом первого триггер а соответственно, блок управления дополнительно содержит третий элемелт задержки и узел совпадения, причем вход третьего элемента задержки соединен с выходом формирователя импульсов, а выход соединен с входом первого элемента задержки и с первым входом узла совпадения соответственно, второй вход которого соединен с входом режима блока управления, а выход узла совпадения соединен с выходом начального занесения блока управления, который соединен с входом начального занесения блока начальной установки, первый информационный вход которого соединен с первой информационной шиной арифметического расширителя, вторая информационная шина которого соединена с вто

5

20

34

0

25

30

35

40

124

рым информационным входом блока начальной установки, обнуляющий, синхронизирующий входы и вход положительного и отрицательного переносов которого соединены с обнуляющим, первым синхронизирующим выходами блока управления и первой входной шиной переносов блока согласования соответственно, а выход занесения блока начальной установки соединен с установочными входами всех К-разрядных ных модулей, выход знака начальной установки соединен с входами знака делителя обоих блоков анализа, а выход установки блока начальной установки соединен с входной информационной шиной второго блока анализа, входная информационная шина первого блока анализа соединена с первым выходом положительного и отрицательного переносов первого К-разрядного вычислительного модуля, входы управления вторым и первым параллельными сумматорами которого соединены с третьим и четвертым, первым и вторым соответственно информационными входами блока согласования и с выходными шинами сигналов управления параллельными сумматорами первого и второго соответственно блоков анализа, входные шины сигнала управления параллельными сумматорами которых соединены с выходами блоков управления вторым и первым параллельными сумматорами соответственно, входы режима обоих блоков анализа соединены между собой, с входом режима арифметического расширителя, входом режима блока управления и входом режима блока согласования, а пятый информационный вход блока согласования соединен с первой информационной выходной шиной первого К-разрядного вычислительного модуля.

Таблица 1

Коды входных сигналов блока логических элементов

0(1)0(1)(3(1)0(1)О

10 1

О1 О

0(1)0(1) 101

0(1)0(1) 01О

Таблица 2

Коды выходных сигналов блока логических элементов

г О

1 1

1 1

1

О При О

о о

фиг.З

e99si

/tfo

Фиг. 6

| Устройство для умножения п-разрядных чисел,представленных последовательным кодом | 1975 |

|

SU631919A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1981 |

|

SU1005035A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1984 |

|

SU1256016A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-23—Публикация

1988-07-31—Подача