1

Изобретение относится к цифровой вычислительной технике и может быть использовано в управляющих, моделирующих и вычислительных машинах как арифметический расширитель.

Цель изобретения - повышение быстродействия устройства.

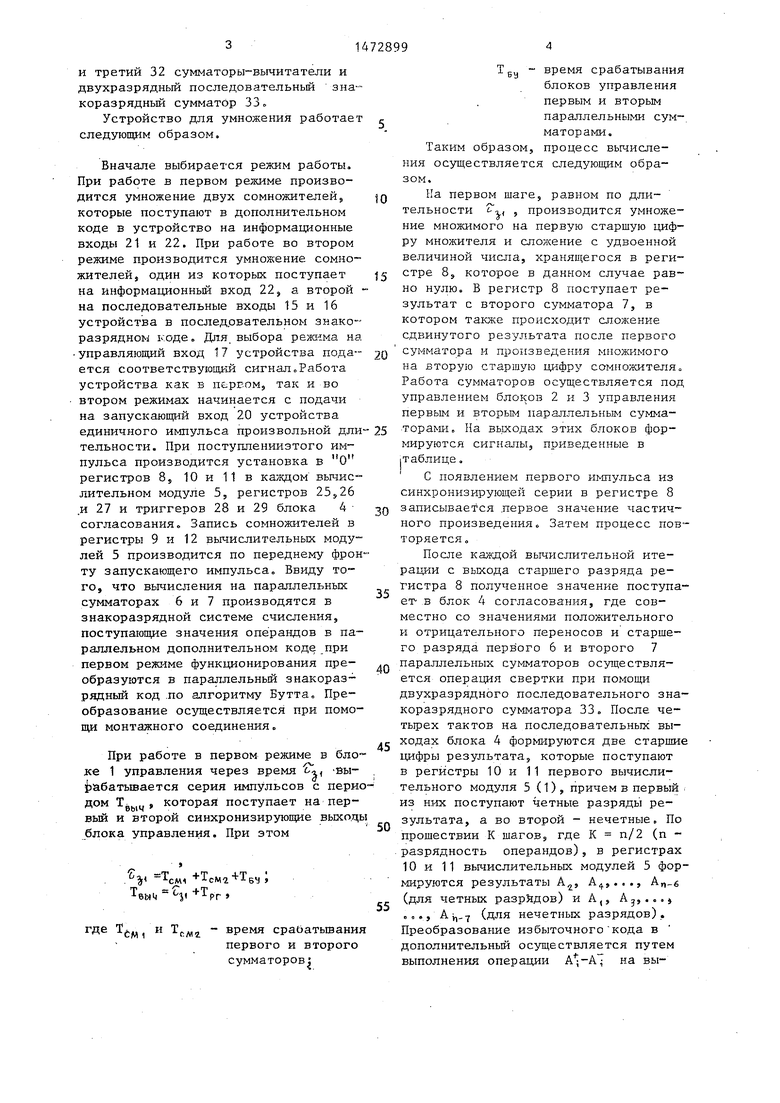

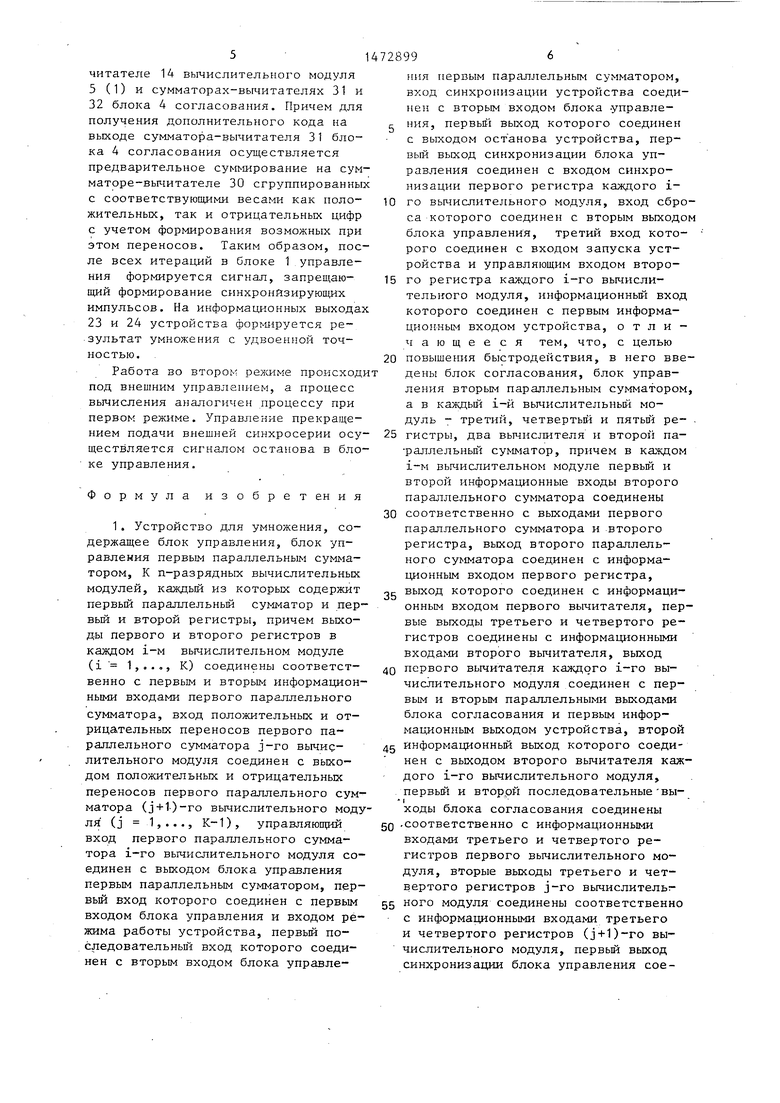

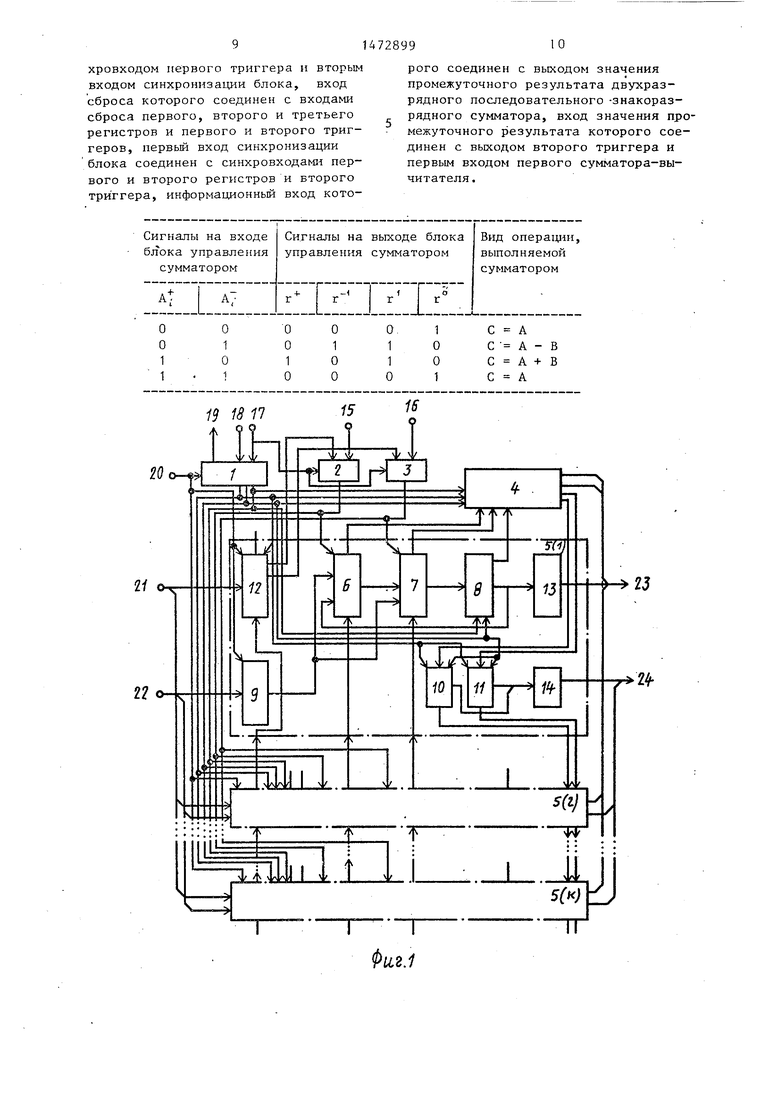

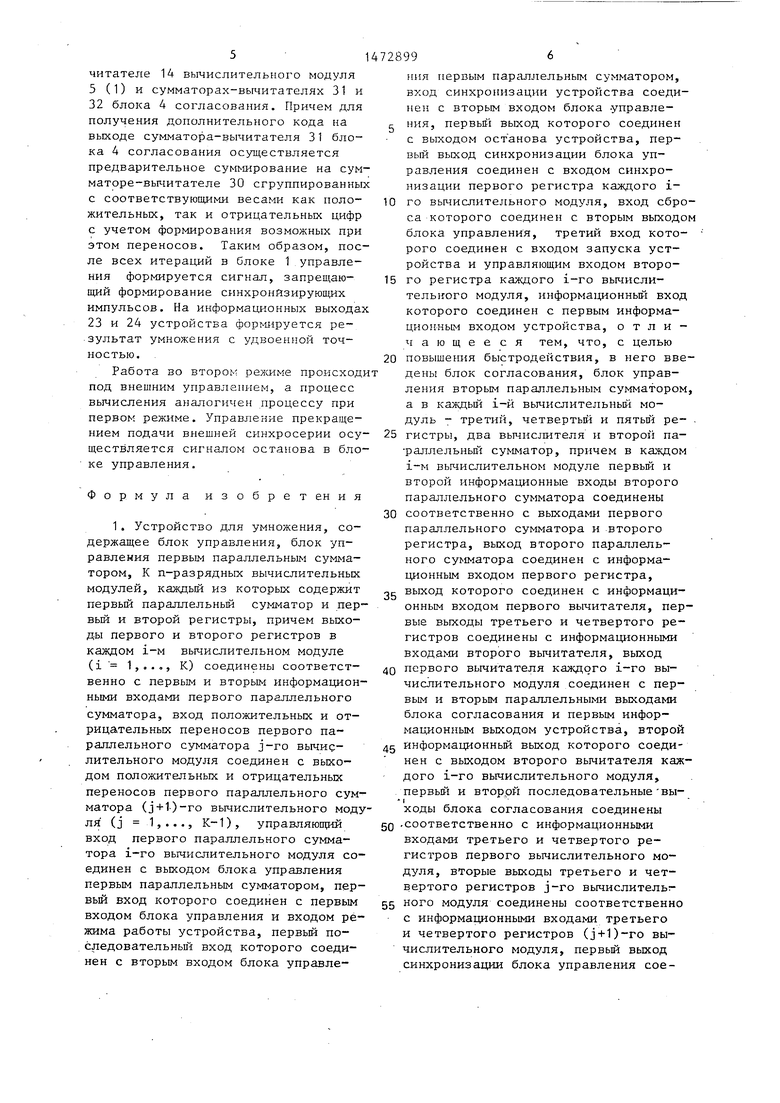

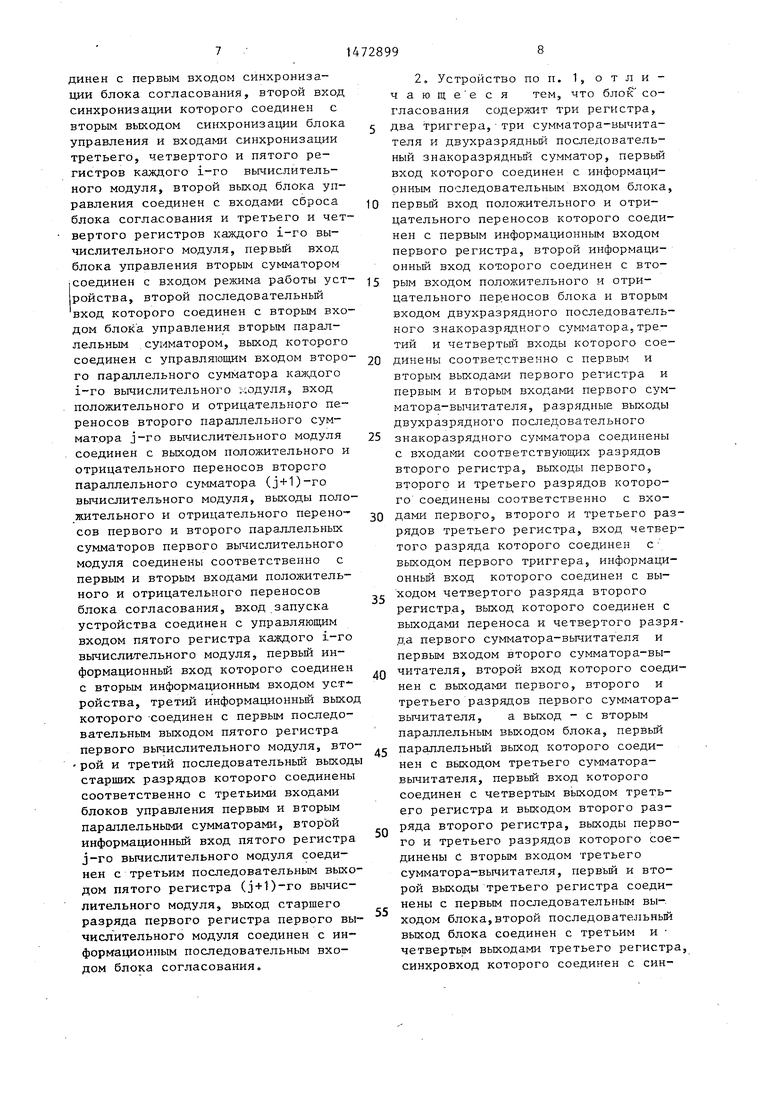

На фиг.1 изображена функциональная схема устройства для умноженияJ на фиг.2 - функциональная схема блока согласования; на фиг.З - временные диаграммы работы устройства.

Устройство для умножения (фиг.1) содержит блок 1 управления, блоки 2 и 3 управления первым и вторым параллельными сумматорами соответственно блок 4 согласования и К

n-разрядных вычислительных модулей 5, каждый из которых содержит первый 6 и второй 7 параллельные сумматоры, с первого по пятый регистры 8-12 и первый 13 и второй 14 вычи- татели, первый 15 и второй 16 последовательные входы устройства, управляющие входы 17 режима работы, 18 синхронизации, 19 останова и 20 запуска устройства, первый 21 и второй 22 информационные входы устройства и первьй 23 и второй 24 информационные выходы устройства.

Блок 4 согласования (фиг.2) содержит первый 25, второй 26 и третий 27 регистры, первый 28 и второй 29 триггеры, первый 30, второй 31

Ј

vl to

00

со со

и третий 32 сумматоры-вычитатели и двухразрядный последовательный зна- коразрядный сумматор 33

Устройство для умножения работает следующим образом.

Вначале выбирается режим работы. При работе в первом режиме производится умножение двух сомножителей, которые поступают в дополнительном коде в устройство на информационные входы 21 и 22. При работе во втором режиме производится умножение сомножителе один из которых поступает на информационный вход 22, а второй на последовательные входы 15 и 16 устройства в последовательном знако- разрядном коде. Для выбора режима на управляющий вход 17 устройства пода- ется соответствующий сигнал.Работа устройства как в пергом, так и во втором режимах начинается с подачи на запускающий вход 20 устройства единичного импульса произвольной дли тельности. При поступленииэтого импульса производится установка в О регистров 8, 10 и 11 в каждом вычислительном модуле 5, регистров 25,26 ,и 27 и триггеров 28 и 29 блока 4 согласования. Запись сомножителей в регистры 9 и 12 вычислительных модулей 5 производится по переднему фронту запускающего импульса. Ввиду того, что вычисления на параллельных сумматорах 6 и 7 производятся в знакоразрядной системе счисления, поступающие значения операндов в параллельном дополнительном коде при первом режиме функционирования пре- образуются в параллельный знакораз- рядный код по алгоритму Бутта. Преобразование осуществляется при помощи монтажного соединения.

При работе в первом режиме в блоке 1 управления через время ь, Вырабатывается серия импульсов с периодом Т , которая поступает на пер

вый и второй синхронизирующие выхоцы блока управления. При этом

6$ TCMI +тсм г+ТбЧ J Твы4 Ч

Тсм f и Tf д,г - время срабатывания первого и второго

сумматоров:

Q 5 0 5 0

5

5

0

5

Т БЬ - время срабатывания блоков управления первым и вторым параллельными сумматорами.

Таким образом, процесс вычисления осуществляется следующим образом.

На первом шаге, равном по длительности ьу , производится умножение множимого на первую старшую цифру множителя и сложение с удвоенной величиной числа, хранящегося в регистре 8, которое в данном случае равно нулю. В регистр 8 поступает результат с второго сумматора 7, в котором также происходит сложение сдвинутого результата после первого сумматора и произведения множимого на вторую старшую цифру сомножителя. Работа сумматоров осуществляется под управлением блоков 2 и 3 управления первым и вторым параллельным сумматорами. На выходах этих блоков формируются сигналы, приведенные в таблице.

С появлением первого импульса из синхронизирующей серии в регистре 8 записывается первое значение частичного произведения. Затем процесс повторяется „

После каждой вычислительной итерации с выхода старшего разряда регистра 8 полученное значение поступает в блок 4 согласования, где совместно со значениями положительного и отрицательного переносов и старшего разряда первого 6 и второго 7 параллельных сумматоров осуществляется операция свертки при помощи двухразрядного последовательного зна- коразрядного сумматора 33. После четырех тактов на последовательных выходах блока 4 формируются две старшие цифры результата, которые поступают в регистры 10 и 11 первого вычислительного модуля 5(1), причем в первый из них поступают четные разряды результата, а во второй - нечетные. По прошествии К шагов, где К п/2 (п - разрядность операндов), в регистрах 10 и 11 вычислительных модулей 5 формируются результаты А2, А4,..., (для четных разрядов) и А(, А,... ,,., (для нечетных разрядов). Преобразование избыточного кода в дополнительный осуществляется путем выполнения операции на вы

5

читателе 14 вычислительного модуля 5 (1) и сумматорах-вычитателях 31 и 32 блока 4 согласования. Причем для получения дополнительного кода на выходе сумматора-вычитателя 31 блока 4 согласования осуществляется предварительное суммирование на сум маторе-вычитателе 30 сгруппированны с соответствующими весами как положительных, так и отрицательных цифр с учетом формирования возможных при этом переносов. Таким образом, после всех итераций в блоке 1 управления формируется сигнал, запрещающий формирование синхронизирующих импульсов. На информационных выходах 23 и 24 устройства формируется результат умножения с удвоенной точностью.

Работа во второе режиме происход под внешним управлением, а процесс вычисления аналогичен процессу при первом режиме. Управление прекращением подачи внешней синхросерии осуществляется сигналом останова в блоке управления.

Формула изобретения

1. Устройство для умножения, содержащее блок управления, блок управления первым параллельным сумматором, К n-разрядных вычислительных модулей, каждый из которых содержит первый параллельный сумматор и первый и второй регистры, причем выходы первого и второго регистров в каждом i-м вычислительном модуле (i 1,..., К) соединены соответственно с первым и вторым информационными входами первого параллельного сумматора, вход положительных и отрицательных переносов первого параллельного сумматора j-ro вычислительного модуля соединен с выходом положительных и отрицательных переносов первого параллельного сумматора (j+1)-ro вычислительного модуля (j 1,..., К-1), управляющий вход первого параллельного сумматора 1-го вычислительного модуля соединен с выходом блока управления первым параллельным сумматором, первый вход которого соединен с первым входом блока управления и входом режима работы устройства, первый последовательный вход которого соединен с вторым входом блока управле0

5

0

ния первым параллельным сумматором, вход синхронизации устройства соединен с вторым входом блока -управления, первый выход которого соединен с выходом останова устройства, первый выход синхронизации блока управления соединен с входом синхронизации первого регистра каждого i- го вычислительного модуля, вход сброса которого соединен с вторым выходом блока управления, третий вход которого соединен с входом запуска устройства и управляющим входом второго регистра каждого 1-го вычислительного модуля, информационный вход которого соединен с первым информационным входом устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены блок согласования, блок управления вторым параллельным сумматором, а в каждый i-й вычислительный модуль - третий, четвертый и пятый ре5 гистры, два вычислителя и второй параллельный сумматор, причем в каждом iм вычислительном модуле первый и второй информационные входы второго параллельного сумматора соединены

0 соответственно с выходами первого параллельного сумматора и второго регистра, выход второго параллельного сумматора соединен с информационным входом первого регистра,

g выход которого соединен с информационным входом первого вычитателя, первые выходы третьего и четвертого регистров соединены с информационными входами второго вычитателя, выход

о первого вычитателя каждого 1-го вычислительного модуля соединен с первым и вторым параллельными выходами блока согласования и первым информационным выходом устройства, второй

5 информационный выход которого соединен с выходом второго вычитателя каждого 1-го вычислительного модуля,

первый и второй последовательные вы- i ходы блока согласования соединены

0 -соответственно с информационными входами третьего и четвертого регистров первого вычислительного модуля, вторые выходы третьего и четвертого регистров j-ro вычислительг5 кого модуля соединены соответственно с информационными входами третьего и четвертого регистров (j+1)-ro вычислительного модуля, первый выход синхронизации блока управления соединен с первым входом синхронизации блока согласования, второй вход синхронизации которого соединен с вторым выходом синхронизации блока управления и входами синхронизации третьего, четвертого и пятого регистров каждого 1-го вычислительного модуля, второй выход блока управления соединен с входами сброса блока согласования и третьего и четвертого регистров каждого 1-го вычислительного модуля, первьй вход блока управления вторым сумматором соединен с входом режима работы устройства, второй последовательньй вход которого соединен с вторым входом блока управления вторым параллельным сумматором, выход которого соединен с управляющим входом второго параллельного сумматора каждого 1-го вычислительного ..одуля, вход положительного и отрицательного переносов второго параллельного сумматора j-го вычислительного модуля соединен с выходом положительного и отрицательного переносов второго параллельного сумматора (j+1)-ro вычислительного модуля, выходы положительного и отрицательного перено-- сов первого и второго параллельных сумматоров первого вычислительного модуля соединены соответственно с первым и вторым входами положительного и отрицательного переносов блока согласования, вход запуска устройства соединен с управляющим входом пятого регистра каждого 1-го вычислительного модуля, первьй информационный вход которого соединен с вторым информационным входом уст-1- ройства, третий информационный выхо которого соединен с первым последовательным выходом пятого регистра первого вычислительного модуля, второй и третий последовательный выход старших разрядов которого соединены соответственно с третьими входами блоков управления первым и вторым параллельными сумматорами, второй информационный вход пятого регистра j-ro вычислительного модуля соединен с третьим последовательным выходом пятого регистра (j+1)ro вычислительного модуля, выход старшего разряда первого регистра первого вычислительного модуля соединен с информационным последовательным входом блока согласования.

0

5

0

5

0

5

0

5

0

5

2, Устройство по п. 1, отличающееся тем, что блок согласования содержит три регистра, два триггера, три сумматора-вычита- теля и двухразрядньй последовательный знакоразрядный сумматор, первьй вход которого соединен с информационным последовательным входом блока, первьй вход положительного и отрицательного переносов которого соединен с первым информационным входом первого регистра, второй информаци- онньй вход которого соединен с вторым входом положительного и отрицательного переносов блока и вторым входом двухразрядного последовательного знакоразрядного сумматора,третий и четвертый входы которого соединены соответственно с первым и вторым выходами первого регистра и первым и вторым входами первого сум- матора-вычитателя, разрядные выходы двухразрядного последовательного знакоразрядного сумматора соединены с входами соответствующих разрядов второго регистра, выходы первого, второго и третьего разрядов которого соединены соответственно с входами первого, второго и третьего разрядов третьего регистра, вход четвертого разряда которого соединен с выходом первого триггера, информационный вход которого соединен с выходом четвертого разряда второго регистра, выход которого соединен с выходами переноса и четвертого разряда первого сумматора-вычитателя и первым входом второго сумматора-вычитателя, второй вход которого соединен с выходами первого, второго и третьего разрядов первого сумматора- вычитателя, а выход - с вторым параллельным выходом блока, первьй параллельный выход которого соединен с выходом третьего сумматора- вычитателя, первьй вход которого соединен с четвертым выходом третьего регистра и выходом второго разряда второго регистра, выходы первого и третьего разрядов которого соединены с вторым входом третьего сумматора-вычитателя, первьй и второй выходы третьего регистра соединены с первым последовательным выходом блока,второй последовательньй выход блока соединен с третьим и четвертым выходами третьего регистра, синхровход которого соединен с синхровходом первого триггера и вторым входом синхронизации блока, вход сброса которого соединен с входами сброса первого, второго и третьего регистров и первого и второго триггеров, первый вход синхронизации блока соединен с синхровходами первого и второго регистров и второго триггера, информационный вход которого соединен с выходом значения промежуточного результата двухразрядного последовательного -знакораз- рядного сумматора, вход значения промежуточного результата которого соединен с выходом второго триггера и первым входом первого сумматора-вы- читателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметический расширитель | 1988 |

|

SU1566341A1 |

| Арифметический расширитель | 1989 |

|

SU1661758A1 |

| Устройство для умножения | 1984 |

|

SU1256016A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1988 |

|

SU1640709A1 |

| Устройство для умножения | 1989 |

|

SU1612295A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для умножения | 1979 |

|

SU868751A1 |

| Устройство для умножения | 1981 |

|

SU1012245A1 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано в управляющих, моделирующих и вычислительных машинах как арифметический расширитель. Цель изобретения - повышение быстродействия - достигается введением в устройство для умножения, содержащее блок управления, блок управления первым параллельным сумматором, К N-разрядных вычислительных модулей, каждый из которых содержит первый параллельный сумматор и два регистра, блоков согласования и управления вторым параллельным сумматором, а в каждый вычислительный модуль - трех регистров, двух вычитателей и второго параллельного сумматора, что дает возможность организовать умножение знакоразрядных сомножителей способом умножения на два разряда множителя с удвоенной точностью. 1 табл., 1 з.п.ф-лы, 3 ил.

Фм.1

26

27

J

Т

32

-

50

3

| Устройство для умножения | 1981 |

|

SU1005035A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 12560316, кл, G 06 F 7/49, 1984. | |||

Авторы

Даты

1989-04-15—Публикация

1987-08-19—Подача