Изобретение относится к цифровой вычислительной технике, в частности к вычислительным системам со знако- разрядным кодированием информации, и может быть использовано в управляющих, моделирующих и вычислительных машинах в качестве сопроцессора для

выполнения операций умножения, деле- фЙя и извлечения корня.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения вычисления квадратного корня.

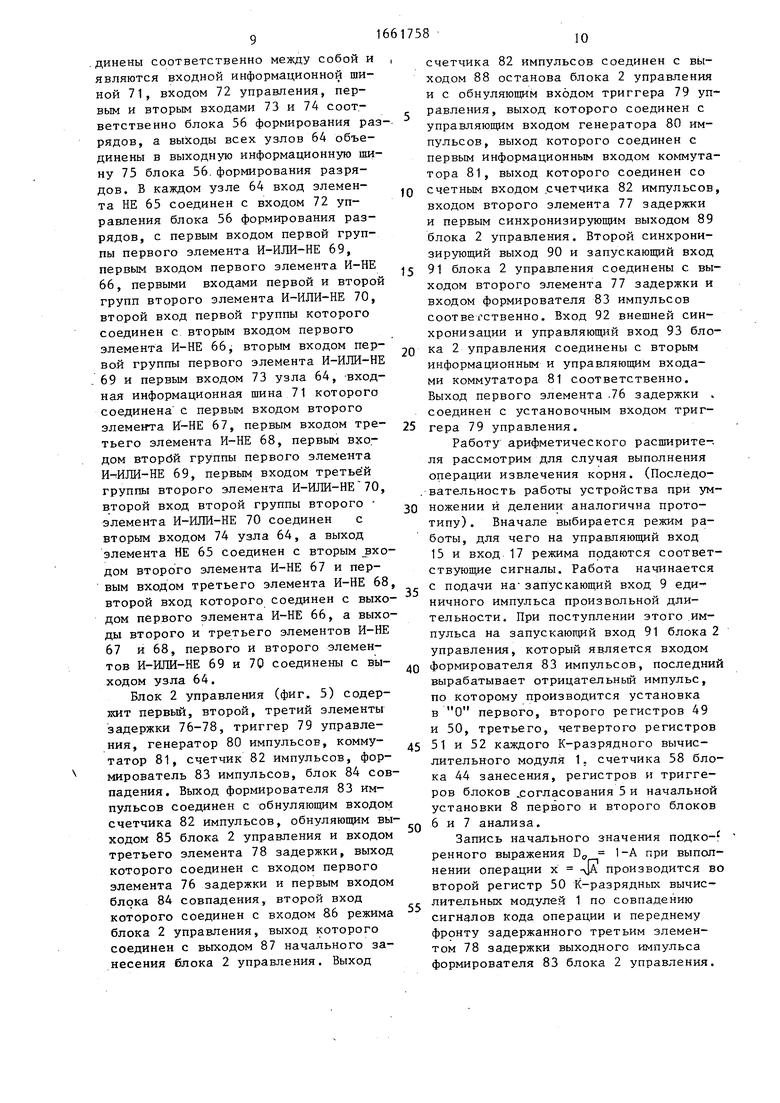

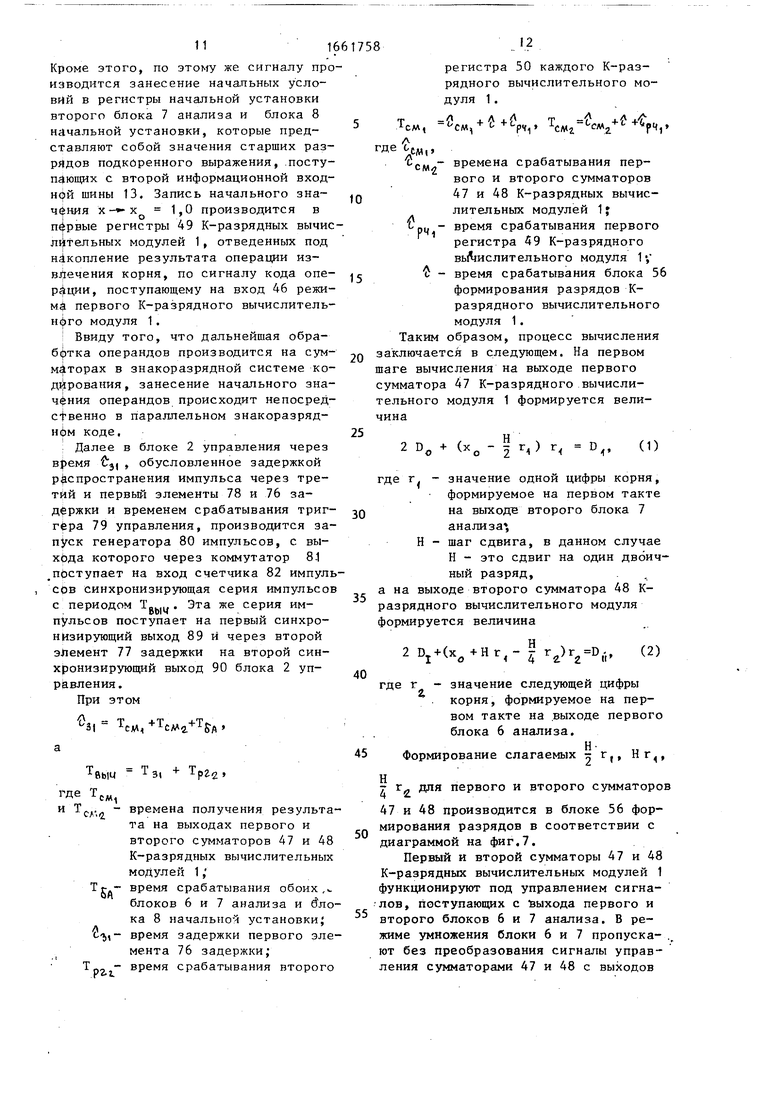

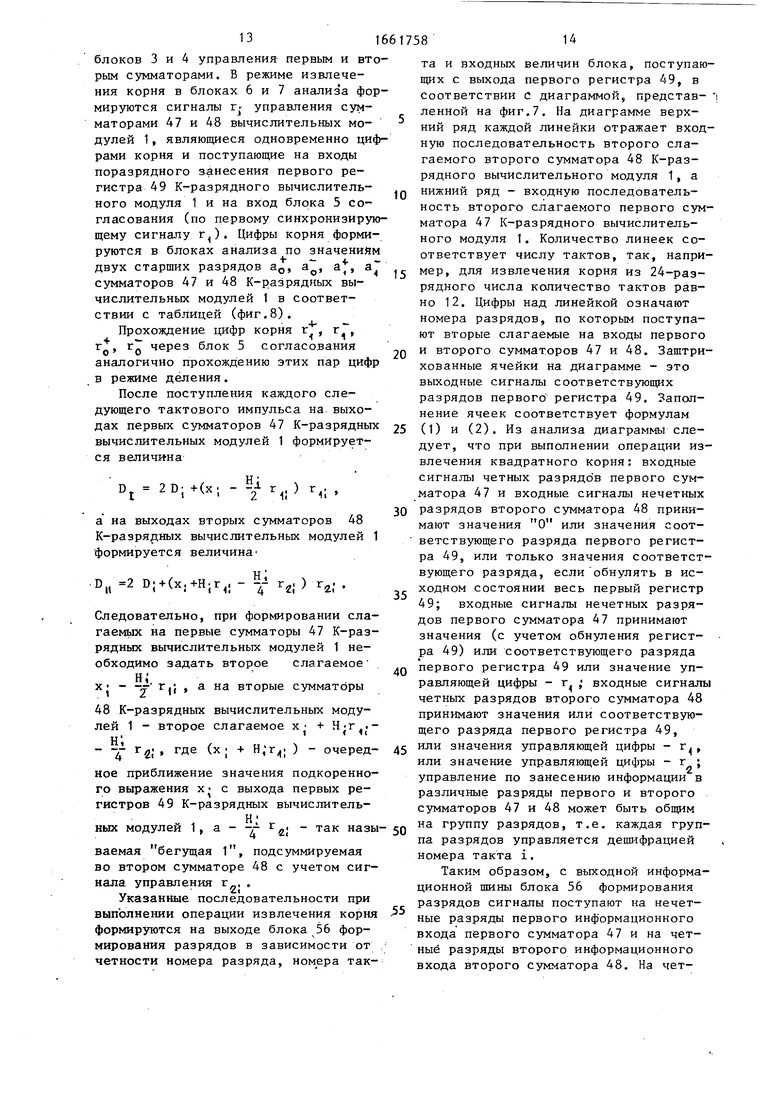

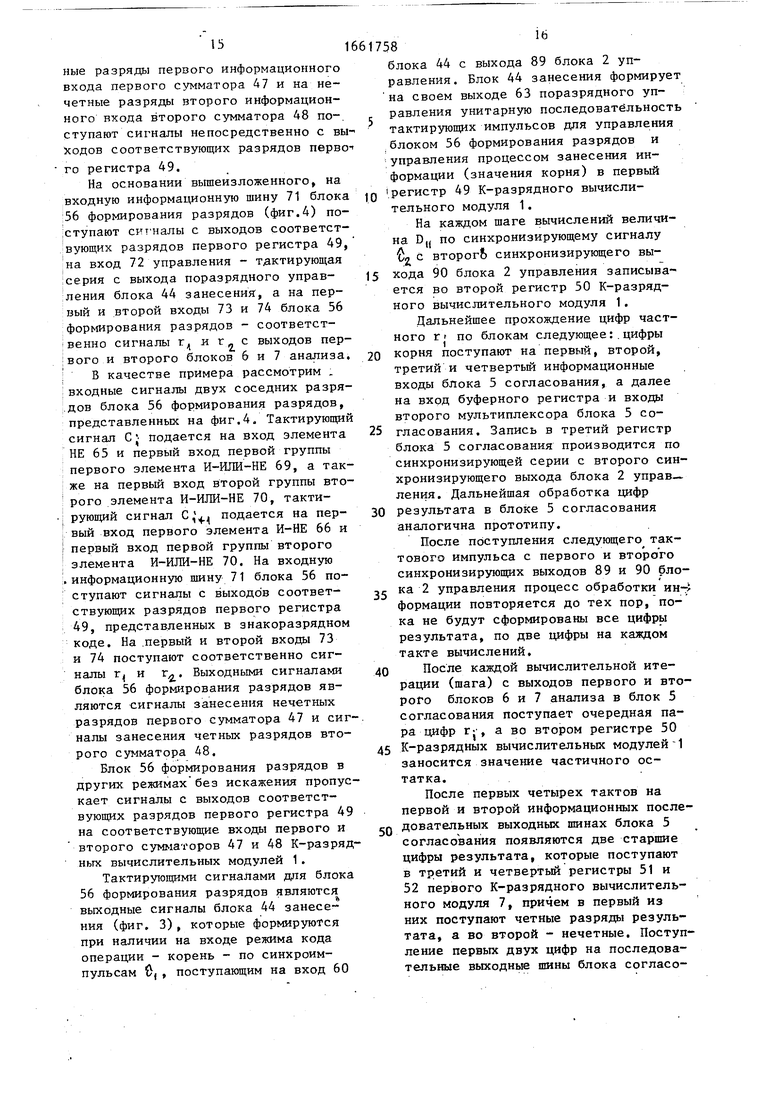

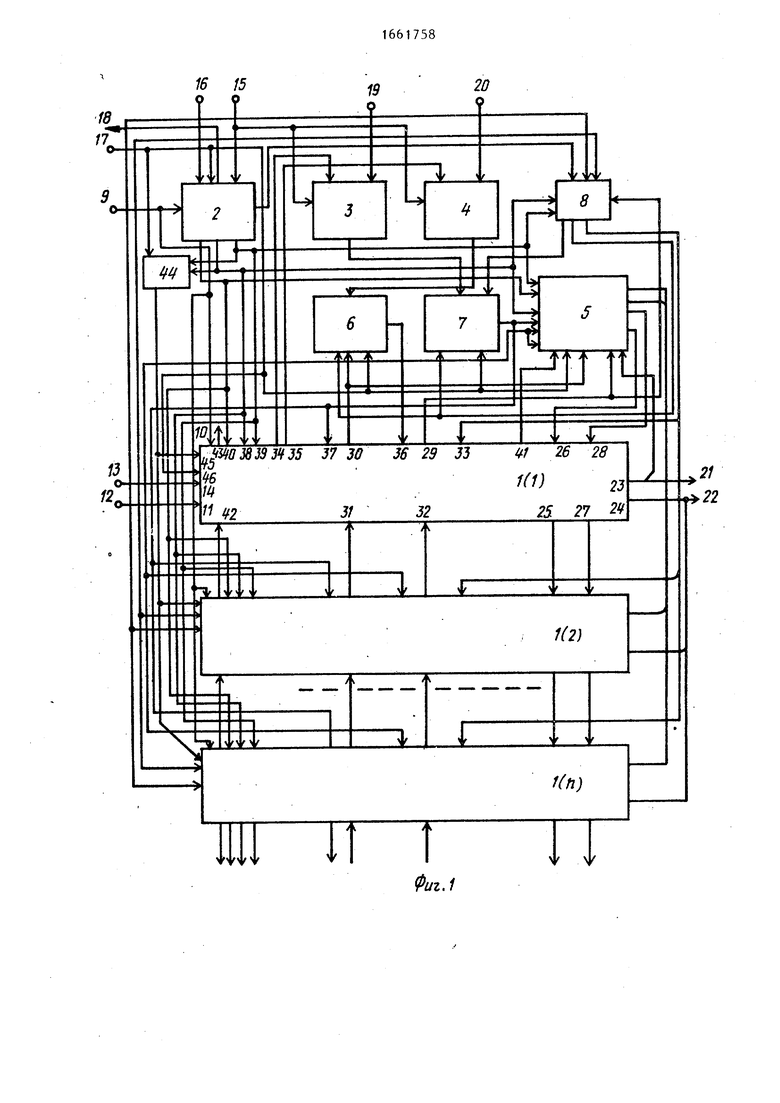

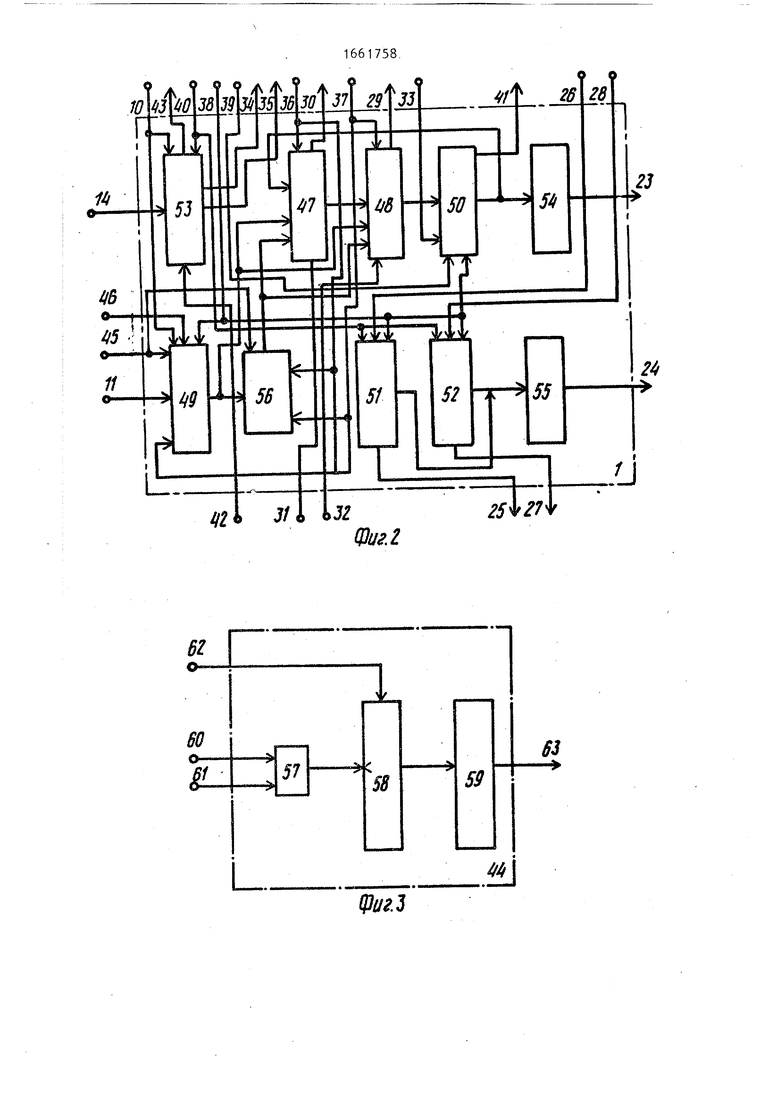

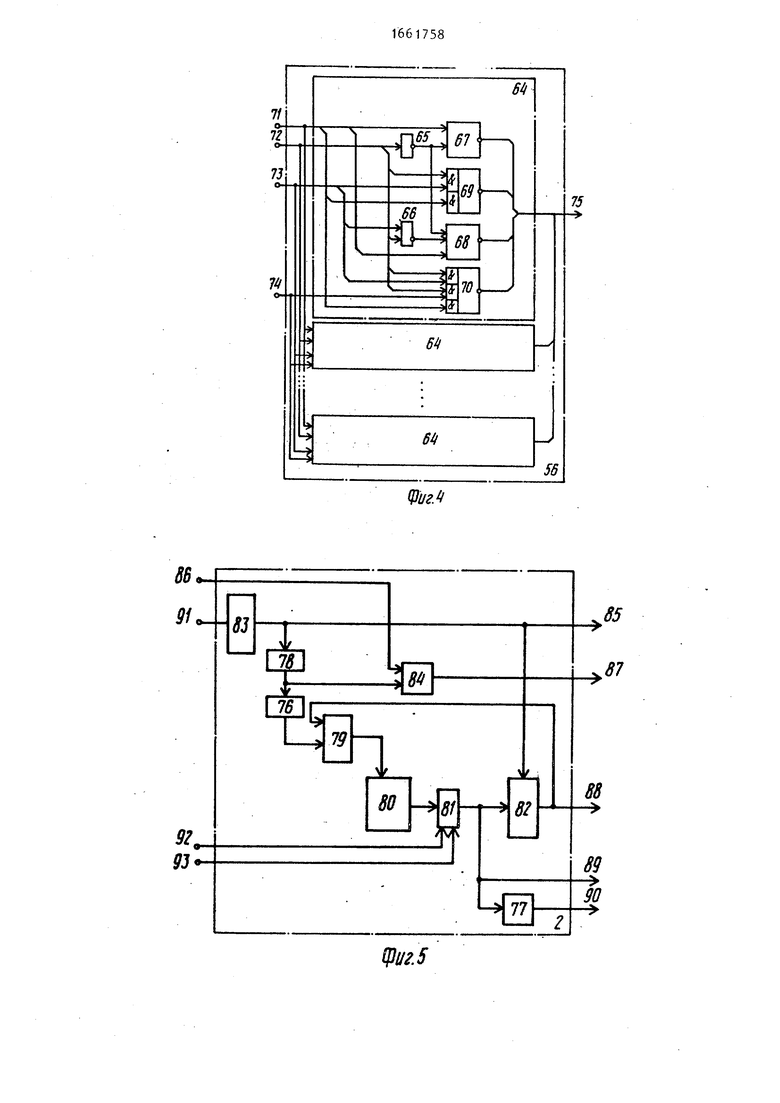

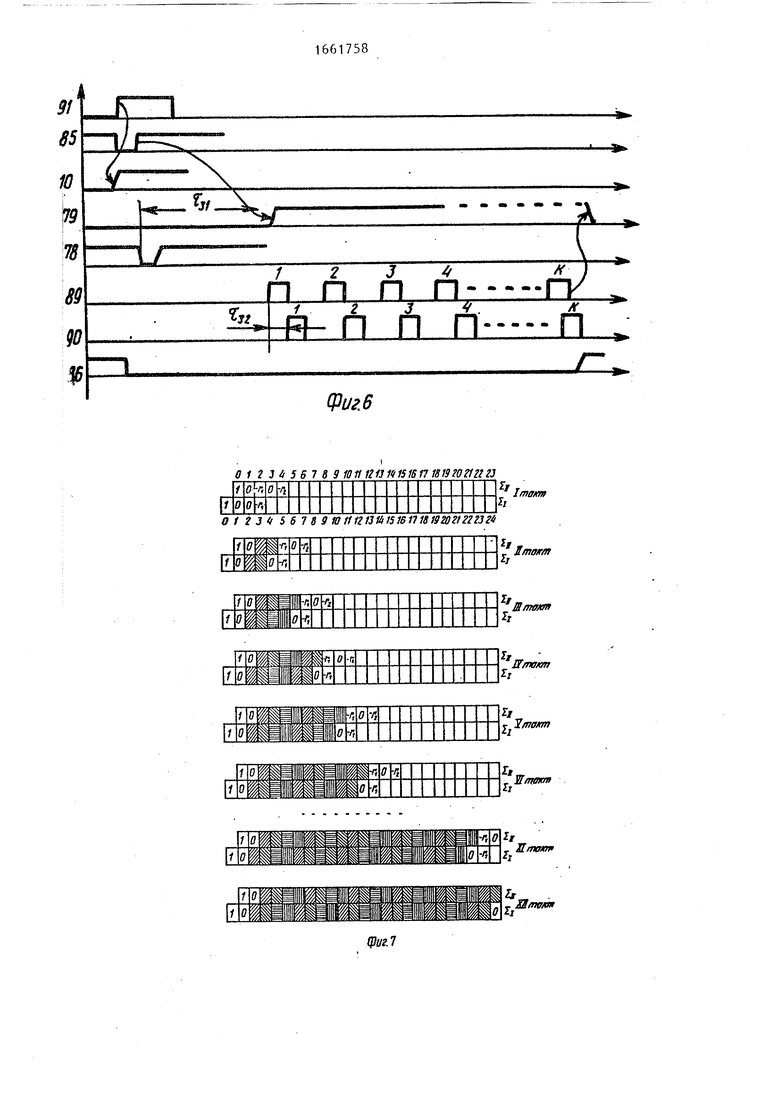

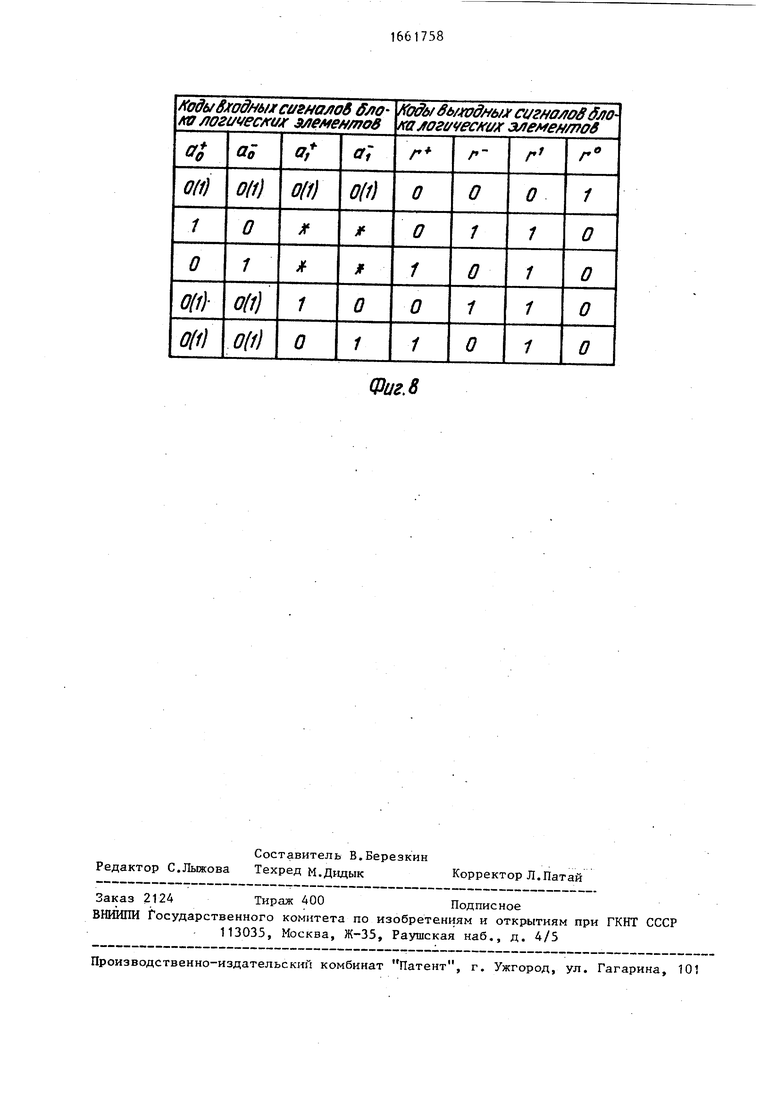

На фиг.1 изображена блок-схема арифметического расширителя; на фиг.2 - блок-схема К-разрядного вы- числич.льного модуля; на фиг.З - блок-схема блока занесения; на фиг.4- блок-схема блока формирования разрядов; на фиг.З - блок-схема блока управления-, на фиг.6 - временные диаграммы работы; на фиг.7 - диаграмма функционирования блока формирования разрядов; на фиг.8 - таблица, где представлена логика работы блока анализа при формировании цифр результата при выполнении операции вычисления квадратного корня.

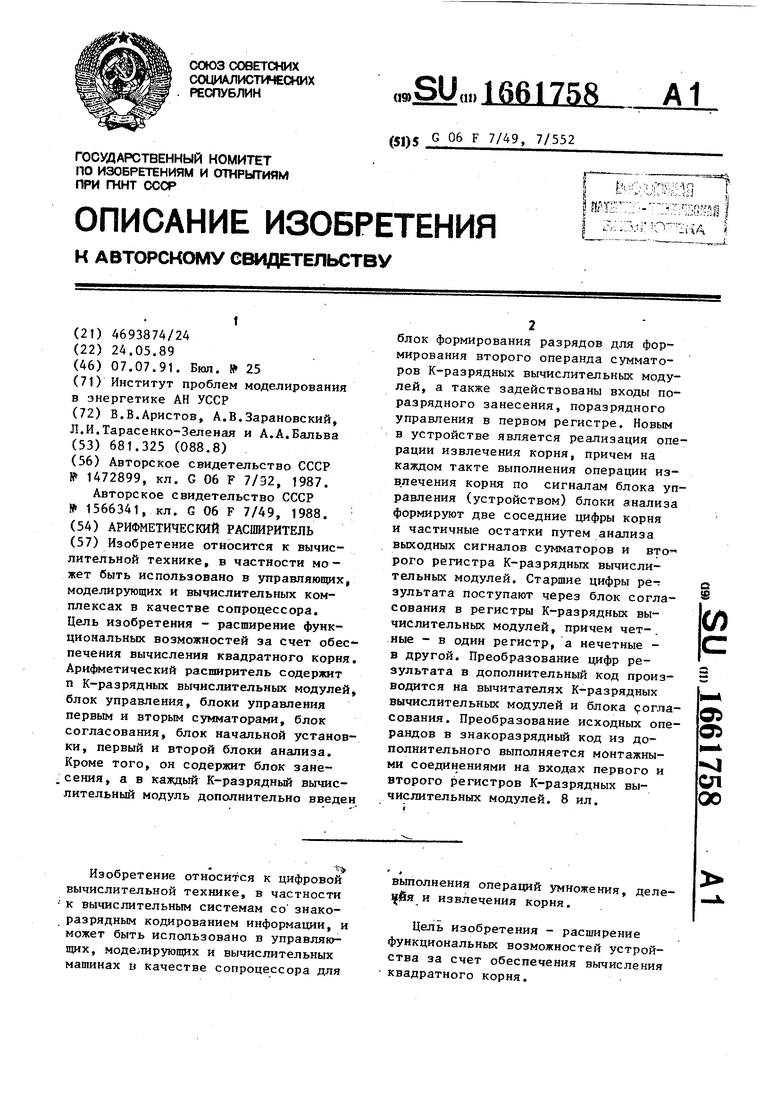

Арифметический расширитель (фиг.1) содержит п К-разрядных вычислительных модулей 1, блок 2 управления, блок 3 управления первым сумматором, блок 4 управления вторым сумматором, блок 5 согласования, первый 6 и второй 7 блоки анализа, блок 8 начальной установки, причем запускающий вход 9 устройства соединен с запускающим входом блока 2 управления и с запускающими входами 10 всех К-разрядных вычислительных модулей, первые информационные входы 11 которых соединены между собой, с первым информационным входом блока 8 начальной установки и первой информационной ; входной шиной 12, вторая информационная входная шина 13 соединена с вторым информационным входом 14 каждого из К-разрядных вычислительных модулей и вторым информационным входом блока 8 начальной установки, вхо начального занесения которого соединен с выходом начального занесения блока 2 управления, управляющий вход которого соединен с управляющим входом 15, расширителя, вход внешней синхронизации 16 которого соединен с входом внешней синхронизации блока 2 управления, вход режима которого соединен с входами режима первого 6 и второго 7 блоков анализа и блока 5 согласования, а также с входом 17 режима, выход 18 останова соединен с выходом останова блока 2 управления , первый 19 и второй 20 последовательные входы соединены с первыми ; входами блоков 3 и 4 управления первым и вторым соответственно сумматорами, а первая и вторая информационные выходные шины 21 и 22 соединены с первым, вторым параллельными выходами блока 5 согласования, пер

0

5

0

5

0

5

0

5

выми информационными выходами 23 всех К-разрядных вычислительных модулей 1 и вторыми информационными выходами 24 всех К-разрядных вычислительных модулей 1 соответственно, первый информационный последовательный выход 25 каждого предыдущего К-разрядного вычислительного модуля 1 соединен с первым информационным последовательным входом 26 каждого последующего К-разрядного вычислительного модуля, второй информационный последовательный выход 27 каждого предыдущего К-разрядного вычислительного модуля 1 соединен с вторым информационным последовательным входом 28 каждого последующего К-раэрядного модуля, а первый и второй информационные последовательные коды первого К-раэрядного вычислительного модуля соединены с первой и второй соответственно информационными последовательными выходными шинами блока 5 согласования, первая и вторая входные шины переносов которого соединены с входом положительного и отрицательного переносов блока 8 начальной установки, вторым выходом 29 положительного и отрицательного переносов первого К-разрядного вычислительного модуля и входной шиной блока логических элементов первого блока 6 анализа, первым выходом 30 положительного и отрицательного переносов первого К-разрядного вычислительного модуля 1 соответственно, первый 31 и второй 32 входы положительного и отрицательного переносов каждого предыдущего К-разрядного вычислительного модуля 1 соединены с первым и вторым соответственно выходами положительного и отрицательного переносов каждого последующего К-разрядного вычислительного модуля 1, установочные входы 33 всех К-разрядных вычислительных модулей 1 соединены между собой и с выходом занесения блока 8 начальной установки, выход знака которого соединен с входами знака делителя обоих блоков 6 и 7 анализа, входные шины сигналов управления сумматорами первого 6 и второго 7 блоков анализа соединены с выходами блоков управления вторым и первым соответственно сумматорами 4 и 3, управляющие входы блоков управления первым 3 и вторым 4 сумматорами сое5

динены между собой и с управляющим входом 15, вторые входы блоков управления первым 3 и вторым 4 сумматорами соединены с четвертым 34 и пятым 35 соответственно информационными последовательными выходами первого К-разрядного вычислительного модуля 1, вход 36 управления вторым сумматором которого соединен с выходной шиной сигналов управления сумматорами первого блока 6 анализа, с входами управления вторым сумматором всех К-разрядных вычислительных модулей 1 и с первым и вторым информационными входами блока 5 согласования, а вход 37 управления первым сумматором которого соединен с выходной шиной сигналов управления сумматорами второго блока 7 анализа, с входами управления первым сумматором всех К-разрядных вычислителъных мо- дулей 1 и с третьим и четвертым информационными входами блока 5 согласования, обнуляющий вход которого соединен с обнуляющим входом блока 8 начальной установки, обнуляющими входами 38 всех К-разрядных вычислительных модулей 1 и обнуляющим выходом блока 2 управления, первый синхронизирующий выход которого соединен с первым синхронизирующим входом 39 всех К-разрядных вычислительных модулей 1, синхронизирующим входом блока 8 начальной установки и первым синхронизирующим входом блока 5 согласования, второй синхронизирующий вход которого соединен с вторым синхронизирующим выходом блока 2 управления и вторыми синхронизирующими входами 40 всех К-разрядных вычислительных модулей 1, выход блока 8 начальной установки соединен с входной шиной блока логических элементов второго блока 6 анализа, последовательная входная информационная шина блока 5 согласования соединена с шестым информационным последовательным выходом 41 первого К-разрядного вычислительного модуля 1, третий информационный последовательный вход 42 каждого предыдущего К-разрядного вычислительного модуля соединен с третьим информационным последовательным выходом 43 последующего К-разрядного вычислительного модуля 1, а пятый информационный вход блока 5 согласования соединен с первой информационной выходной шиной 21 пер17586

вого К-разрядного вычислительного модуля. Кроме того, арифметический расширитель содержит блок 44 занесе- е ния, вход режима которого соединен с входом 17 режима, синхронизирующий и обнуляющий входы блока 44 занесения соединены с первым синхронизирующим

и обнуляющим выходами соответственно блока 2 управления, а выход поразрядного управления блока 44 занесения соединен с входами 45 поразрядного управления всех К-разрядных вычислительных модулей 1, вход 46

режима первого из которых соединен с входом 17 режима.

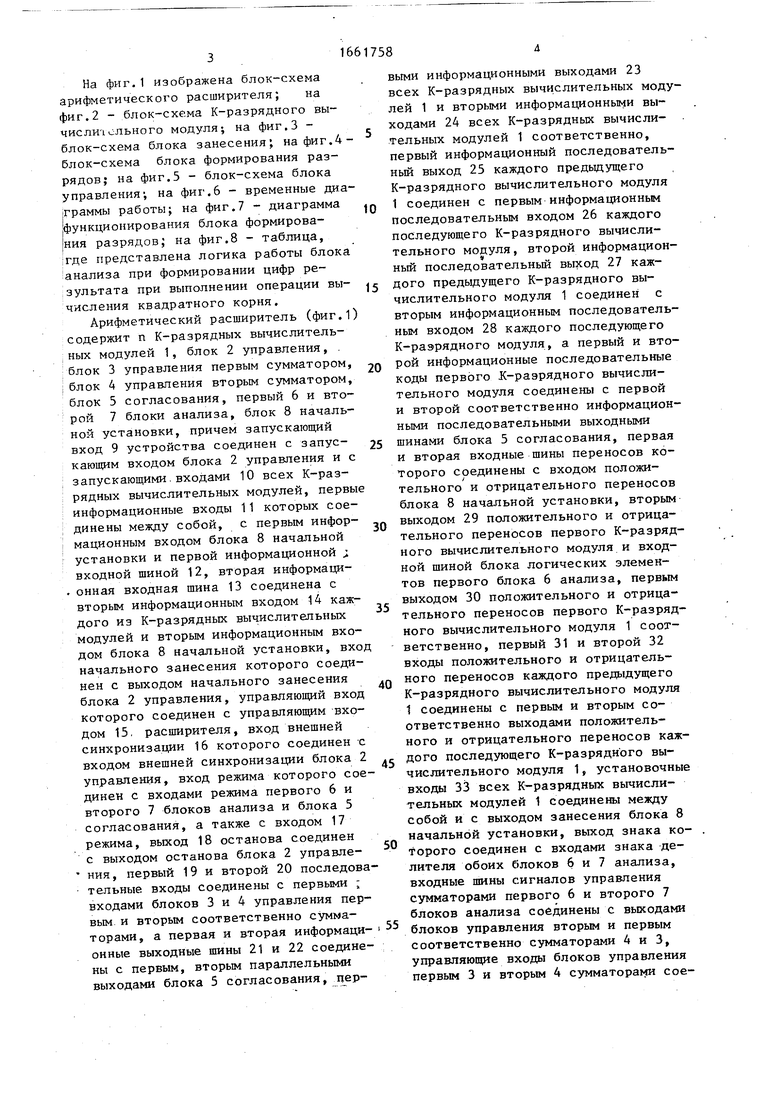

Каждый К-разрядньй вычислительный модуль 1 (фиг.2) содержит первый сумматор 47, имеющий первый и второй информационные входы, второй сумматор 48, имеющий первый и второй информационные входы, первый регистр 49, второй регистр 50, третий, четвертый и пятый регистры 51 - 53,первый и второй вычитатели 54 и 55,причем в каждом К-разрядном вычислительном модуле 1 информационный вход первого регистра 49 соединен с первым информационным входом 11 К-разрядного вычислительного модуля 1 р параллельный управляющий вход первого регистра 49 соединен с управляющим входом пятого регистра 53 и запускающим входом 10 К-разрядного вычислительного модуля 1, первый синхронизирующий вход 39 которого соединен с входом синхронизации второго регистра 50, обнуляющий вход которого соединен с обнуляющими входами

четвертого, третьего регистров 52 и 51 и обнуляющим входом 38 К-разрядного вычислительного модуля 1, второй синхронизирующий вход 40 которого соединен с синхронизирующими

входами третьего, четвертого и пятого регистров 51 - 53, последовательные входы которых соединены с первым, вторым и третьим соответственно информационными последовательными входами 26, 28 и 42 К-разрядного вычислительного модуля 1, информационный вход пятого регистра 53 соединен с вторым информационным входом 14 К-разрядного вычислителького модуля 1, первый и второй информационные последовательные выходы 25. и 27 которого соединены с последовательными выходами третьего и четвертого регистров 51 и 52 соответ

ственно, а третий, четвертый и пятый информационные последовательные выходы 43, 34 и 35 К-разрядного вычислительного модуля 1 соединены с последовательным, первым и вторым выходами старших разрядов соответственно пятого регистра 53, а шестой информационный последовательный выход 41 К-разрядного вычислительного Модуля 1 соединен с выходом старшего разряда второго регистра 50, установочный вход которого соединен с установочным входом 33 К-разрядного Вычислительного модуля 1, первый и Второй выходы 30 и 29 положительно- fo и отрицательного переносов которого соединены с выходами положительного и отрицательного переносов первого и второго соответственно сумматоров 47 и 48, управляющие входы Которых соединены с входами 36 и 37 Управления первым и вторым соответственно сумматорами 47 и 48 К-разрядного вычислительного модуля 1, первый и второй информационные выходы 23 и 24 которого соединены с выходами первого и второго соответственно вычитателей 54 и 55, а первый и второй входы 31 и 32 положительного и отрицательного переносов К-разрядного вычислительного модуля 1 соединены с входами положительного и отрицательного переносов первого и второго соответственно сумматоров 47 и

48,четные разряды первого информационного входа первого сумматора 47 соединены с выходами соответствующих нечетных разрядов первого регистра

49,а нечетные разряды второго информационного входа второго сумматора 48 соединены с выходами соответствующих четных разрядов первого регистра 49, второй информационный вхо первого сумматора 47 соединен с входной информационной шиной первого вы- читателя 54 и выходом второго регистра 50, информационный вход которого соединен с выходом второго сумматора 48, первый информационный вхо второго сумматора соединен с выходом первого сумматора 47, а выход третьего регистра 51 соединен с выходом четвертого регистра 52 и входной информационной шиной второго вычитател 55. Кроме того, каждый К-разрядный вычислительный модуль 1 содержит бло 56 формирования разрядов и в первом регистре 49 задействованы входы по0

5

0

5

0

5

0

5

0

5

разрядного управления, входы поразрядного занесения, вход установки в О, а в первом регистре 49 первого К-разрядного вычислительного модуля 1 установочный вход старшего разряда, причем в каждом К-разрядном вычислительном модуле 1 вход поразрядного управления первого регистра 49 соединен с входом управления блока 56 формирования разрядов и входом 45 поразрядного управления К-разрядного вычислительного модуля, вход 46 режима перво го К-раэрядного модуля 1 соединен с установочным входом старшего разряда первого регистра 49, вход установки в О первого регистра 49 соединен с обнуляющим вкодом 38 К-разрядного вычислительного модуля 1, вход поразрядного занесения первого регистра 49 соединен с управляющими входами первого и второго сумматоров 47 и 48, а выход первого регистра 49 соединен с входной информационной шиной блока 56 формирования разрядов, первый и второй входы которого соединены с входом управления первым и вторым сумматорами 36 и 37 соответственно, а выходная информационная шина блока 56 формирования разрядов соединена с первым информационным входом первого сумматора 47 и вторым информационным входом второго сумматора 48.

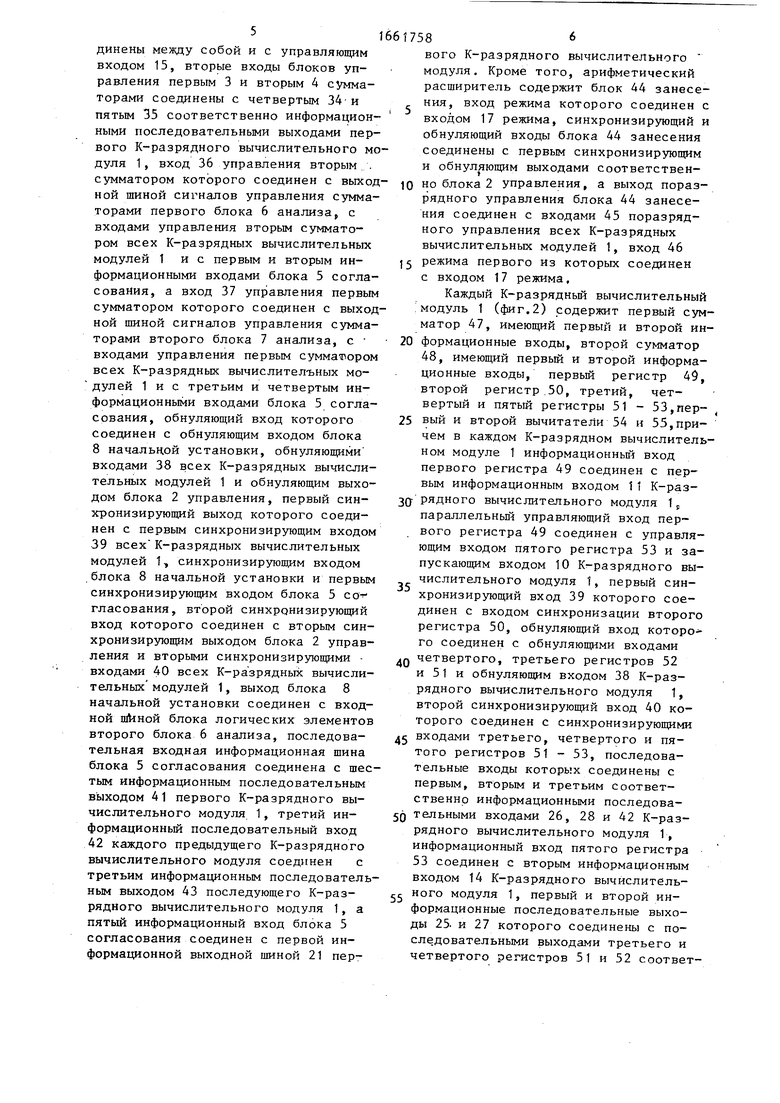

Блок занесения 44 (фиг. 3) состоит из элемента И 57, счетчика 58 и дешифратора 59, причем первый вход элемента И 57 соединен с синхронизирующим входом 60 блока 44 занесения, второй вход элемента И 57 соединен с входом 61 режима блока 44 занесения, а выход элемента И 57 соединен со счетным входом счетчика 58, обнуляющий вход которого соединен с обнуляющим входом 62 блока 44 занесения, а выход счетчика 58 соединен с входом дешифратора 59, выход которого соединен с выходом 63 поразрядного управления блока 44 занесения.

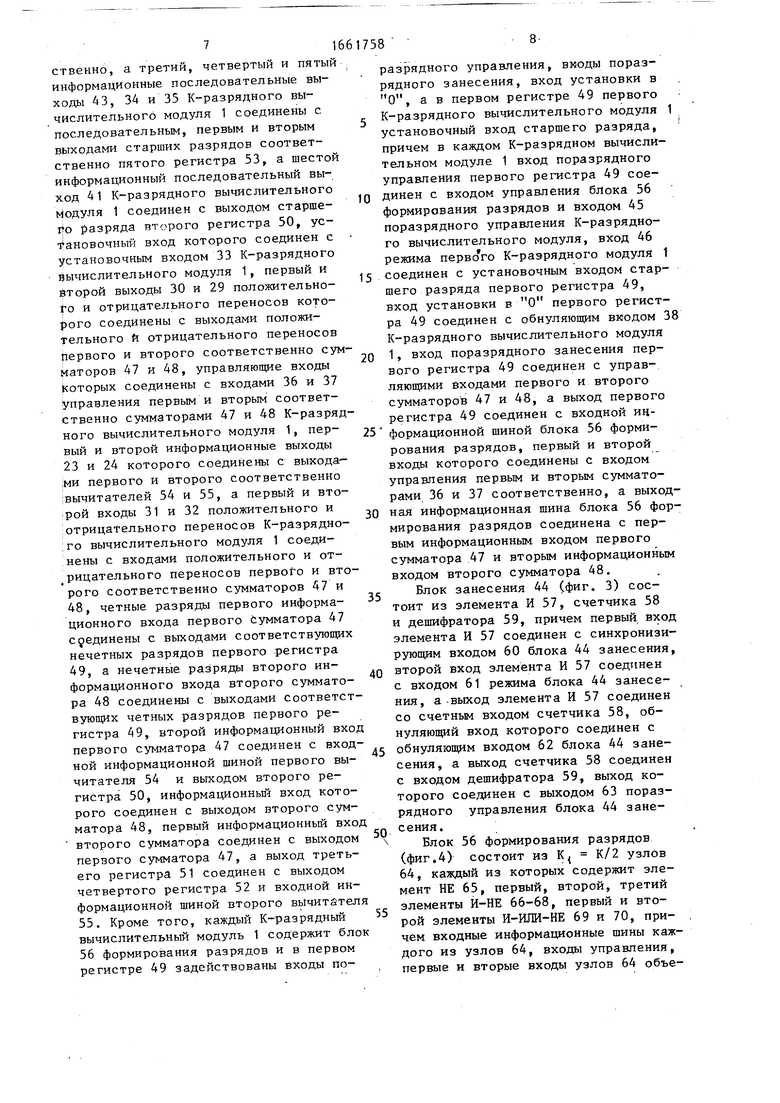

Блок 56 формирования разрядов (фиг.4) состоит из К К/2 узлов 64, каждый из которых содержит элемент НЕ 65, первый, второй, третий элементы И-НЕ 66-68, первый и второй элементы И-ИЛИ-НЕ 69 и 70, причем входные информационные шины каждого из узлов 64, входы управления, первые и вторые входы узлов 64 объединены соответственно между собой и являются входной информационной шиной 71, входом 72 управления, первым и вторым входами 73 и 74 соответственно блока 56 формирования разрядов, а выходы всех узлов 64 объединены в выходную информационную шину 75 блока 56 формирования разрядов. В каждом узле 64 вход элемента НЕ 65 соединен с входом 72 управления блока 56 формирования разрядов, с первым входом первой группы первого элемента И-ИЛИ-НЕ 69, первым входом первого элемента И-НЕ 66, первыми входами первой и второй групп второго элемента И-ИЛИ-НЕ 70, второй вход первой группы которого соединен с вторым входом первого элемента И-НЕ 66, вторым входом первой группы первого элемента И-ИЛИ-НЕ 69 и первым входом 73 узла 64, -входная информационная шина 71 которого соединена с первым входом второго элемента И-НЕ 67, первым входом третьего элемента И-НЕ 68, первым входом вторбй группы первого элемента И-ИЛИ-НЕ 69, первым входом третьей группы второго элемента И-ИЛИ-НЕ 70, второй вход второй группы второго элемента И-ИЛИ-НЕ 70 соединен с вторым входом 74 узла 64, а выход элемента НЕ 65 соединен с вторым уходом второго элемента И-НЕ 67 и первым входом третьего элемента И-НЕ 68 второй вход которого соединен с выходом первого элемента И-НЕ 66, а выходы второго и третьего элементов И-НЕ 67 и 68, первого и второго элементов И-ИЛИ-НЕ 69 и 70 соединены с выходом узла 64.

Блок 2 управления (фиг. 5) содержит первый, второй, третий элементы задержки 76-78, триггер 79 управления, генератор 80 импульсов, коммутатор 81, счетчик 82 импульсов, формирователь 83 импульсов, блок 84 совпадения. Выход формирователя 83 импульсов соединен с обнуляющим входом счетчика 82 импульсов, обнуляющим выходом 85 блока 2 управления и входом третьего элемента 78 задержки, выход которого соединен с входом первого элемента 76 задержки и первым входом блока 84 совпадения, второй вход которого соединен с входом 86 режима блока 2 управления, выход которого соединен с выходом 87 начального занесения блока 2 управления. Выход

0

5

0

5

0

5

0

5

0

5

счетчика 82 импульсов соединен с выходом 88 останова блока 2 управления и с обнуляющим входом триггера 79 управления, выход которого соединен с управляющим входом генератора 80 импульсов, выход которого соединен с первым информационным входом коммутатора 81, выход которого соединен со счетным входом счетчика 82 импульсов, входом второго элемента 77 задержки и первым синхронизирующим выходом 89 блока 2 управления. Второй синхронизирующий выход 90 и запускающий вход 91 блока 2 управления соединены с выходом второго элемента 77 задержки и входом формирователя 83 импульсов соответственно. Вход 92 внешней синхронизации и управляющий вход 93 блока 2 управления соединены с вторым информационным и управляющим входами коммутатора 81 соответственно. Выход первого элемента .76 задержки . соединен с установочным входом триггера 79 управления.

Работу арифметического расширителя рассмотрим для случая выполнения операции извлечения корня. (Последовательность работы устройства при умножении и делении аналогична прототипу) . Вначале выбирается режим работы, для чего на управляющий вход 15 и вход 17 режима подаются соответствующие сигналы. Работа начинается с подачи на запускающий вход 9 единичного импульса произвольной длительности. При поступлении этого импульса на запускающий вход 91 блока 2 управления, который является входом формирователя 83 импульсов, последний вырабатывает отрицательный импульс, по которому производится установка в О первого, второго регистров 49 и 50, третьего, четвертого регистров 51 и 52 каждого К-разрядного вычислительного модуля 1. счетчика 58 блока 44 занесения, регистров и триггеров блоков .согласования 5 и начальной установки 8 первого и второго блоков 6 и 7 анализа.

Запись начального значения подко- ренного выражения D0 1-А при выполнении операции х производится во второй регистр 50 К-разрядных вычислительных модулей 1 по совпадению сигналов кода операции и переднему фронту задержанного третьим элементом 78 задержки выходного импульса формирователя 83 блока 2 управления.

11

1661758

Кроме этого, по этому же сигналу производится занесение начапьных условий в регистры начальной установки второго блока 7 анализа и блока 8 начальной установки, которые представляют собой значения старших раз- рЯдов подкоренного выражения, посту- п4ющих с второй информационной входной шины 13. Запись начального зна- х х 1,0 производится в первые регистры 49 К-разрядных вычислительных модулей 1, отведенных под накопление результата операции извлечения корня, по сигналу кода опе- , поступающему на вход 46 режиму первого К-разрядного вычислитель- нфго модуля 1.

Ввиду того, что дальнейшая обра- бфтка операндов производится на сум- м торах в знакоразрядной системе кодирования, занесение начального зна- чфния операндов происходит непосред- сфвенно в параллельном знакоразряд- ном коде.

Далее в блоке 2 управления через время Јэ) , обусловленное задержкой распространения импульса через третий и первый элементы 78 и 76 задержки и временем срабатывания триггера 79 управления, производится запуск генератора 80 импульсов, с выхода которого через коммутатор 8J пбступает на вход счетчика 82 импульсов синхронизирующая серия импульсов с периодом Т-1аЬ|у . Эта же серия импульсов поступает на первый синхронизирующий выход 89 и через второй элемент 77 задержки на второй синхронизирующий выход 90 блока 2 управления.

При этом

31

Гсл .+ТЈд

твыи тз + Трг2,

е Т

СМ1

Тсг - времена получения результата на выходах первого и второго сумматоров 47 и 48 К-разрядных вычислительных модулей 1;

Т t- - время срабатывания обоих,, блоков 6 и 7 анализа и блока 8 начальном установки; c-j,- время задержки первого элемента 76 задержки; Т р. - время срабатывания второго

12

регистра 50 каждого К-разрядного вычислительного модуля 1.

1см,

fl

СМ

Л О.Л

+ V +V Т

1е- cpfi

смг

см.

PV

гДе .с/ис

ссм - времена срабатывания первого и второго сумматоров 47 и 48 К-разрядных вычислительных модулей 1 у рч время срабатывания первого регистра 49 К-разрядного вычислительного модуля 1 , c - время срабатывания блока 56 формирования разрядов К- разрядного вычислительного модуля 1.

Таким образом, процесс вычисления Q заключается в следующем. На первом шаге вычисления на выходе первого сумматора 47 К-разрядного вычислительного модуля 1 формируется величина5

2 D0 +

Н

хо 2 Г Dt

(1)

0

5

0

0

где г. - значение одной цифры корня, формируемое на первом такте на выходе второго блока 7 анализа,

Н - шаг сдвига, в данном случае Н - это сдвиг на один двоичный разряд,

а на выходе второго сумматора 48 Кразрядного вычислительного модуля

формируется величина

2 D1 + (xo+Hr4-f rft)VD., (2)

где г - значение следующей цифры

корня, формируемое на первом такте на выходе первого блока 6 анализа.

Н 5 Формирование слагаемых г,, Нг,

Н

т г для первого и второго сумматоров

47 и 48 производится в блоке 56 формирования разрядов в соответствии с диаграммой на фиг.7.

Первый и второй сумматоры 47 и 48 К-разрядных вычислительных модулей 1 функционируют под управлением сигналов, поступающих с выхода первого и второго блоков 6 и 7 анализа. В режиме умножения блоки 6 и 7 пропуска- .„ ют без преобразования сигналы управления сумматорами 47 и 48 с выходов

блоков 3 и 4 управления первым и вторым сумматорами. В режиме извлечения корня в блоках 6 и 7 анализа формируются сигналы г- управления сумматорами 47 и 48 вычислительных мо- дулей 1, являющиеся одновременно цифрами корня и поступающие на входы поразрядного занесения первого регистра 49 К-разрядного вычислительного модуля 1 и на вход блока 5 согласования (по первому синхронизирующему сигналу г). Цифры корня формируются в блоках анализа по значениям двух старших разрядов а0, а, а}, а сумматоров 47 и 48 К-разрядных вычислительных модулей 1 в соответствии с таблицей (фиг.8).

Прохождение цифр корня г, г, г, г через блок 5 согласования аналогично прохождению этих пар цифр в режиме деления.

После поступления каждого следующего тактового импульса на выходах первых сумматоров 47 К-разрядных вычислительных модулей 1 формируется величина

D

н;

i -YV v.

а на выходах вторых сумматоров 48 К-разрядных вычислительных модулей 1 формируется величина1

D,, 2 В; + (х,+Н;Г4,- S-i гг{ ) га; .

Следовательно, при формировании слагаемых на первые сумматоры 47 К-разрядных вычислительных модулей 1 необходимо задать второе слагаемое

Н

х- - , а на вторые сумматоры

48 К-разрядных вычислительных модулей 1 - второе слагаемое х + .Н - ™ г 2| , где (х; + Н;г,,; ) - очеред-

ное приближение значения подкоренного выражения х- с выхода первых регистров 49 К-разрядных вычислительных модулей 1, а - -г Г2; - так назы

ваемая бегущая 1, подсуммируемая во втором сумматоре 48 с учетом сигнала управления г , .

Указанные последовательности при выполнении операции извлечения корня формируются на выходе блока 56 формирования разрядов в зависимости от четности номера разряда, номера так0

5

0

5

5

0

5

та и входных величин блока, поступающих с выхода первого регистра 49, в соответствии с диаграммой, представ- i ленной на фиг.7. На диаграмме верхний ряд каждой линейки отражает входную последовательность второго слагаемого второго сумматора 48 К-разрядного вычислительного модуля 1, а нижний ряд - входную последовательность второго слагаемого первого сумматора 47 К-разрядного вычислительного модуля 1. Количество линеек соответствует числу тактов, так, например, для извлечения корня из 24-разрядного числа количество тактов равно 12. Цифры над линейкой означают номера разрядов, по которым поступают вторые слагаемые на входы первого и второго сумматоров 47 и 48. Заштрихованные ячейки на диаграмме - это выходные сигналы соответствующих разрядов первого регистра 49. Заполнение ячеек соответствует формулам (1) и (2). Из анализа диаграммы следует, что при выполнении операции извлечения квадратного корня: входные сигналы четных разрядов первого сумматора 47 и входные сигналы нечетных разрядов второго сумматора 48 принимают значения О или значения соответствующего разряда первого регистра 49, или только значения соответствующего разряда, если обнулять в исходном состоянии весь первый регистр 49; входные сигналы нечетных разрядов первого сумматора 47 принимают значения (с учетом обнуления регистра 49) или соответствующего разряда первого регистра 49 или значение управляющей цифры - г ; входные сигналы четных разрядов второго сумматора 48 принимают значения или соответствующего разряда первого регистра 49, или значения управляющей цифры - г., или значение управляющей цифры - г ; управление по занесению информации в различные разряды первого и второго сумматоров 47 и 48 может быть общим на группу разрядов, т.е. каждая группа разрядов управляется дешифрацией номера такта i.

Таким образом, с выходной информационной шины блока 56 формирования разрядов сигналы поступают на нечетные разряды первого информационного входа первого сумматора 47 и на четные разряды второго информационного входа второго сумматора 48. На чет

15

ные разряды первого информационного входа первого сумматора 47 и на нечетные разряды второго информационного входа второго сумматора 48 поступают сигналы непосредственно с вы Ходов соответствующих разрядов перво го регистра 49.

На основании вышеизложенного, на входную информационную шину 71 блока 56 формирования разрядов (фиг.4) поступают сигналы с выходов соответствующих разрядов первого регистра 49, на вход 72 управления - тдктирующая серия с выхода поразрядного управления блока 44 занесения, а на первый и второй входы 73 и 74 блока 56 формирования разрядов - соответственно сигналы г д и т„ с выходов первого и второго блоков 6 и 7 анализа.

В качестве примера рассмотрим . входные сигналы двух соседних разрядов блока 56 формирования разрядов, представленных на фиг.4, Тактирующий

сигнал Cj подается на вход элемента НЕ 65 и первый вход первой группы первого элемента И-ИЛИ-НЕ 69, а также на первый вход второй группы второго элемента И-ИЛИ-НЕ 70, тактирующий сигнал С,г. подается на первый вход первого элемента И-НЕ 66 и первый вход первой группы второго элемента И-ИЛИ-НЕ 70. На входную информационную шину 71 блока 56 поступают сигналы с выходов соответствующих разрядов первого регистра 49, представленных в энакоразрядном коде. На первый и второй входы 73 и 74 поступают соответственно сигналы г,| и TЈ. Выходными сигналами блока 56 формирования разрядов являются сигналы занесения нечетных разрядов первого сумматора 47 и сиг налы занесения четных разрядов второго сумматора 48,

Блок 56 формирования разрядов в других режимах без искажения пропускает сигналы с выходов соответствующих разрядов первого регистра 49 на соответствующие входы первого и второго сумматоров 47 и 48 К-разряд- ньтх вычислительных модулей 1 .

Тактирующими сигналами для блока 56 формирования разрядов являются выходные сигналы блока 44 занесения (фиг. 3), которые формируются при наличии на входе режима кода операции - корень - по синхроимпульсам 0, , поступающим на вход 60

5

0

1758

5

0

1Ь

блока 44 с выхода 89 блока 2 управления. Блок 44 занесения формирует на своем выходе 63 поразрядного управления унитарную последовательность тактирующих импульсов для управления блоком 56 формирования разрядов и управления процессом занесения информации (значения корня) в первый регистр 49 К-разрядного вычислительного модуля 1.

На каждом шаге вычислений величина Dtj по синхронизирующему сигналу Ся с второго синхронизирующего выхода 90 блока 2 управления записывается во второй регистр 50 К-разрядного вычислительного модуля 1.

Дальнейшее прохождение цифр частного г по блокам следующее: цифры корня поступают на первый, второй,

5

0

5

0

0

третий и четвертый информационные входы блока 5 согласования, а далее на вход буферного регистра и входы второго мультиплексора блока 5 согласования. Запись в третий регистр блока 5 согласования производится по синхронизирующей серии с второго синхронизирующего выхода блока 2 управления. Дальнейшая обработка цифр результата в блоке 5 согласования аналогична прототипу.

После поступления следующего тактового импульса с первого и второго синхронизирующих выходов 89 и 90 блока 2 управления процесс обработки ин-J формации повторяется до тех пор, пока не будут сформированы все цифры результата, по две цифры на каждом такте вычислений.

После каждой вычислительной итерации (шага) с выходов первого и второго блоков 6 и 7 анализа в блок 5 согласования поступает очередная пара цифр , а во втором регистре 50 5 К-разрядных вычислительных модулей 1 заносится значение частичного остатка.

После первых четырех тактов на первой и второй информационных последовательных выходных шинах блока 5 согласования появляются две старшие цифры результата, которые поступают в третий и четвертый регистры 51 и 52 первого К-разрядного вычислительного модуля 7, причем в первый из них поступают четные разряды результата, а во второй - нечетные. Поступление первых двух цифр на последовательные выходные шины блока согласования происходит так же, как и в режиме деления и умножения через четыре такта, благодаря наличию последовательного ряда регистров и триггеров (буферного регистра) в блоке 5 согласования, предназначенных для согласования индексов переменных. Перед каждым циклом вычислений буферный регистр следует обнулять. По окончании п шагов, где п1 К/2-1 (К - разрядность операндов) в третьем и четвертом регистрах 51 и 52 К- разрядных вычислительных модулей 1 сформированы старшие разряды результата соответственно для четных и нечетных разрядов, оставшиеся старшие разряды результата формируются на первом и втором информационных выходах блока 5 согласования, а разряды остатков - на первом и втором информационных выходах К-разрядных вычислительных модулей 1.

Преобразование избыточного кода в дополнительный осуществляется путем выполнения операции xt - x на первом и втором вычитателях 54 и 55 К- разрядных вычислительных модулей 1 и на сумматорах-вычитателях лока 5 согласования. Процесс получения дополнительного кода из знакоразрядно- го в блоке 5 согласования происходит аналогично режимам умножения и деления .

После К итераций с выхода счетчика 82 импульсов блока 2 управления поступает импульс на обнуляющий вход триггера 79 управления, который запрещает формирование синхронизирующих импульсов генератора 80 импульсов. На первой и второй информационных выходных шинах 21 и 22 формируется результат операции извлечения корня.

Так как на каждом такте вычислений производится занесение цифр корня в первый регистр 49 К-раэрядного вычислительного модуля 1, результат операции извлечения корня будет сформирован после окончания всех циклов в первом регистре 49 в виде знако- разрядного числа.

Формула изобретения

Арифметический расширитель, содержащий блок управления, блок управления первым сумматором, блок управления вторым сумматором, блок на0

5

0

5

0

5

0

5

0

5

чальной установки, первый и второй блоки анализа, блок согласования, п К-разрядных вычислительных модулей, каждый из которых содержит первый сумматор, второй сумматор, первый регистр, второй регистр, третий, четвертый и пятый регистры, первый вычитатель, второй вычитатель,причем в каждом К-разрядном вычислительном модуле информационный вход первого регистра соединен с первым информационным входом К-разрядного вычислительного модуля, параллельный управляющий, вход первого регистра соединен с управляющим входом пятого регистра и запускающим входом К-раз- рядного вычислительного модуля, первый синхронизирующий вход которого соединен с входом синхронизации второго регистра, обнуляющий вход которого соединен с обнуляющими входами четвертого, третьего регистров и обнуляющим входом К-разрядного вычислительного модуля, второй синхронизирующий вход которого соединен с синхронизирующими входами третьего, четвертого и пятого регистров, .последовательные входы которых соединены с первым, вторым и третьим соответственно информационными последовательными входами К-разрядного вычислительного модуля, информационный, вход пятого регистра соединен с вторым информационным входом К-разрядного вычислительного модуля, первый и второй информационные последовательные выходы которого соединены с последовательными выходами третьего и четвертого регистров соответственно, а третий, четвертый, пятый информационные последовательные выходы К-разрядного вычислительного модуля соединены с последовательным, первым и вторым выходами старших разрядов соответственно пятого регистра, а шестой информационный последовательный выход К-разрядного вычислительного модуля соединен с выходом старшего разряда второго регистра, установочный вход КОТОРОГО соединен с установочным входом К-разрядного вычислительного модуля, первый и второй выходы положительного и отрицательного переносов которого соединены с выходами положительного и отрицательного переносов первого и второго соответственно сумматоров, управляющие входы которых соединены

с входами управления первым и вторым Соответственно сумматорами К-разряд- Ного вычислительного модуля, первый и BTOt i информационные выходы которого соединены с выходами первого и Второго соответственно вычитателей, Первый и второй входы положительного и отрицательного переносов К-разряд- ного вычислительного модуля соединены с входами положительного и отри- Ьатёльного переносов первого и второго соответственно сумматоров, чет- йые разряды первого информационного входа первого сумматора соединены „ с выходами соответствующих нечетных разрядов первого регистра, первый информационный вход второго сумматора соединен с выходом первого сумматора, а нечетные разряды второго информационного входа второго сумматора соединены с выходами соответствующих четных разрядов первого регистра, второй информационный вход первого сумматора соединен с входной информационной шиной первого вычитателя и выходом второго регистра, информационный вход которого соединен с выходом второго сумматора, а выход третьего регистра соединен с выходом четвертого регист- 1ра и входной информационной шиной второго вычитателя, причем запускающий вход арифметического расширителя соединен с запускающим входом блока управления и с запускающими входами всех К-разрядных вычислительных модулей, первые информационные входы которых соединены между собой, с первым информационным входом блока начальной установки и первой информационной входной шиной арифметического расширителя, вторая информационная входная шина которого соединена с вторым информационным входом каждого из К-разрядных вычислительных модулей и вторым информационным входом блока начальной установки, вход начального занесения которого соединен с выходом начального занесения блока управления, управляющий вход которого соединен с управляющим входом арифметического расширителя, вход внешней синхронизации которого соединен с входом внешней синхронизации блока управления, вход режима которого соединен с входами режима первого и второго блоков анализа и блока согласования, а также с входом режима арифметического рас

5

0

5

0

5

0

5

0

5

ширителя, выход останова которого соединен с выходом останова блока управления, первый и второй последе, вательные входы арифметического рас ширителя соединены с первыми входами блоков управления первым и вторым сумматорами соответственно, а первая и вторая информационные выходные шины арифметического расширителя соединены с первым, вторым, параллельными выходами блока согласования, первыми информационными выходами всех К-разрядных вычислительных модулей и вторыми информационными выходами всех К-разрядных вычислительных модулей соответственно, первый информационный последовательный выход каждого предыдущего К-разрядного вычислительного модуля соединен с первым информационным последовательным входом каждого последующего К-разрядного вычислительного модуля, второй информационный последовательный выход каждого предыдущего К-разрядного вычислительного модуля соединен с вторым информационным последовательным входом каждого последующего К-разрядного модуля, а первый и второй информационные последовательные входы первого К-разрядного вычислительного модуля соединение первой и второй соответственно информационными последовательными выходными шинами блока согласования, первая и вторая входные шины переносов которого соединены с входом положительного и отрицательного переносов блока начальной установки, вторым выходом по- ложительного и отрицательного переносов первого К-разрядного вычислительного модуля и входной шиной блока логических элементов первого блока анализа, первым выходом положительного и отрицательного переносов первого К-разрядного вычислительного модуля соответственно, первые и вторые входы положительного и отрицательного переносов каждого предыдущего К- разрядного вычислительного модуля соединены с первым и вторым соответственно выходами положительного и отрицательного переносов каждого последующего К-разрядного вычислительного модуля, установочные входы всех К- разрядных вычислительных модулей соединены между собой и с выходом занесения блока начальной установки, выход знака которого соединен с входами знака делителя обоих блоков анализа, входные шины сигналов управления сумматорами первого и второго блоков анализа соединены с выходами блоков управления вторым и первым сумматорами соответственно, управляющие входы блоков управления первым и вторым сумматорами соединены между собой и с управляющими входами арифметического расширителя, вторые входы блоков управления первым и вторым сумматорами соединены с четвертым и пятым соответственно информационными последовательными выходами первого К-разрядного вычислительного модуля, вход управления вторым сумматором которого соединен с выходной шиной сигналов управления сумматором первого блока анализа, с входами управления вторым сумматором всех К- разрядных вычислительных модулей и с первым и вторым информационными входами блока согласования, вход управления первым сумматором которого соединен с выходной шиной сигналов управления сумматорами второго блока анализа, с входами управления первым сумматором всех К-разрядных вычислительных модулей и с третьими и четвертыми, информационными входами блока согласования, обнуляющий вход которого соединен с обнуляющим входом блока начальной установки, обнуляющими входами К-разрядных вычислительных модулей и обнуляющим-выходом блока управления, первый синхронизирующий выход которого соединен с первыми синхронизирующими входами всех К-разрядных вычислительных модулей, синхронизирующим входом блока начальной установки и первым синхронизирующим входом блока согласования, второй синхронизирующий вход которого соединен с вторым синхронизирующим выходом блока управления и вторыми

синхронизирующими входами всех К-разрядных вычислительных модулей, выход блока начальной установки соединен с входной шиной блока логических элементов второго блока анализа, последовательная входная информационная шина блока согласования соединена с шестым информационным последователь,ным выходом первого К-разрядного вычислительного модуля, третий информационный последовательный вход каждого предыдущего К-разрядного вычис5

0

5

лительного модуля соединен с третьим информационным последовательным выходом последующего К-разрядного вычислительного модуля, а пятый информационный вход блока согласования соединен с первой информационной выходной шиной первого К-разрядного вычислительного модуля, о т л и ч а ющ и и с я тем, что, с целью расширения функциональных возможностей за счет обеспечения вычисления квадратного корня, он содержит блок занесения, а каждый из К-разрядных вычислительных модулей дополнительно содержит блок формирования разрядов и в первом регистре всех К-разрядных вычислительных модулей задействованы входы поразрядного управления, входы поразрядного занесения, вход установки в О, а в первом регистре первого К-разрядного вычислительного модуля - установочный вход старшего разряда, причем блок занесения состоит из счетчика, дешифратора и элемента И, первый вход которого соединен с синхронизирующим входом блока занесения, второй вход элемента И соединен с входом режима блока занесения, а выход соединен со счетным входом счетчика, обнуляющий вход которого соединен с обнуляющим входом блока занесения, а выход счетчика соединен с входом дешифратора выход которого соединен с выходом поразрядного управления блока занесения9блок формирования разрядов состоит из п/2 узлов, каждый из которых содержит элемент НЕ, три элемента И-НЕ, два элемента И-ИЛИ-НЕ, причем входные информационные шины каждого из узлов, входы управления и первые и BTQ- , рые входы узлов объединены между собой и являются входной информационной шиной, входом управления, первым и вторым входами соответственно блока формирования разрядов, а выходы всех узлов объединены в выходную информационную шину блока формирования разрядов, а в каждом из узлов вход элемента НЕ соединен с входом управления блока формирования .разрядов, с первым входом первой группы первого элемента И-ИЛИ-НЕ, первым входом первого элемента И-НЕ, первыми входами первой и второй групп второго элемента И-ИЛИ-НЕ, второй вход первой группы которого соединен с вторым входом первого элемен0

5

0

5

0

5

та И-НЕ, вторым входом первой группы первого элемента И-ИЛИ-НЕ и первый входом узла, входная информационная шина которого соединена с первым входом второго элемента И-НЕ, первым входом третьего элемента И-НЕ, первым входом второй группы первого элемента И-ИЛИ-НЕ, первым входом третьей группы второго элемента И-ИЛИ-НЕ, второй вход второй группы второго элемента И-ИЛИ-НЕ соединен с вторым входом узла, а выход элемента ЧЕ соединен с вторым входом второго эле- мзнта И-НЕ и первым входом третьего элемента И-НЕ, второй вход которого соединен с выходом первого элемента , а выходы второго и третьего элементов И-НЕ, первого и второго элементов И-ИЛИ-НЕ соединены с вы- узла, в каждом К-разрядном вычислительном модуле вход поразрядно- гб управления первого регистра соеди- нфн с входом управления блока формирования разрядов и входом поразрядного управления К-раэрядного вычислительного модуля, вход установки в О первого регистра соединен с обнуляющим входом К-разрядного вычислительного модуля, вход поразрядного занесения первого регистра соединен с входами управления первым и вторым сумматорами соответственно, з выход первого регистра соединен с входной информационной шиной блока формирования разрядов, первый и второй входы которого соединены с входами управления первым и вторым сумматорами соответственно, а выходная

информационная шина блока формирования разрядов соединена с первым информационным входом первого сумматора и вторым информационным входом второго сумматора, вход режима первого К-разрядного вычислительного модуля соединен с установочным входом старшего разряда первого регист-i ра, кроме того, вход режима блока занесения соединен с входом режима

арифметического расширителя, синхронизирующий и обнуляющий входы блока занесения соединены с первым синхронизирующим и обнуляющим выходами соответственно блока управления, а выход поразрядного управления блока занесения соединен с входами поразрядного управления всех К-разрядных вычислительных модулей, вход режима первого из которых соединен с входом

режима арифметического расширителя.

16 15 о о

18

19 о

20 о

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметический расширитель | 1988 |

|

SU1566341A1 |

| Устройство для умножения | 1984 |

|

SU1256016A1 |

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Арифметическое устройство | 1988 |

|

SU1578708A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для умножения | 1987 |

|

SU1472899A1 |

| Вычислительный преобразователь информации | 1985 |

|

SU1330642A1 |

| УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ ПАМЯТИ | 1990 |

|

RU2020566C1 |

Изобретение относится к вычислительной технике, в частности может быть использовано в управляющих, моделирующих и вычислительных комплексах в качестве сопроцессора. Цель изобретения - расширение функциональных возможностей за счет обеспечения вычисления квадратного корня. Арифметический расширитель содержит N K-разрядных вычислительных модулей, блок управления, блоки управления первым и вторым сумматорами, блок согласования, блок начальной установки, первый и второй блоки анализа. Кроме того, он содержит блок занесения, а в каждый K-разрядный вычислительный модуль дополнительно введен блок формирования разрядов для формирования второго операнда сумматоров K-разрядных вычислительных модулей, а также задействованы входы поразрядного занесения, поразрядного управления в первом регистре. Новым в устройстве является реализация операции извлечения корня, причем на каждом такте выполнения операции извлечения корня по сигналам блока управления (устройством) блоки анализа формируют две соседние цифры корня и частичных остатков путем анализа выходных сигналов сумматоров и второго регистра K-разрядных вычислительных модулей. Старшие цифры результата поступают через блок согласования в регистры K-разрядных вычислительных модулей, причем четные- в один регистр, а нечетные- в другой. Преобразование цифр результата в дополнительный код производится на вычитателях K-разрядных вычислительных модулей и блока согласования. Преобразование исходных операндов в знакоразрядный код из дополнительного выполняется монтажными соединениями на входах первого и второго регистров K-разрядных вычислительных модулей. 8 ил.

W1 г 1 Г

±

Ю.

Ј

ъЦУЮЯЯЯЭ5

6

ш

11 М

L

37 30 36 29 J3

31

32

II }

Фиг.1

I

I t( I

.-f

I J I I i

L

J3

W 26 28 1(1)23

25 27 29

+ 22

L

t

L

П

l.

фиг.3

.

91

92, H

85

УUг. 5

ю

79 78

JL

f2J 4

1 П П П

V

tw

-V

123чff

R- П П ПП „

Фиг 6

0123456789 10 fl tt 1314151Б17 1819 0 Я tt 23

Ot23 /5678 9Ю11КЯ1Ы516П181920г122гзг4

щ

шм

Ш

с

ЯГяюкт

г,

J/ffff/m

л

Sifliffiffff

Ж/паю

Мтотя

Фиг. 8

| Устройство для умножения | 1987 |

|

SU1472899A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Арифметический расширитель | 1988 |

|

SU1566341A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-07—Публикация

1989-05-24—Подача