Изобретение относится к импульсно технике.

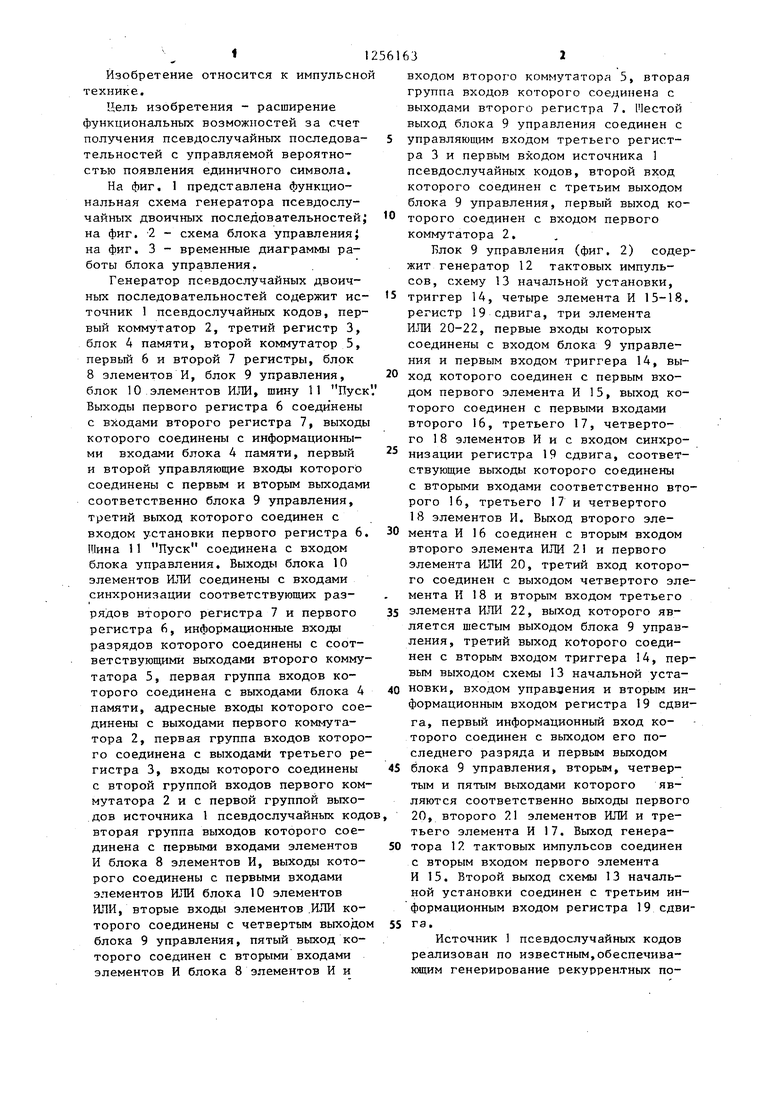

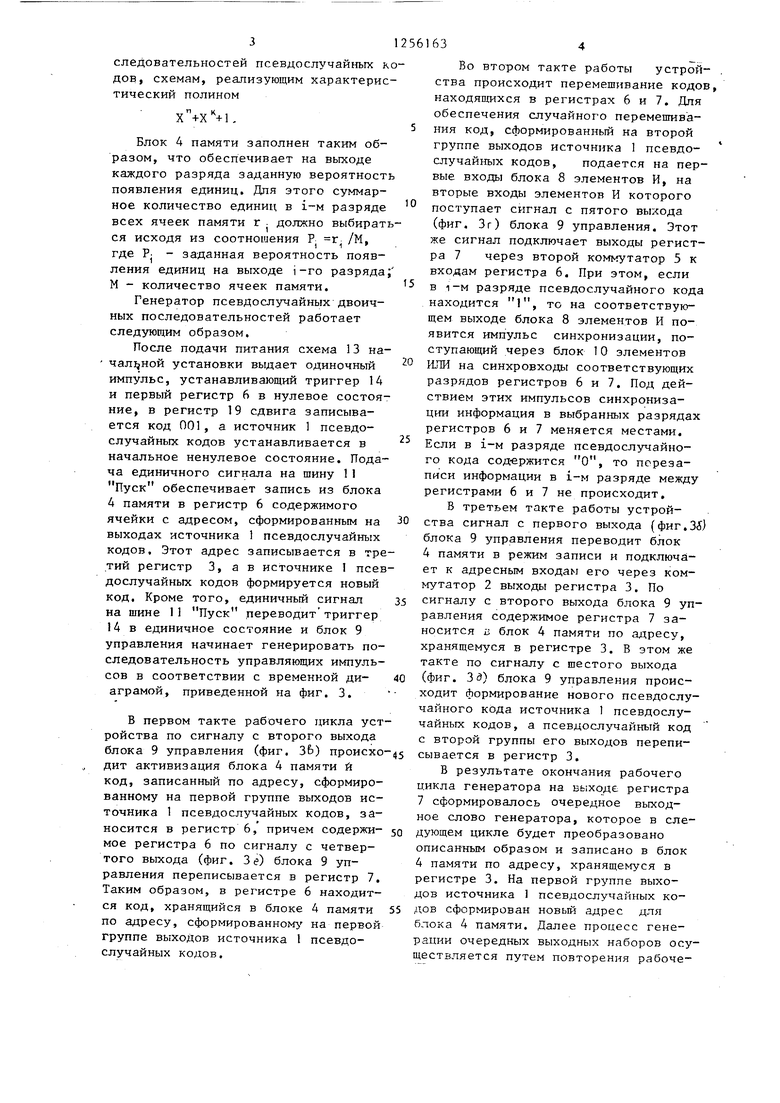

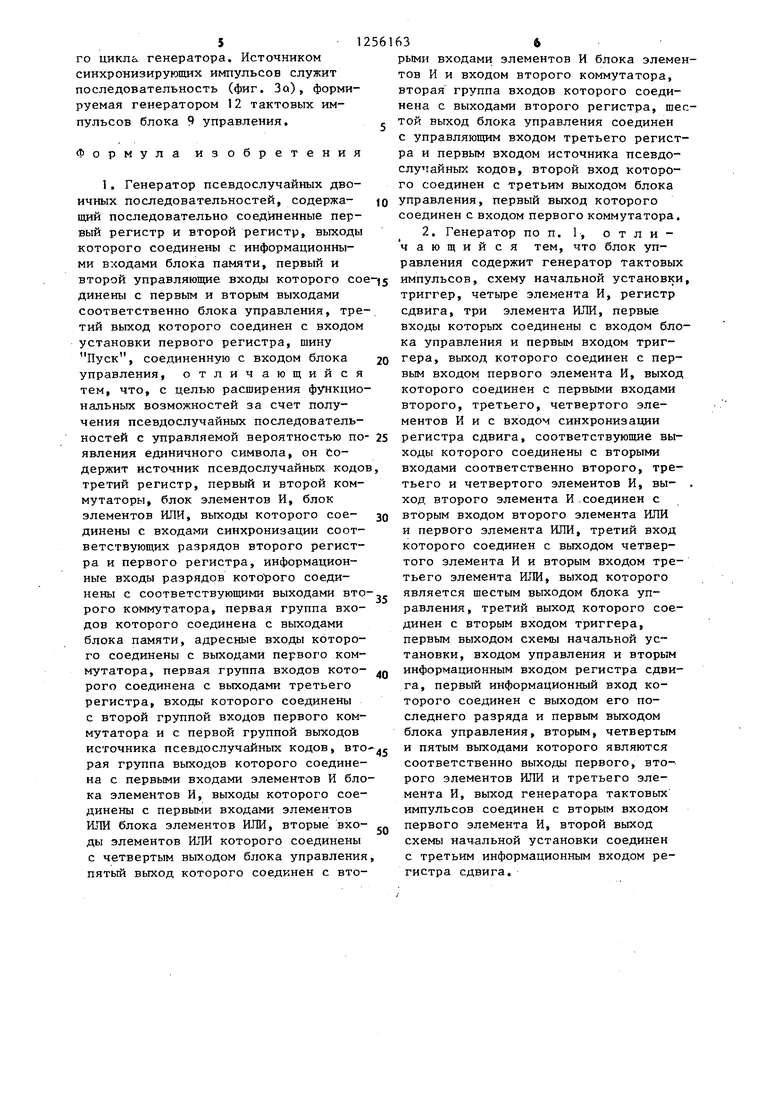

Цель изобретения - расширение функциональных возможностей за счет получения псевдослучайных последовательностей с управляемой вероятностью появления единичного символа. На фиг, 1 представлена функциональная схема генератора псевдослучайных двоичных последовательностей; на фиг. 2 - схема блока управленияJ на фиг, 3 - временные диаграммы работы блока управления.

Генератор псевдослучайных двоичных последовательностей содержит источник 1 псевдослучайных кодов, первый коммутатор 2, третий регистр 3, блок 4 памяти, второй коммутатор 5, первый 6 и второй 7 регистры, блок 8 элементов И, блок 9 управления, блок 10 элементов ИЛИ, шину 11 Пуск Выходы первого регистра 6 соеди нены с входами второго регистра 7, выходы которого соединены с информационными входами блока 4 памяти, первый и второй управляющие входы которого соединены с первым и вторым выходами соответственно блока 9 управления, третий выход которого соединен с входом установки первого регистра 6, Шина 11 Пуск соединена с входом блока управления. Выходы блока 10 элементов ИЛИ соединены с входами синхронизации соответствующих разрядов второго регистра 7 и первого регистра 6, информационные входы разрядов которого соединены с соответствующими выходами второго коммутатора 5, первая группа входов которого соединена с выходами блока 4 памяти, адресные входы которого соединены с выходами первого коммутатора 2, первая группа входов которого соединена с выходами третьего регистра 3, входы которого соединены с второй группой входов первого коммутатора 2 и с первой группой выходов источника 1 псевдослучайных кодо вторая группа выходов которого соединена с первыми входами элементов И блока 8 элементов И, выходы которого соединены с первыми входами элементов ИЛИ блока 10 элементов ИЛИ, вторые входы элементов .ИЛИ которого соединены с четвертым выходом блока 9 управления, пятый выход которого соединен с вторыми входами элементов И блока 8 элементов И и

0

5

входом второго коммутатора 5, вторая группа входов которого соединена с выходами второго регистра 7. Шестой выход блока 9 управления соединен с управляющим входом третьего регистра 3 и первым входом источника 1 псевдослучайных кодов, второй вход которого соединен с третьим выходом блока 9 управления, первый выход которого соединен с входом первого коммутатора 2,

Блок 9 управления (фиг. 2) содержит генератор 12 тактовых импульсов, схему 13 начальной установки, 5 триггер 14, четьфе элемента И 15-18. регистр 19 сдвига, три элемента ИЛИ 20-22, первые входы которых соединены с входом блока 9 управления и первым входом триггера 14, выход которого соединен с первым входом первого элемента И 15, выход которого соединен с первыми входами второго 16, третьего 17, четвертого 18 элементов И и с входом синхронизации регистра 19 сдвига, соответствующие выходы которого соединены с вторыми входами соответственно второго 16, третьего 17 и четвертого 18 элементов И, Выход второго элемента И 16 соединен с вторым входом второго элемента ИЛИ 21 и первого элемента ИЛИ 20, третий вход которого соединен с выходом четвертого элемента И 18 и вторым входом третьего 5 элемента ИЛИ 22, выход которого является щестым выходом блока 9 управления, третий выход которого соединен с вторым входом триггера 14, первым выходом схемы 13 начальной уста- 0 новки, входом управдзения и вторым информационным входом регистра 19 сдвига, первый информационный вход которого соединен с выходом его последнего разряда и первым выходом блока 9 управления, вторым, четвертым и пятым выходами которого являются соответственно выходы первого 20, второго 21 элементов ИЛИ и третьего элемента И 17. Выход генератора 12 тактовых импульсов соединен с вторым входом первого элемента И 15. Второй выход схемы 13 начальной установки соединен с третьим информационным входом регистра 19 сдвига.

Источник 1 псевдослучайных кодов реализован по известным,обеспечива- кщим генерирование рекуррентных по0

5

0

55

следовательностеи псевдослучайных кдов, схемам, реализующим характеристический полином

.

Блок 4 памяти заполнен таким образом, что обеспечивает на выходе каждого разряда заданную вероятност появления единиц. Для этого суммарное количество единиц в i-м разряде всех ячеек памяти г . должно выбиратся исходя из соотношения Р г /М, где Р - заданная вероятность появления единиц на выходе i-го разряда М - количество ячеек памяти.

Генератор псевдослучайных двоичных последовательностей работает следующим образом.

После подачи питания схема 13 на- установки выдает одиночный импульс, устанавливающий триггер 14 и первый регистр 6 в нулевое состояние, в регистр 19 сдвига записывается код 001, а источник 1 псевдослучайных кодов устанавливается в начальное ненулевое состояние. Подача единичного сигнала на шину 11 Пуск обеспечивает запись из блока 4 памяти в регистр 6 содержимого ячейки с адресом, сформированным на выходах источника 1 псевдослучайных кодов. Этот адрес записывается в третий регистр 3, а в источнике I псевдослучайных кодов формируется новый код. Кроме того, единичный сигнал на шине 11 Пуск переводит триггер 14 в единичное состояние и блок 9 управления начинает генерировать последовательность управляющих импульсов в соответствии с временной ди- аграмой, приведенной на фиг. 3.

В первом такте рабочего цикла устройства по сигналу с второго выхода блока 9 управления (фиг. 36) происхо дит активизация блока 4 памяти и код, записанный по адресу, сформированному на первой группе выходов источника 1 псевдослучайных кодов, заносится в регистр 6, причем содержи- мое регистра 6 по сигналу с четвертого выхода (фиг. 3е) блока 9 управления переписывается в регистр 7. Таким образом, в регистре 6 находится код, хранящийся в блоке 4 памяти по адресу, сформированном на первой группе выходов источника 1 псевдослучайных кодов.

10

15

20

5

0

5

0

5 0 5

Во втором такте работы устройства происходит перемешивание кодов, находящихся в регистрах 6 и 7. Для обеспечения случайного перемешивания код, сформированный на второй группе выходов источника 1 псевдослучайных кодов, подается на первые входы блока 8 элементов И, на вторые входы элементов И которого поступает сигнал с пятого выхода (фиг. Зг) блока 9 управления. Этот же сигнал подключает выходы регистра 7 через второй коммутатор 5 к входам регистра 6. При этом, если в 1-м разряде псевдослучайного кода находится 1, то на соответствующем выходе блока 8 элементов И появится импульс синхронизации, поступающий через блок 10 элементов ИЛИ на синхровходы соответствующих разрядов регистров 6 и 7. Под действием этих импульсов синхронизации информация в выбранных разрядах регистров 6 и 7 меняется местами. Если в i-M разряде псевдослучайного кода содержится О, то перезаписи информации в i-M разряде между регистрами 6 и 7 не происходит,

В третьем такте работы устройства сигнал с первого выхода (фиг.ЗЛ блока 9 управления переводит блок 4 памяти в режим записи и подключает к адресным входам его через коммутатор 2 выходы регистра 3. По сигналу с второго выхода блока 9 управления содержимое регистра 7 заносится в блок 4 памяти по адресу, хранящемуся в регистре 3. В этом же такте по сигналу с шестого выхода (фиг. 3) блока 9 управления происходит формирование нового псевдослучайного кода источника 1 псевдослучайных кодов, а псевдослучайный код с второй группы его выходов переписывается в регистр 3.

В результате окончания рабочего цикла генератора на выходе регистра 7 сформировалось очередное выходное слово генератора, которое в следующем цикле будет преобразовано описанным образом и записано в блок 4 памяти по адресу, хранящемуся в регистре 3. На первой группе выходов источника 1 псевдослучайных кодов сформирован новый адрес для блока 4 памяти. Далее процесс генерации очередных выходных наборов осуществляется путем повторения рабочего цикла генератора. Источником синхронизирующих импульсов служит последовательность (фиг. За), формируемая генератором 12 тактовых импульсов блока 9 управления.

Формула изобретения

1. Генератор псевдослучайных двоичных последовательностей, содержа- щий последовательно соединенные первый регистр и второй регистр, выходы которого соединены с информационными входами блока памяти, первый и второй управляющие входы которого со динены с первым и вторым выходами соответственно блока управления, третий выход которого соединен с входом установки первого регистра, шину Пуск, соединенную с входом блока управления, отличающийся тем, что, с целью расширения функциональных возможностей за счет получения псевдослучайных последовательностей с управляемой вероятностью по явления единичного символа, он Содержит источник псевдослучайных кодо третий регистр, первый и второй коммутаторы, блок элементов И, блок элементов ИЛИ, выходы которого сое- динены с входами синхронизации соответствующих разрядов второго регистра и первого регистра, информационные входы разрядов которого соединены с соответствующими выходами вто рого коммутатора, первая группа входов которого соединена с выходами блока памяти, адресные входы которого соединены с выходами первого коммутатора, первая группа входов кото- рого соединена с выходами третьего регистра, входы которого соединены с второй группой входов первого коммутатора и с первой группой выходов источника псевдослучайных кодов, вто рая группа выходов которого соединена с первыми входами элементов И блока элементов И, выходы которого соединены с первыми входами элементов ИЛИ блока элементов ИЛИ, вторые вхо- ды элементов ИЛИ которого соединены с четвертым выходом блока управления пятый выход которого соединен с вторыми входами элементов И блока элеметов И и входом второго коммутатора, вторая группа входов которого соединена с выходами второго регистра, шетой выход блока управления соединен с управляющим входом третьего регистра и первым входом источника псевдослучайных кодов, второй вход которого соединен с третьим выходом блока управления, первый выход которого соединен с входом первого коммутатора.

2. Генератор по п. 1, отличающийся тем, что блок управления содержит генератор тактовых импульсов, схему начальной установки триггер, четыре элемента И, регистр сдвига, три элемента ИЛИ, первые входы которых соединены с входом блока управления и первым входом триггера, выход которого соединен с первым входом первого элемента И, выход которого соединен с первыми входами второго, третьего, четвертого элементов И и с входом синхронизации регистра сдвига, соответствующие выходы которого соединены с вторыми входами соответственно второго, третьего и четвертого элементов И, вы- ход второго элемента И .соединен с вторьм входом второго элемента ИЛИ и первого элемента ИЛИ, третий вход которого соединен с выходом четвертого элемента И и вторым входом третьего элемента ИЛИ, выход которого является шестым выходом блока управления , третий выход которого соединен с вторым входом триггера, первым выходом схемы начальной установки, входом управления и вторым информационным входом регистра сдвига, первый информационный вход которого соединен с выходом его последнего разряда и первым выходом блока управления, вторым, четвертым и пятым выходами которого являются соответственно выходы первого, второго элементов ИЛИ и третьего элемента И, выход генератора тактовых импульсов соединен с вторым входом первого элемента И, второй выход схемы начальной установки соединен с третьим информационным входом регистра сдвига.

Составитель Ю.Бурмистров М.Ходанич корректор И.Муска

4834/55

Тираж 816Подписное

ВНИИПИ Государственнох о комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. ПроектнанГ

q}U2.Z

физ.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Устройство для формирования тестов | 1986 |

|

SU1336013A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Генератор псевдослучайных испытательных последовательностей | 1984 |

|

SU1226621A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1352624A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

Изобретение относится к импульсной технике. Цель изобретения - расширение функциональных возможностей устройства. Генератор содержит блок 4 памяти, регистры 6 и 7 и блок 9 управления. Введение источника 1 псевдослучайных кодов, коммутаторов 2 и 5, регистра 3, блока 8 элементов И и блока 10 элементов ИЛИ позволяет получать псевдослучайные последовательности с управляемой вероятностью появления единичного сим- в ола. 1 3.п. ф-лы, 3 ил. (Л ffitrf Stal

| Генератор псевдослучайных двоичных последовательностей | 1978 |

|

SU744529A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU1013955A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-07—Публикация

1985-03-01—Подача