i

Изобретение относится к вычислительной технике и может быть использовано при построении буферных запоминающих устройств в системах передачи и приема данных, в частности при обработке информации от абоненто в порядке ее поступления.

Цель изобретения - повышение надежности запоминающего устройства.

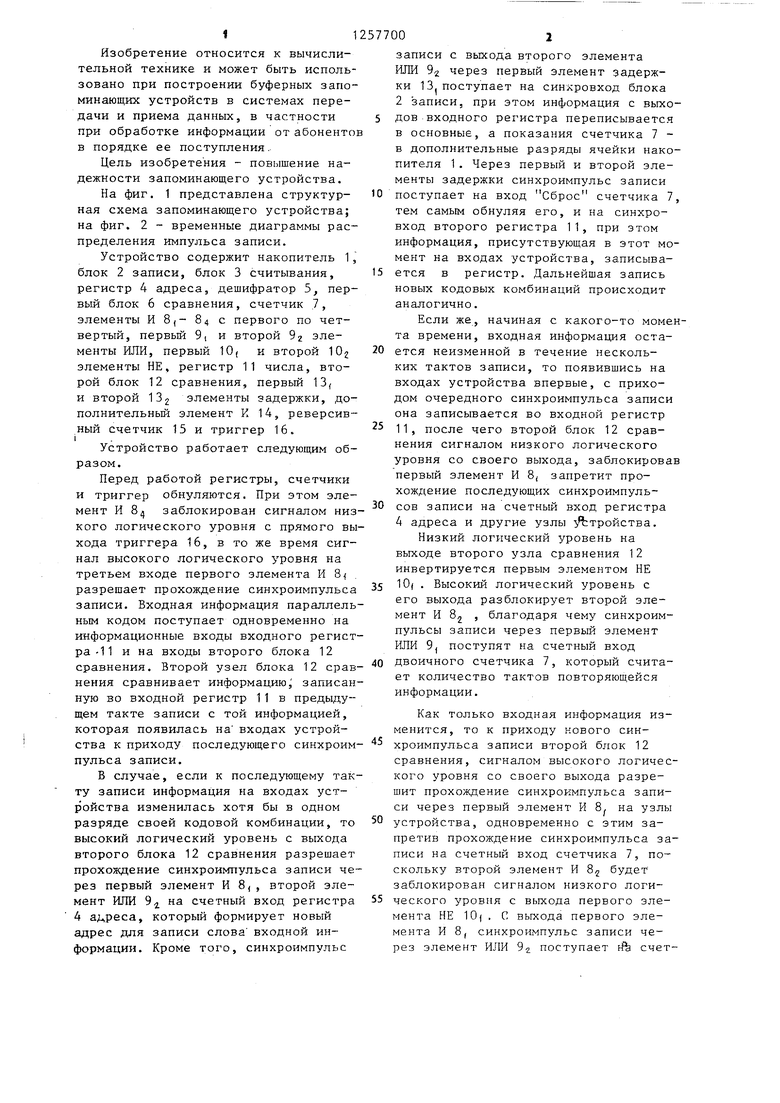

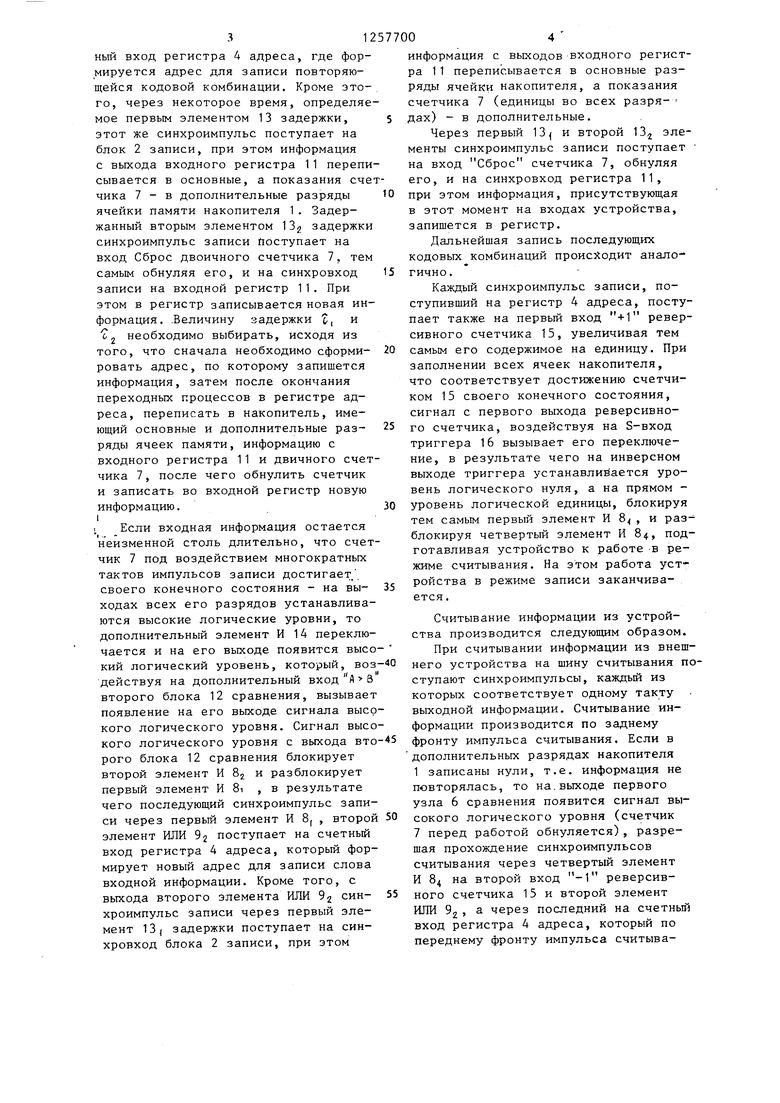

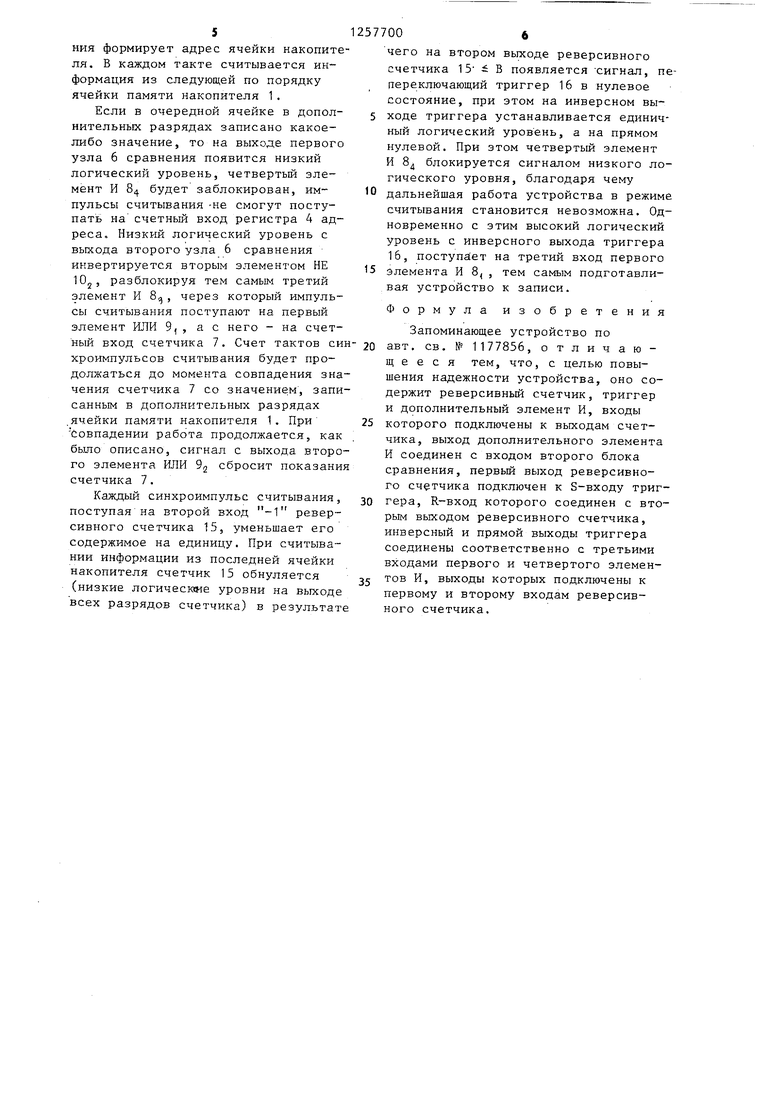

На фиг. 1 представлена структурная схема запоминающего устройства; на фиг. 2 временные диаграммы распределения импульса записи.

Устройство содержит накопитель 1 блок 2 записи, блок 3 считывания, регистр 4 адреса, дешифратор 5 первый блок 6 сравнения, счетчик 1, элементы И 8(- 84 с первого по четвертый, первый 9i и второй 9 элементы ИЛИ, первый 10( и второй lOj элементы НЕ, регистр 11 числа, второй блок 12 сравнения, первый 13( и второй 132 элементы задержки, дополнительный элемент И 14, реверсивный счетчик 15 и триггер 16. i

Устройство работает следующим образом.

Перед работой регистры, счетчики и триггер обнуляются. При этом элемент И 8 заблокирован сигналом низкого логического уровня с прямого выхода триггера 16, в то же время сигнал высокого логического уровня на третьем входе первого элемента И 8( разрешает прохождение синхроимпульса записи. Входная информация параллельным кодом поступает одновременно на информационные входы входного регистра -11 и на входы второго блока 12 сравнения. Второй узел блока 12 сравнения сравнивает информацию, записанную во входной регистр 11 в предыдущем такте записи с той информацией, которая появилась на входах устройства к приходу последующего синхроимпульса записи.

В случае, если к последующему такту записи информация на входах устройства изменилась хотя бы в одном разряде своей кодовой комбинации, то высокий логический уровень с выхода второго блока 12 сравнения разрешает прохождение синхроимпульса записи через первый элемент И 8(, второй эле

мент ИЛИ 9 на счетный вход регистра 4 адреса, который формирует новый адрес для записи слова входной информации. Кроме того, синхроимпульс

записи с выхода второго элемента ИЛИ 9 через первый элемент задержки 13| поступает на синхровход блока 2 записи, при этом информация с выходов входного регистра переписывается в основные, а показания счетчика 7 - в дополнительные разряды ячейки накопителя 1 . Через первый и второй элементы задержки синхроимпульс записи поступает на вход Сброс счетчика 7, тем самым обнуляя его, и на синхро- вход второго регистра 11, при этом информация, присутствующая в этот момент на входах устройства, записывается в регистр. Дальнейшая запись новых кодовых комбинаций происходит аналогично.

Если же, начиная с какого-то момента времени, входная информация остается неизменной в течение нескольких тактов записи, то появившись на входах устройства впервые, с приходом очередного синхроимпульса записи она записывается во входной регистр 11, после чего второй блок 12 сравнения сигналом низкого логического уровня со своего выхода, заблокировав первый элемент И 8 запретит прохождение последующих синхроимпульсов записи на счетный вход регистра 4 адреса и другие узлы Ътройства.

Низкий логический уровень на выходе второго узла сравнения 12 инвертируется первым элементом НЕ 10( . Высокий логический уровень с его выхода разблокирует второй элемент И 82 , благодаря чему синхроимпульсы записи через первый элемент ИЛИ 9, поступят на счетный вход двоичного счетчика 7, который считает количество тактов повторяющейся информации.

Как только входная информация изменится, то к приходу нового син- хроимпульса записи второй блок 12

сравнения, сигналом высокого логического уровня со своего выхода разрешит прохождение синхроимпульса записи через первый элемент И 8 на узлы устройства, одновременно с этим запретив прохождение синхроимпульса записи на счетный вход счетчика 7, поскольку второй элемент И 8 будет заблокирован сигналом низкого логического уровня с выхода первого элемента НЕ 10( . С выхода первого элемента И 8, синхроимпульс записи через элемент ИЛИ 9 поступает ift счетный вход регистра 4 адреса, где формируется адрес для записи повторяющейся кодовой комбинации. Кроме этого, через некоторое время, определяемое первым элементом 13 задержки, ; этот же синхроимпульс поступает на блок 2 записи, при этом информация с выхода входного регистра 11 переписывается в основные, а показания счетчика 7 - в дополнительные разряды ячейки памяти накопителя 1. Задержанный вторым элементом ISg задержки синхроимпульс записи Поступает на вход Сброс двоичного счетчика 7. тем самым обнуляя его, и на синхровход записи на входной регистр 11. При этом в регистр записывается новая информация. .Величину задержки J, и с-2 необходимо выбирать, исходя из

того, что сначала необходимо сформировать адрес, по которому запишется информация, затем после окончания переходных процессов в регистре адреса, переписать в накопитель, имеющий основные и дополнительные разряды ячеек памяти, информацию с входного регистра 11 и двичного счетчика 7, после чего обнулить счетчик и записать во входной регистр новую

информацию.

I

I Если входная информация остается

неизменной столь длительно, что счетчик 7 под воздействием многократных тактов импульсов записи достигает/ своего конечного состояния - на вы- ходах всех его разрядов устанавливаются высокие логические уровни, то дополнительный элемент И 14 переключается и на его выходе появится высо кий логический уровень, который, воз действуя на дополнительный вход и В второго блока 12 сравнения, вызывает появление на его выходе сигнала высокого логического уровня. Сигнал высокого логического уровня с выхода вто рого блока 12 сравнения блокирует второй элемент И 82 и разблокирует первый элемент И 8i , в результате чего последующий синхроимпульс записи через первый элемент И 8, , второй элемент ИЛИ Qj поступает на счетный вход регистра 4 адреса, который формирует новый адрес для записи слова входной информации. Кроме того, с выхода второго элемента ИЛИ Э син- хроимпульс записи через первый элемент 13) задержки поступает на синхровход блока 2 записи, при этом

; 0

5

0

5

0

0 5 5

информация с выходов входного регистра 11 переписывается в основные разряды ячейки накопителя, а показания счетчика 7 (единицы во всех разря- дах) - в дополнительные.

Через первый 13 и второй 13 элементы синхроимпульс записи поступает на вход Сброс счетчика 7, обнуляя его, и на синхровход регистра 11, при этом информация, присутствующая в этот момент на входах устройства, запишется в регистр.

Дальнейшая запись последующих кодовых комбинаций происходит аналогично.

Каждый синхроимпульс записи, поступивший на регистр 4 адреса, поступает также на первый вход +1 реверсивного счетчика 15, увеличивая тем самым его содержимое на единицу. При заполнении всех ячеек накопителя, что соответствует достижению счетчиком 15 своего конечного состояния, сигнал с первого выхода реверсивного счетчика, воздействуя на S-вход триггера 16 вызывает его переключение, в результате чего на инверсном выходе триггера устанавлив ается уровень логического нуля, а на прямом - уровень логической единицы, блокируя тем самым первый элемент И 8, и разблокируя четвертый элемент И 84, подготавливая устройство к работе -в режиме считывания. На этом работа устройства в режиме записи заканчивается .

Считывание информации из устройства производится следующим образом.

При считывании информации из внешнего устройства на шину считывания поступают синхроимпульсы, каждый из которых соответствует одному такту выходной информации. Считывание информации производится по заднему фронту импульса считывания. Если в дополнительных разрядах накопителя 1 записаны нули, т.е. информация не повторялась, то на.выходе первого узла 6 сравнения появится сигнал высокого логического уровня (счетчик 7 перед работой обнуляется), разрешая прохождение синхроимпульсов считывания через четвертый элемент И 8 на второй вход -1 реверсивного счетчика 15 и второй элемент ИЛИ 92 , а через последний на счетньй вход регистра 4 адреса, который по переднему фронту импульса считыва

5

ния формирует адрес ячейки накопитля. В каждом такте считывается информация из следующей по порядку ячейки памяти накопителя 1.

Если в очередной ячейке в дополнительных разрядах записано какое- либо значение, то на выходе первог узла 6 сравнения появится низкий логический уровень, четвертьй элемент И 84 будет заблокирован, импульсы считывания -не смогут поступать на счетньш вход регистра 4 адреса. Низкий логический уровень с выхода второго узла 6 сравнения инвертируется вторым элементом НЕ 10, разблокируя тем самым третий элемент И 8, через который импульсы считывания поступают на первый элемент ИЛИ 9,, ас него - на счетный вход счетчика 7. Счет тактов схроимпульсов считывания будет продолжаться до момента совпадения знчения счетчика 7 со значением, запсанным в дополнительных разрядах .ячейки памяти накопителя 1. При совпадении работа продолжается, ка было описано, сигнал с выхода вторго элемента ИЛИ 9, сбросит показан счетчика 7.

Каждый синхроимпульс считывания поступая на второй вход -1 реверсивного счетчика 15, уменьшает его содержимое на единицу. При считывании информации из последней ячейки накопителя счетчик 15 обнуляется (низкие логические уровни на выход всех разрядов счетчика) в результа

0

5

0

5

0

5

чего на втором выходе реверсивного счетчика 15 - В появляется сигнал, пе- переключающий триггер 16 в нулевое состояние, при этом на инверсном выходе триггера устанавливается единичный логический уровень, а на прямом нулевой. При этом четвертый элемент И 8д блокируется сигналом низкого логического уровня, благодаря чему дальнейшая работа устройства в режиме считывания становится невозможна. Одновременно с этим высокий логический уровень с инверсного выхода триггера 16, поступает на третий вход первого элемента И 8 , тем самым подготавливая устройство к записи.

Формула изобретения

Запоминающее устройство по авт. св. № 1177856, отличающееся тем, что, с целью повышения надежности устройства, оно содержит реверсивньй счетчик, триггер и дополнительный элемент И, входы которого подключены к выходам счетчика, выход дополнительного элемента И соединен с входом второго блока сравнения, первый выход реверсивного счетчика подключен к S-входу триггера, R-вход которого соединен с вторым выходом реверсивного счетчика, инверсный и прямой выходы триггера соединены соответственно с третьими входами первого и четвертого элементов И, выходы которых подключены к первому и второму входам реверсивного счетчика.

Cu xpecu9ffeff CVUff eoMu

Ct/ffxpactifffojr Записи

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательное буферное запоминающее устройство | 1986 |

|

SU1332383A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1397968A1 |

| Запоминающее устройство | 1984 |

|

SU1177856A1 |

| Устройство для приема дискретной информации в системах с решающей обратной связью | 1986 |

|

SU1478361A1 |

| Устройство для задержки цифровой информации с контролем | 1987 |

|

SU1462424A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Информационное устройство | 1987 |

|

SU1564066A1 |

| Устройство для сопряжения ЦВМ и накопителя информации | 1985 |

|

SU1265780A1 |

| Способ записи - воспроизведения цифровой информации и устройство для его осуществления | 1990 |

|

SU1721630A1 |

| Блок задержки цифровой информации с самоконтролем | 1986 |

|

SU1368922A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении буферных запоминающих устройств в . системах передави и приема данных. в частности при обработке информа- дии от абонентов в порядке ее поступления. Целью изобретения является повышение надежности устройства. Введение в устройство реверсивного счетчика, триггера и дополнительного элемента И позволяет фиксировать заполнение накопителя при записи в него информации, а также подготовить устройство к считыванию информации. При считывании информации из последней ячейки накопителя реверсивный счетчик обнуляется, благодаря чему дальнейшая работа устройства в режиме считывания становится невозможной. Изобретение дополнительное к авт. св. № 1177856, 2 ил. (Л СП -|

(pue.2

Составитель 0. Кулаков Редактор Ю. Середа Техред Л.Олейник Корректор Г. Решетник

Заказ 4964/50 Тираж 671Подписное .

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

t

| Патент Великобритании № 1356287, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Запоминающее устройство | 1984 |

|

SU1177856A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-09-15—Публикация

1984-11-10—Подача