Изобретение относится к импульсной технике и может быть использовано при построении резервированной аппаратуры с логическими элементами.

Целью изобретения является повышение достоверности функционирования мажоритарного элемента.

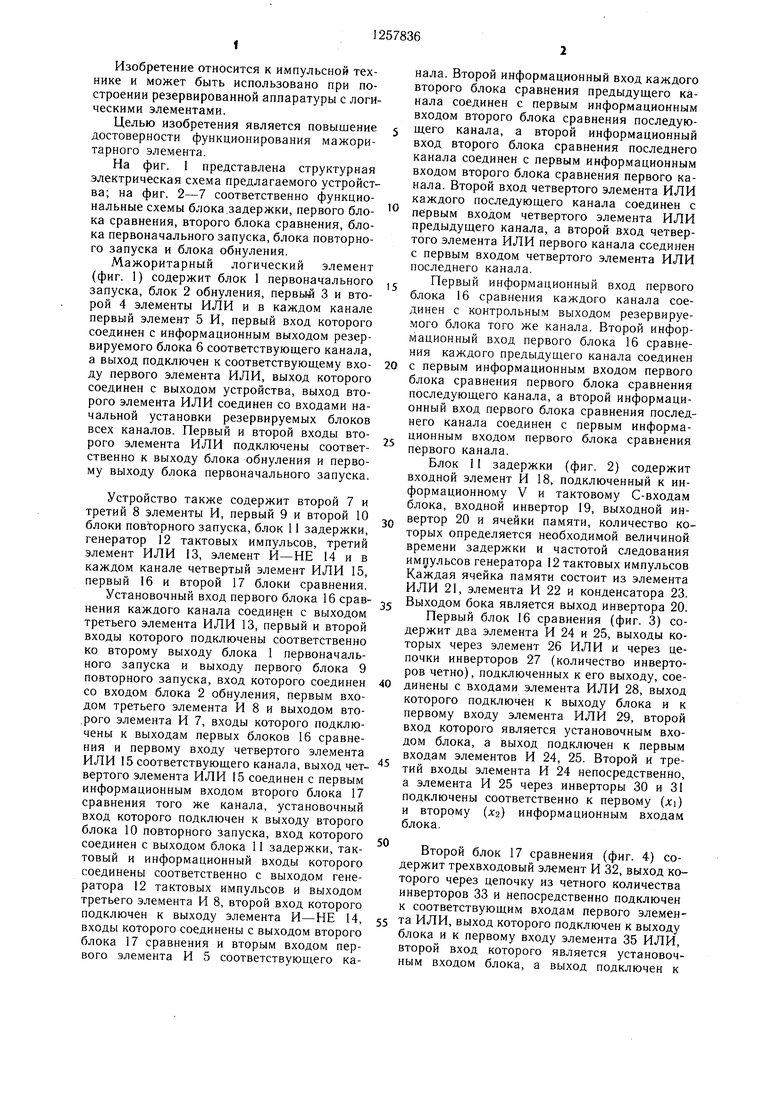

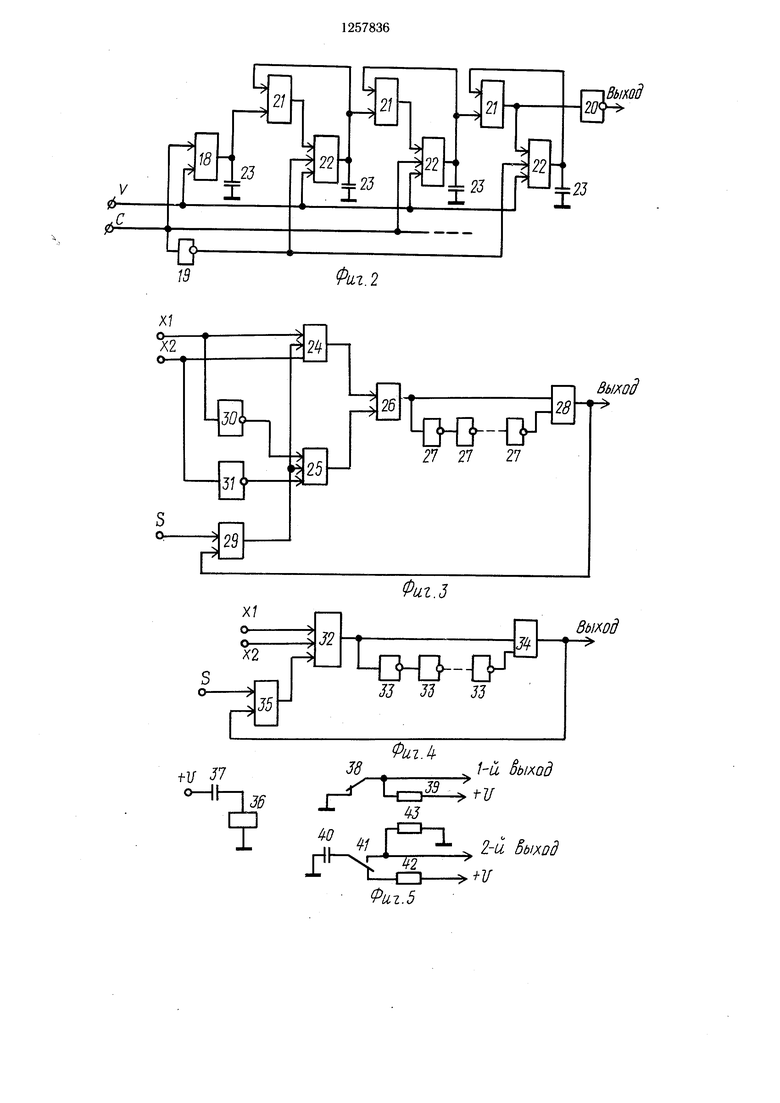

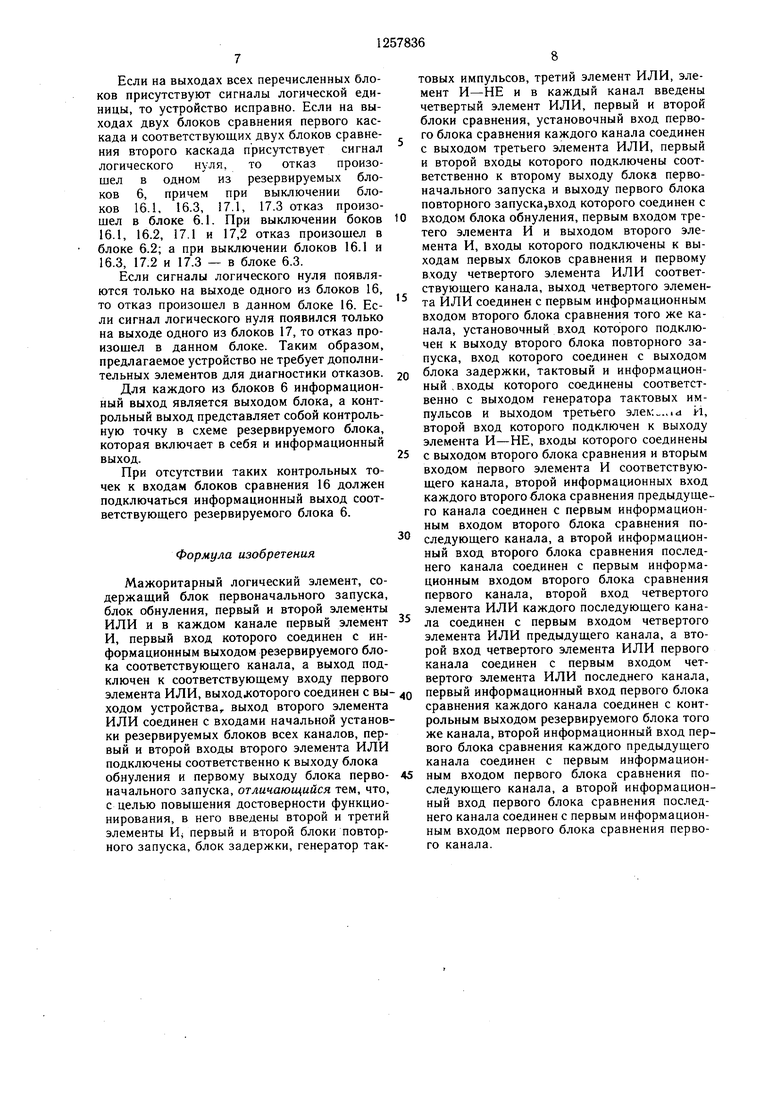

На фиг. 1 представлена структурная электрическая схема предлагаемого устройства; на фиг. 2-7 соответственно функциональные схемы блока.задержки, первого блока сравнения, второго блока сравнения, блока первоначального запуска, блока повторного запуска и блока обнуления.

Мажоритарный логический элемент (фиг. 1) содержит блок 1 первоначального запуска, блок 2 обнуления, первый 3 и второй 4 элементы ИЛИ и в каждом канале первый элемент 5 И, первый вход которого соединен с информационным выходом резервируемого блока 6 соответствующего канала, а выход подключен к соответствующему входу первого элемента ИЛИ, выход которого соединен с выходом устройства, выход второго элемента ИЛИ соединен со входами начальной установки резервируемых блоков всех каналов. Первый и второй входы второго элемента ИЛИ подключены соответственно к выходу блока обнуления и первому выходу блока первоначального запуска.

Устройство также содержит второй 7 и третий 8 элементы И, первый 9 и второй 10 блоки повторного запуска, блок 11 задержки, генератор 12 тактовых импульсов, третий элемент ИЛИ 13, элемент И-НЕ 14 и в каждом канале четвертый элемент ИЛИ 15, первый 16 и второй 17 блоки сравнения.

Установочный вход первого блока 16 сравнения каждого канала соединен с выходом третьего элемента ИЛИ 13, первый и второй входы которого подключены соответственно ко второму выходу блока 1 первоначального запуска и выходу первого блока 9 повторного запуска, вход которого соединен со входом блока 2 обнуления, первым входом третьего элемента И 8 и выходом вто- .рого элемента И 7, входы которого подключены к выходам первых блоков 16 сравнения и первому входу четвертого элемента ИЛИ 15 соответствующего канала, выход четвертого элемента ИЛИ 15 соединен с первым информационным входом второго блока 17 сравнения того же канала, установочный вход которого подключен к выходу второго блока 10 повторного запуска, вход которого соединен с выходом блока 11 задержки, тактовый и информационный входы которого соединены соответственно с выходом генератора 12 тактовых импульсов и выходом третьего элемента И 8, второй вход которого подключен к выходу элемента И-НЕ 14, входы которого соединены с выходом второго блока 17 сравнения и вторым входом первого элемента И 5 соответствующего ка

нала. Второй информационный вход каждого второго блока сравнения предыдущего канала соединен с первым информационным входом второго блока сравнения последующего канала, а второй информационный вход второго блока сравнения последнего канала соединен с первым информационным входом второго блока сравнения первого канала. Второй вход четвертого элемента ИЛИ каждого последующего канала соединен с первым входом четвертого элемента ИЛИ предыдущего канала, а второй вход четвертого элемента ИЛИ первого канала соединен с первым входом четвертого элемента ИЛИ последнего канала.

Первый информационный вход первого блока 16 сравнения каждого канала соединен с контрольным выходом резервируемого блока того же канала. Второй информационный вход первого блока 16 сравнения каждого предыдущего канала соединен

0 С первым информационным входом первого блока сравнения первого блока сравнения последующего канала, а второй информационный вход первого блока сравнения последнего канала соединен с первым информационным входом первого блока сравнения первого канала.

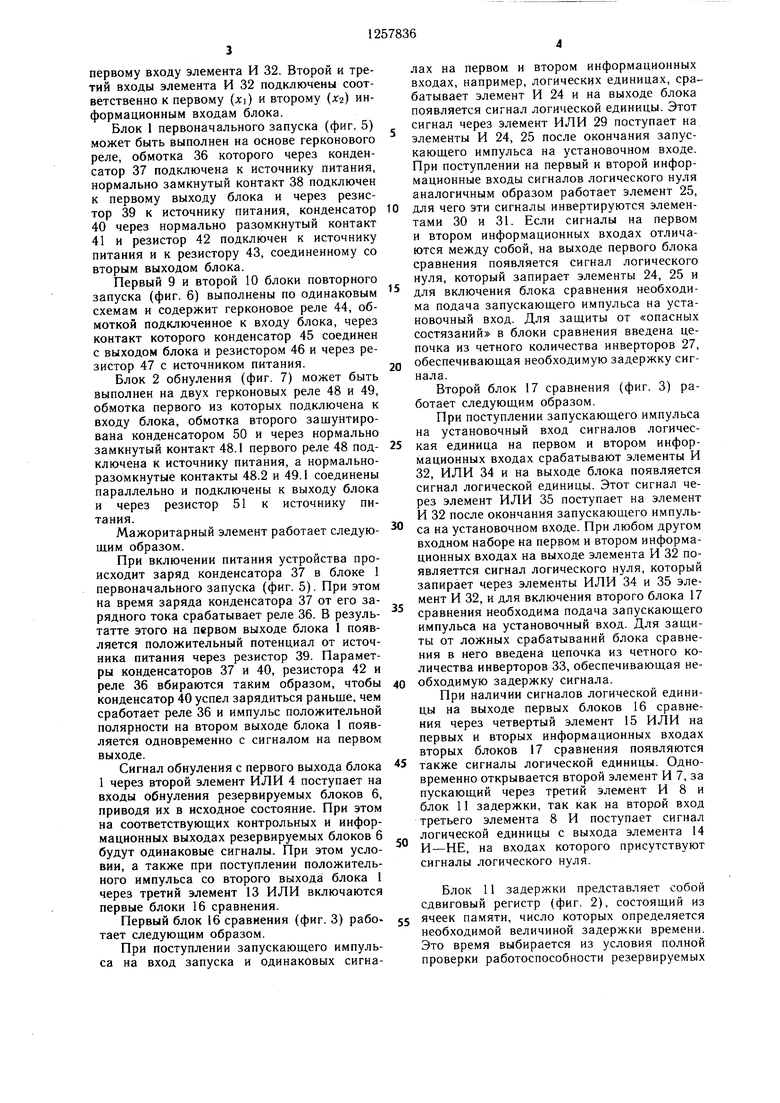

Блок 11 задержки (фиг. 2) содержит входной элемент И 18, подключенный к информационному V и тактовому С-входам блока, входной инвертор 19, выходной инQ вертор 20 и ячейки памяти, количество которых определяется необходимой величиной времени задержки и частотой следования импульсов генератора 12 тактовых импульсов Каждая ячейка памяти состоит из элемента ИЛИ 21, элемента И 22 и конденсатора 23.

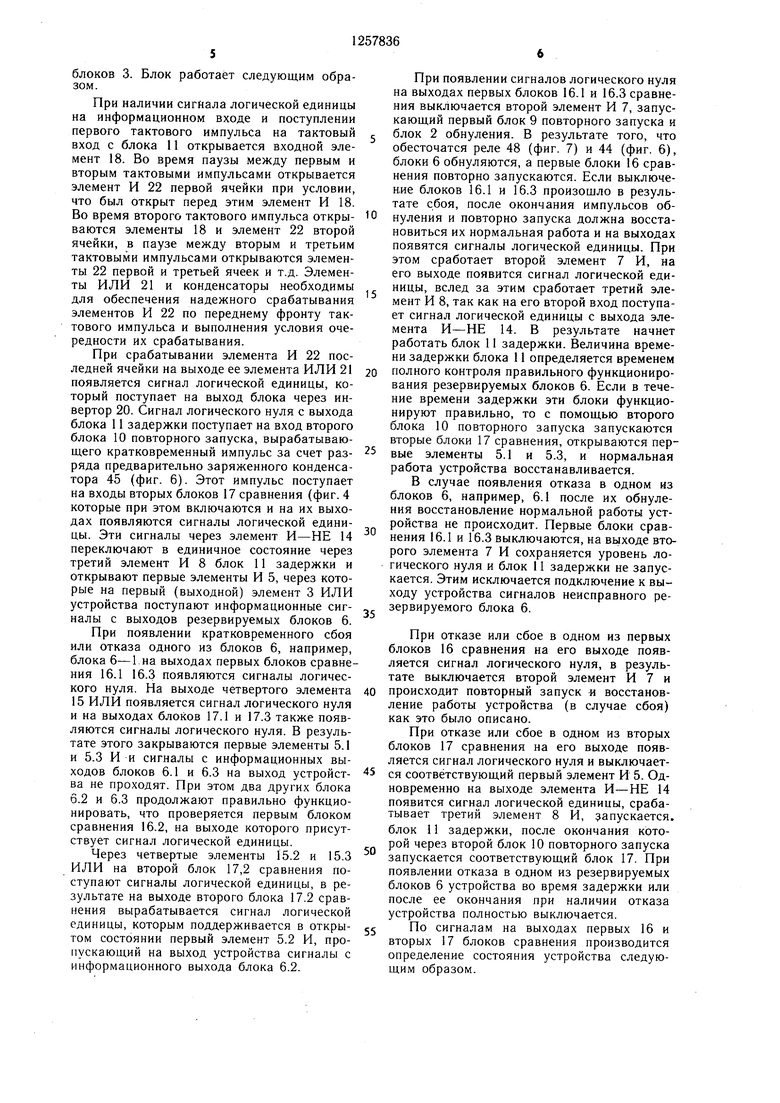

5 Выходом бока является выход инвертора 20. Первый блок 16 сравнения (фиг. 3) содержит два элемента И 24 и 25, выходы которых через элемент 26 ИЛИ и через цепочки инверторов 27 (количество инверторов четно), подключенных к его выходу, сое0 динены с входами элемента ИЛИ 28, выход которого подключен к выходу блока и к первому входу элемента ИЛИ 29, второй вход которого является установочным входом блока, а выход подключен к первым входам элементов И 24, 25. Второй и тре- тий входы элемента И 24 непосредственно, а элемента И 25 через инверторы 30 и 31 подключены соответственно к первому (xi) и второму (лга) информационным входам блока.

Второй блок 17 сравнения (фиг. 4) содержит трехвходовый элемент И 32, выход которого через цепочку из четного количества инверторов 33 и непосредственно подключен к соответствующим входам первого элемен- 5 та ИЛИ, выход которого подключен к выходу блока и к первому входу элемента 35 ИЛИ, второй вход которого является установочным входом блока, а выход подключен к

первому входу элемента И 32. Второй и третий входы элемента И 32 подключены соответственно к первому (х) и второму (2) информационным входам блока.

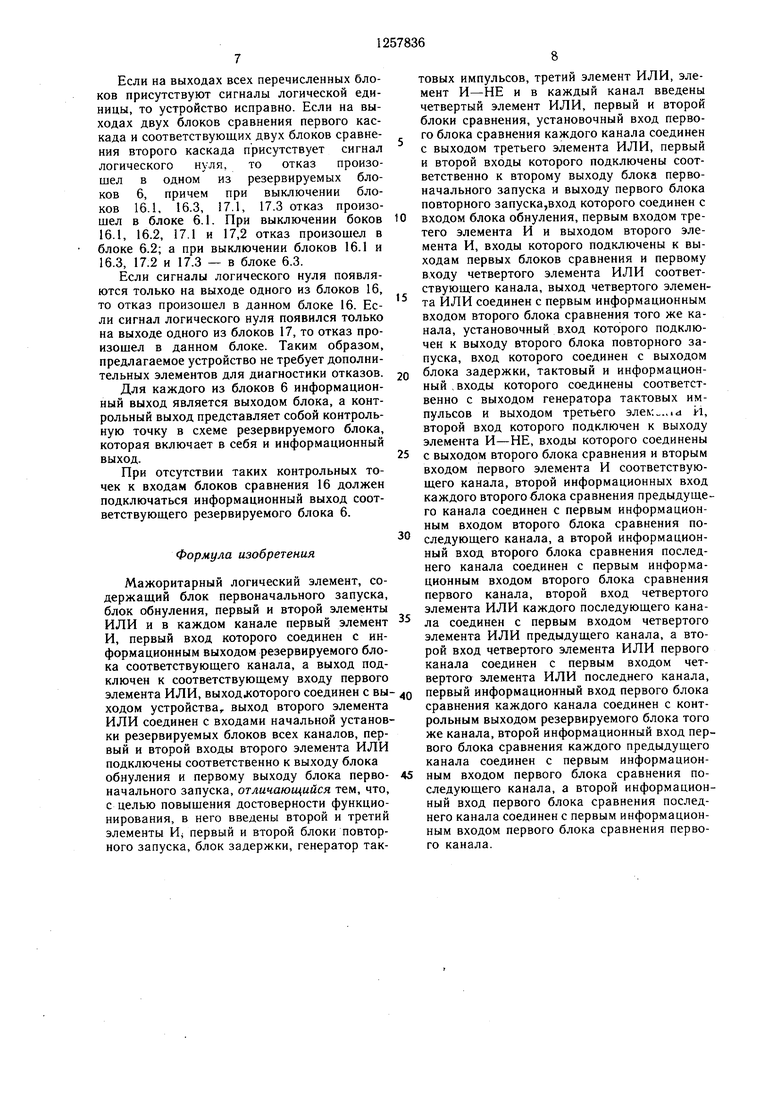

Блок 1 первоначального запуска (фиг. 5) может быть выполнен на основе герконового реле, обмотка 36 которого через конденсатор 37 подключена к источнику питания, нормально замкнутый контакт 38 подключен к первому выходу блока и через резистор 39 к источнику питания, конденсатор

40через нормально разомкнутый контакт

41и резистор 42 подключен к источнику питания и к резистору 43, соединенному со вторым выходом блока.

Первый 9 и второй 10 блоки повторного запуска (фиг. 6) выполнены по одинаковым схемам и содержит герконовое реле 44, обмоткой подключенное к входу блока, через контакт которого конденсатор 45 соединен с выходом блока и резистором 46 и через резистор 47 с источником питания.

Блок 2 обнуления (фиг. 7) может быть выполнен на двух герконовых реле 48 и 49, обмотка первого из которых подключена к входу блока, обмотка второго зашунтиро- вана конденсатором 50 и через нормально замкнутый контакт 48.1 первого реле 48 под- ключена к источнику питания, а нормально- разомкнутые контакты 48.2 и 49.1 соединены параллельно и подключены к выходу блока и через резистор 51 к источнику питания.

Мажоритарный элемент работает следующим образом.

При включении питания устройства происходит заряд конденсатора 37 в блоке 1 первоначального запуска (фиг. 5). При этом на время заряда конденсатора 37 от его зарядного тока срабатывает реле 36. В резуль- татте этого на первом выходе блока 1 появляется положительный потенциал от источника питания через резистор 39. Параметры конденсаторов 37 н 40, резистора 42 и реле 36 вбираются таким образом, чтобы конденсатор 40 успел зарядиться раньше, чем сработает реле 36 и импульс положительной полярности на втором выходе блока 1 появляется одновременно с сигналом на первом выходе.

Сигнал обнуления с первого выхода блока 1 через второй элемент ИЛИ 4 поступает на входы обнуления резервируемых блоков 6, приводя их в исходное состояние. При этом на соответствующих контрольных и информационных выходах резервируемых блоков 6 будут одинаковые сигналы. При этом условии, а также при поступлении положительного импульса со второго выхода блока 1 через третий элемент 13 ИЛИ включаются первые блоки 16 сравнения.

Первый блок 16 сравнения (фиг. 3) рабо- тает следующим образом.

При поступлении запускающего импульса на вход запуска и одинаковых сигна

5

0

0

5

0

5

5

0

5

0

лах на первом и втором информационных входах, например, логических единицах, срабатывает элемент И 24 и на выходе блока появляется сигнал логической единицы. Этот сигнал через Эv eмeнт ИЛИ 29 поступает на элементы И 24, 25 после окончания запускающего импульса на установочном входе. При поступлении на первый и второй информационные входы сигналов логического нуля аналогичным образом работает элемент 25, для чего эти сигналы инвертируются элементами 30 и 31. Если сигналы на первом и втором информационных входах отличаются между собой, на выходе первого блока сравнения появляется сигнал логического нуля, который запирает элементы 24, 25 и для включения блока сравнения необходима подача запускающего импульса на установочный вход. Для защиты от «опасных состязаний в блоки сравнения введена цепочка из четного количества инверторов 27, обеспечивающая необходимую задержку сигнала.

Второй блок 17 сравнения (фиг. 3) работает следующим образом.

При поступлении запускающего импульса на установочный вход сигналов логическая единица на первом и втором информационных входах срабатывают элементы И 32, ИЛИ 34 и на выходе блока появляется сигнал логической единицы. Этот сигнал через элемент ИЛИ 35 поступает на элемент И 32 после окончания запускающего импульса на установочном входе. При любом другом входном наборе на перром и втором информационных входах на выходе элемента И 32 по- являеттся сигнал логического нуля, который запирает через элементы ИЛИ 34 и 35 элемент И 32, и для включения второго блока 17 сравнения необходима подача запускающего импульса на установочный вход. Для защиты от ложных срабатываний блока сравнения в него введена цепочка из четного количества инверторов 33, обеспечивающая необходимую задержку сигнала.

При наличии сигналов логической единицы на выходе первых блоков 16 сравнения через четвертый элемент 15 ИЛИ на первых и вторых информационных входах вторых блоков 17 сравнения появляются также сигналы логической единицы. Одновременно открывается второй элемент И 7, за пускающий через третий элемент И 8 и блок 11 задержки, так как на второй вход третьего элемента 8 И поступает сигнал логической единицы с выхода элемента 14 И-НЕ, на входах которого присутствуют сигналы логического нуля.

Блок 11 задержки представляет собой сдвиговый регистр (фиг. 2), состоящий из ячеек памяти, число которых определяется необходимой величиной задержки времени. Это время выбирается из условия полной проверки работоспособности резервируемых

блоков 3. Блок работает следующим образом.

При наличии сигнала логической единицы на информационном входе и поступлении первого тактового импульса на тактовый вход с блока 11 открывается входной элемент 18. Во время паузы между первым и вторым тактовыми импульсами открывается элемент И 22 первой ячейки при условии, что был открыт перед этим элемент И 18. Во время второго тактового импульса откры- ваются элементы 18 и элемент 22 второй ячейки, в паузе между вторым и третьим тактовыми импульсами открываются элементы 22 первой и третьей ячеек и т.д. Элементы ИЛИ 21 и конденсаторы необходимы для обеспечения надежного срабатывания элементов И 22 по переднему фронту тактового импульса и выполнения условия очередности их срабатывания.

При срабатывании элемента И 22 последней ячейки на выходе ее элемента ИЛИ 21 появляется сигнал логической единицы, который поступает на выход блока через инвертор 20. Сигнал логического нуля с выхода блока 11 задержки поступает на вход второго блока 10 повторного запуска, вырабатывающего кратковременный импульс за счет раз- ряда предварительно заряженного конденсатора 45 (фиг. 6). Этот импульс поступает на входы вторых блоков 17 сравнения (фиг. 4 которые при этом включаются и на их выходах появляются сигналы логической единицы. Эти сигналы через элемент И-НЕ 14 переключают в единичное состояние через третий элемент И 8 блок 11 задержки и открывают первые элементы И 5, через которые на первый (выходной) элемент 3 ИЛИ устройства поступают информационные сиг- налы с выходов резервируемых блоков 6.

При появлении кратковременного сбоя или отказа одного из блоков 6, например, блока 6-1 на выходах первых блоков сравнения 16.1 16.3 появляются сигналы логического нуля. На выходе четвертого элемента 15 ИЛИ появляется сигнал логического нуля и на выходах блоков 17.1 и 17.3 также появляются сигналы логического нуля. В результате этого закрываются первые элементы 5.1 и 5.3 И и сигналы с информационных выходов блоков 6.1 и 6.3 на выход устройст- ва не проходят. При этом два других блока 6.2 и 6.3 продолжают правильно функционировать, что проверяется первым блоком сравнения 16.2, на выходе которого присутствует сигнал логической единицы.

Через четвертые элементы 15.2 и 15.3 ИЛИ на второй блок 17,2 сравнения поступают сигналы логической единицы, в результате на выходе второго блока 17.2 сравнения вырабатывается сигнал логической единицы, которым поддерживается в откры- том состоянии первый элемент 5.2 И, пропускающий на выход устройства сигналы с информационного выхода блока 6.2.

При появлении сигналов логического нуля на выходах первых блоков 16.1 и 16.3 сравнения выключается второй элемент И 7, запускающий первый блок 9 повторного запуска и блок 2 обнуления. В результате того, что обесточатся реле 48 (фиг. 7) и 44 (фиг. 6), блоки 6 обнуляются, а первые блоки 16 сравнения повторно запускаются. Если выключение блоков 16.1 и 16.3 произошло в результате сбоя, после окончания импульсов обнуления и повторно запуска должна восстановиться их нормальная работа и на выходах появятся сигналы логической единицы. При этом сработает второй элемент 7 И, на его выходе появится сигнал логической единицы, вслед за этим сработает третий элемент И 8, так как на его второй вход поступает сигнал логической единицы с выхода элемента И-НЕ 14. В результате начнет работать блок 11 задержки. Величина времени задержки блока 11 определяется временем полного контроля правильного функционирования резервируемых блоков 6. Если в течение времени задержки эти блоки функционируют правильно, то с помощью второго блока 10 повторного запуска запускаются вторые блоки 17 сравнения, открываются первые элементы 5.1 и 5.3, и нормальная работа устройства восстанавливается.

В случае появления отказа в одном из блоков 6, например, 6.1 после их обнуления восстановление нормальной работы устройства не происходит. Первые блоки сравнения 16.1 и 16.3 выключаются, на выходе второго элемента 7 И сохраняется уровень логического нуля и блок 11 задержки не запускается. Этим исключается подключение к выходу устройства сигналов неисправного резервируемого блока 6.

При отказе или сбое в одном из первых блоков 16 сравнения на его выходе появляется сигнал логического нуля, в результате выключается второй элемент И 7 и происходит повторный запуск и восстановление работы устройства (в случае сбоя) как это было описано.

При отказе или сбое в одном из вторых блоков 17 сравнения на его выходе появляется сигнал логического нуля и выключается соответствующий первый элемент И 5. Одновременно на выходе элемента И-НЕ 14 появится сигнал логической единицы, срабатывает третий элемент 8 И, запускается, блок 11 задержки, после окончания которой через второй блок 10 повторного запуска запускается соответствующий блок 17. При появлении отказа в одном из резервируемых блоков 6 устройства во время задержки или после ее окончания при наличии отказа устройства полностью выключается.

По сигналам на выходах первых 16 и вторых 17 блоков сравнения производится определение состояния устройства следующим образом.

Если на выходах всех перечисленных блоков присутствуют сигиалы логической единицы, то устройство исправно. Если на выходах двух блоков сравнения первого каскада и соответствующих двух блоков сравнения второго каскада присутствует сигнал логического нуля, то отказ произошел в одном из резервируемых блоков 6, причем при выключении блоков 16.1, 16.3, 17.1, 17.3 отказ произошел в блоке 6.1. При выключении боков 16.1, 16.2, 17.1 и 17,2 отказ произошел в блоке 6.2; а при выключении блоков 16.1 и 16.3, 17.2 и 17.3 - в блоке 6.3.

Если сигналы логического нуля появляются только на выходе одного из блоков 16, то отказ произошел в данном блоке 16. Если сигнал логического нуля появился только на выходе одного из блоков 17, то отказ произошел в данном блоке. Таким образом, предлагаемое устройство не требует дополнительных элементов для диагностики отказов.

Для каждого из блоков 6 информационный выход является выходом блока, а контрольный выход представляет собой контрольную точку в схеме резервируемого блока, которая включает в себя и информационный выход.

При отсутствии таких контрольных точек к входам блоков сравнения 16 должен подключаться информационный выход соответствующего резервируемого блока 6.

Формула изобретения

Мажоритарный логический элемент, содержащий блок первоначального запуска, блок обнуления, первый и второй элементы ИЛИ и в каждом канале первый элемент И, первый вход которого соединен с информационным выходом резервируемого блока соответствующего канала, а выход подключен к соответствующему входу первого элемента ИЛИ, выходлоторого соединен с вы ходом устройства, выход второго элемента ИЛИ соединен с входами начальной установки резервируемых блоков всех каналов, первый и второй входы второго элемента ИЛИ подключены соответственно к выходу блока обнуления и первому выходу блока перво- начального запуска, отличающийся тем, что, с целью повышения достоверности функционирования, в него введены второй и третий элементы И; первый и второй блоки повторного запуска, блок задержки, генератор так

0

5

5

0

о 5

товых импульсов, третий элемент ИЛИ, элемент И-НЕ и в каждый канал введены четвертый элемент ИЛИ, первый и второй блоки сравнения, установочный вход первого блока сравнения каждого канала соединен с выходом третьего элемента ИЛИ, первый и второй входы которого подключены соответственно к второму выходу блока первоначального запуска и выходу первого блока повторного запуска,вход которого соединен с входом блока обнуления, первым входом тре- тего элемента И и выходом второго элемента И, входы которого подключены к выходам первых блоков сравнения и первому входу четвертого элемента ИЛИ соответствующего канала, выход четвертого элемента ИЛИ соединен с первым информационным входом второго блока сравнения того же канала, установочный вход которого подключен к выходу второго блока повторного запуска, вход которого соединен с выходом блока задержки, тактовый и информационный .входы которого соединены соответственно с выходом генератора тактовых импульсов и выходом третьего элем..1й И, второй вход которого подключен к выходу элемента И-НЕ, входы которого соединены с выходом второго блока сравнения и вторым входом первого элемента И соответствующего канала, второй информационных вход каждого второго блока сравнения предыдущего канала соединен с первым информационным входом второго блока сравнения последующего канала, а второй информационный вход второго блока сравнения последнего канала соединен с первым информационным входом второго блока сравнения первого канала, второй вход четвертого элемента ИЛИ каждого последующего канала соединен с первым входом четвертого элемента ИЛИ предыдущего канала, а второй вход четвертого элемента ИЛИ первого канала соединен с первым входом четвертого элемента ИЛИ последнего канала, первый информационный вход первого блока сравнения каждого канала соединен с контрольным выходом резервируемого блока того же канала, второй информационный вход первого блока сравнения каждого предыдущего канала соединен с первым информационным входом первого блока сравнения последующего канала, а второй информационный вход первого блока сравнения последнего канала соединен с первым информационным входом первого блока сравнения первого канала.

2-й Sbixod

Фаг.5

В)(0д 0

44

Ti

Выход

Фиг.6

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство мажоритарного контроля резервируемых логических блоков | 1984 |

|

SU1256193A1 |

| Устройство для мажоритарного включения резервируемых логических блоков | 1985 |

|

SU1325727A1 |

| Устройство для контроля микропроцессорных систем | 1987 |

|

SU1425679A1 |

| Устройство для реконфигурации резервируемых блоков | 1990 |

|

SU1748155A1 |

| Резервируемое устройство | 1990 |

|

SU1732505A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

| Устройство для микропрограммногоупРАВлЕНия C КОНТРОлЕМ | 1979 |

|

SU809183A1 |

| СПОСОБ УПРАВЛЕНИЯ ДУБЛИРОВАННОЙ СИСТЕМОЙ С ЗАДЕРЖКОЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1999 |

|

RU2147162C1 |

| Устройство для контроля и реконфигурации дублированной системы | 1990 |

|

SU1815641A1 |

| Многоканальное программно-временное устройство | 1985 |

|

SU1280570A1 |

Устройство относится к импульсной технике, может быть использовано при построении резервированной аппаратуры с логическими элементами. Целью изобретения является повышение достоверности функционирования мажоритарного элемента. Для достижения поставленной цели в устройство, содержащее блок 1 первоначального запуска, блок 2 обнуления, первый 3 и второй 4 элементы ИЛИ и в каждом канале первый элемент И 5, резервируемый блок 6, введены второй 7 и третий 8 элементы И, блоки 9 и 10 повторного запуска, блок 11 задержки, генератор 12 тактовых импульсов, элемент ИЛИ 13, элемент И-НЕ 14. Также в каждый канал дополнительно введены элемент ИЛИ 15, блоки 16, 17 сравнения. В описании изобретения представлены функциональные схемы блока задержки, первого и второго блоков сравнения, блоков первоначального и повторного запуска, блока обнуления. По сигналам на выходах первых 16 и вторых 17 блоков сравнения произво-- дится определение состояния устройства. Данное устройство не требует дополнительных элементов для диагностики отказов. 7 ил. (Л г-1 Hh ю О1 00 оо О5

,f

Выход

| Шевцов Г | |||

| А | |||

| Логическое резервирование | |||

| Львов, Изд-во Львовского университета, Л., ,1973, с | |||

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| Белецкий В | |||

| В | |||

| Теория и практические методы резервирования радиоэлектронной ап | |||

| паратуры | |||

| М.: Энергия, 1977, с | |||

| Паровозный золотник (байпас) | 1921 |

|

SU153A1 |

Авторы

Даты

1986-09-15—Публикация

1985-04-03—Подача