10

20

25

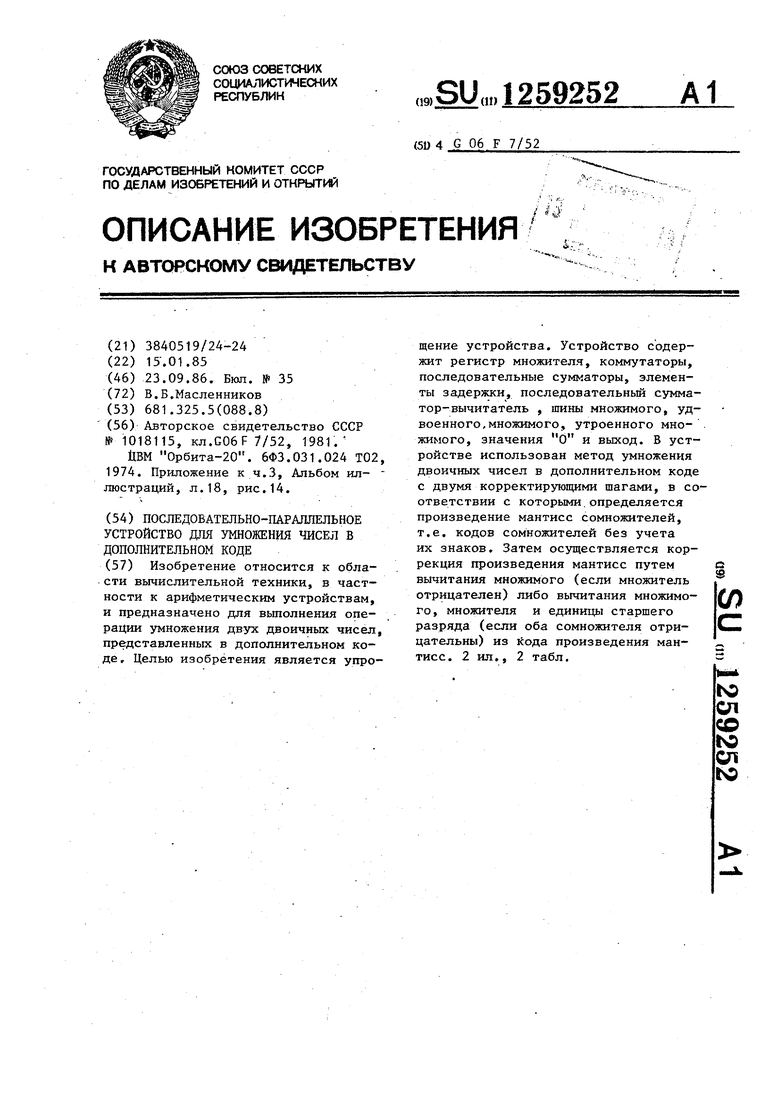

Изобретение относится к вычисли™ ельной технике, а конкретно к арифетическим устройствам, и предназнаено для умножения двух двоичных чиел, представленных в дополнительном оде.

Целью изобретения является упроение устройства.

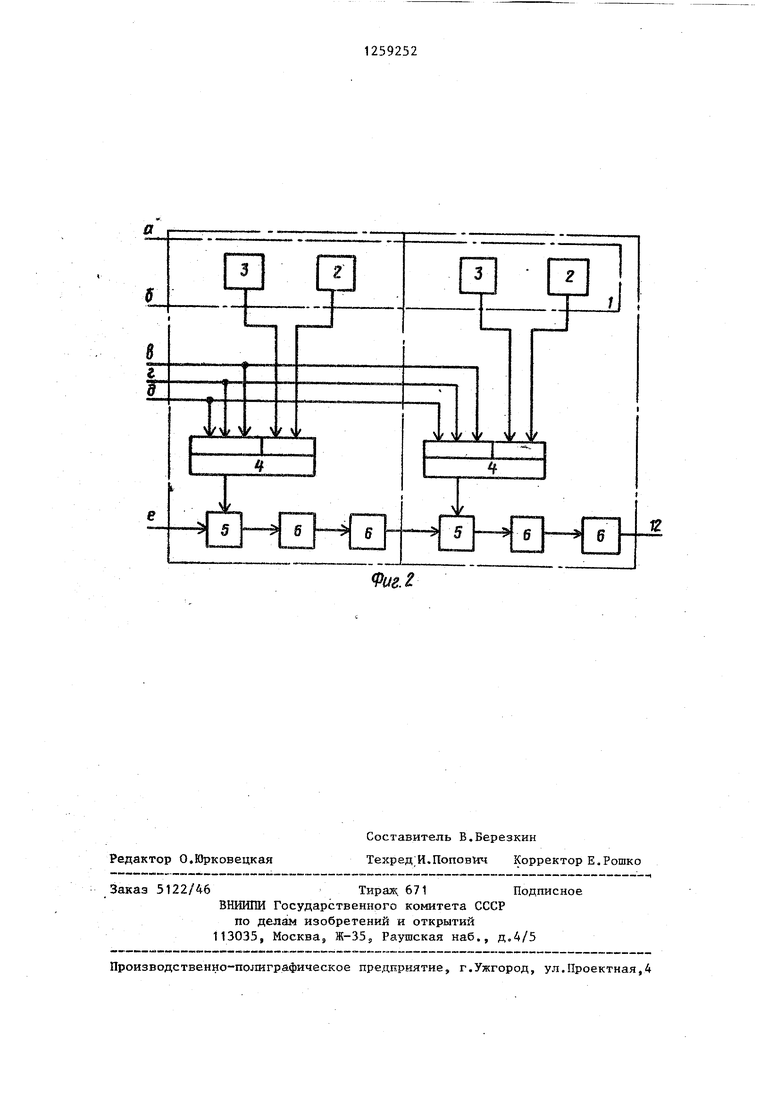

На фиг.1 и 2 приведена функциональная схема предлагаемого устройства.

Устройство содержит регистр 1 множителя, имеющий нечетные и четные разряды 2 и 3 (последний четный разряд 3 регистра 1 является знаковым), коммутаторы 4, последовательные сумматоры 5, элементы 6 задержки, по- ; следовательный сумматор-вычитатель 7, шину 8 множимого, шину 9 удвоенного множимого, шину 10 утроенного множимого, шину 11 значения О,выход 12. Устройство работает следующим образом.

Множитель записывается в регистр и хранится в нем в течение всей операции умножения в параллельном коде. Мантисса множимого поступает в устройство в последовательном коде по шинам 8 (М), 9(2М) и 10(ЗМ), В устройстве использован метод умножения двоичных чисел в дополнительном к,о- де с двумя корректирующими шагами, в соответствии с которым определяется произведение мантисс сомножителей, т.е. кодов сомножителей без учета их знаков, затем осуществляется коррекция произведения мантисс путем вычитания множимого (если множитель от- рицателен) либо вычитания множителя (если множимое отрицательно), либо вычитания множимого, множителя и еди- 40 ницы старшего разряда (если оба сомножителя отрицательны) из кода произведения мантисс.

В зависимости от значения разрядов множителя, составляющих соответствующую пару, коммутатор 4 формирует частичное произведение кода мантиссы множимого на данную пару разрядов множителя путем переключения кодов кратного множимого с шин 8 - 10 на первый вход соответствующего сумматора 5 в соответствии с табл.1.

На второй вход сумматора 5 поступает накопленное частичное произведение с выхода последующего сумматора 5, задержанное на два такта элементами 6 задержки5 что обеспечивает

5

30

35

45

50

55

0

20

40

автоматический сдвиг влево на два разряда последовательного кода частичного произведения, полученного от более старшей пары разрядов множителя. В результате аналогичных преобразований получается последовательный код произведения мантиссы множимого на младшие 2(и-1) разряда кода множителя. Младший разряд (н)-й пары регистра 1 представляет собой старший разряд мантиссы множителя, а старший разряд - знак множителя. Преобразования относительно старшего разряда мантиссы множителя аналогич- 5 ,ны преобразованию в предыдущих звеньях, а преобразования относительно знака множителя сводятся к вычитанию кода мантиссы множимого в случае отрицательного множителя. Таким образом, преобразование, приведенное к второму входу (н-1) - Го сумматора 5, сводится к табл.2.

В соответствии с табл.2 п-и коммутатор 4 звена должен.подключить код с шины 8 (М) либо код с шины 9 (2М). Сумматор-вычитатель 7 может передать код, снимаемый с коммутатора 4 в неизменном виде, либо вычесть этот код из нулевого кода, т.е. присвоить коду противоположный знак в зависимости от значения знакового разряда множителя. С этой целью сигнал с выхода п-го разряда 3 поступает на управляющий вход режима сумматора-вы- читателя 7. Таким образом, устройство формирует код произведения мантисс сомножителей и осуществляет коррекцию V полученного кода на отрицательный множитель. Коррекция произведения в случае отрицательного множимого может быть осуществлена специальным вьгчитате- лем.

Разряд

Т а б л и ц а 1 Разряд 21 Вход сумматора 5

зГразряд 2J:

Таблица2

О 1 О

О

М

-2М

-М

Так как код сдвинут на два разряда влево

-2М + М - Ц

Формула изобретения

Последовательно-параллельное устройство для умножения чисел в дополнительном коде, содержащее регистр мнолштеля, п коммутаторов (2п - число разрядов задержки), (h-1) последовательных сумматоров и 2п элементов задержки, причем управлякдцие входы i-ro коммутатора (i 1,... ,п ) соединены с выходами 2i-1)-ro и 2i- гр разрядов регистра множителя, первый, второй и третий информационные входы коммутатора (j 1,... ,ь-1) соединены соответственно с шинами множимого, удвоенного множимого и

10

5

0

5

утроенного множимого устройства, первый информационный п-го коммутатора соединен с шиной множимого устройства, первый вход j-rc последовательного сумматора соединен с выходом соответствующего коммутато- . ра, выход k-ro последовательного сумматора (,. . . ,п-1) через последо- - вательно соединенные (2и)-йи (2k-1)-fi элементы задержки подключен к второму входу (k-l)-ro последовательного сумматора, выход первого последовательного сумматора через последовательно cpe y нeнныe второй и первый элементы ; задержки соединен с выходом устройства, выход 2П-ГО элемента задержки соединен с входом (2п-1)-го элемента. задержки выход которого соединен с вторым входом (п-1)-го последовательного сумматора, отличающееся тем, что, с целью упрощения, оно содержит последовательный сумматор-вы- читатель, первый информационный вход которого соединен с щиной значения О устройства, а второй информационный вход - с выходом п-го коммутатора, второй и третий информационные входы которого соединены соответственно с шинами удвоенного множимого и множимого устройства, управляющий вход режима последовательного сумматор а-вычитателя подключен к выходу 2п-го (знакового) разряда регистра множителя.

Редактор О.Юрковецкая

Заказ 5122/46Тираж; 671 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, MocKBaj 1-35 Раушская наб., д,А/5

Производственно-по юграфическое предприятие, г.Ужгород, ул.Проектная,4

Фиг.

Составитель Б.Березкин

Техред И.ПоповИч Корректор Е.Рошко

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для умножения | 1979 |

|

SU868751A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Устройство для умножения | 1985 |

|

SU1252774A1 |

| Устройство для умножения | 1989 |

|

SU1612295A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Устройство для умножения двух @ -разрядных чисел | 1988 |

|

SU1575174A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Конвейерный умножитель | 1988 |

|

SU1575175A1 |

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

Изобретение относится к области вычислительной техники, в частности к арифметическим устройствам, и предназначено для вьтолнения операции умножения двух двоичных чисел, представленных в дополнительном коде , Целью изобретения является упрощение устройства. Устройство содержит регистр множителя, коммутаторы, последовательные сумматоры, элементы задержки, последовательный сумма- тор-вычитатель , шины множимого, удвоенного, множимого, утроенного мно- . жимого, значения О и выход. В устройстве использован метод умножения двоичных чисел в дополнительном коде с двумя корректирзпощими шагами, в соответствии с которыми,определяется произведение мантисс сомножителей, т.е. кодов сомножителей без учета их знаков. Затем осуществляется коррекция произведения мантисс путем вычитания множимого (если множитель отрицателен) либо вычитания множимого, множителя и единицы старшего разряда (если оба сомножителя отрицательны) из 1сода произведения мантисс. 2 ил., 2 табл. с: 9 (Л и ю ел со 1C ел ГС

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приложение к ч.З, Альбом ил- люстрации, л.18, рис.14. | |||

Авторы

Даты

1986-09-23—Публикация

1985-01-15—Подача