Изобретение относится к вычислительной технике.

Целью изобретения является повышение надежности устройства.

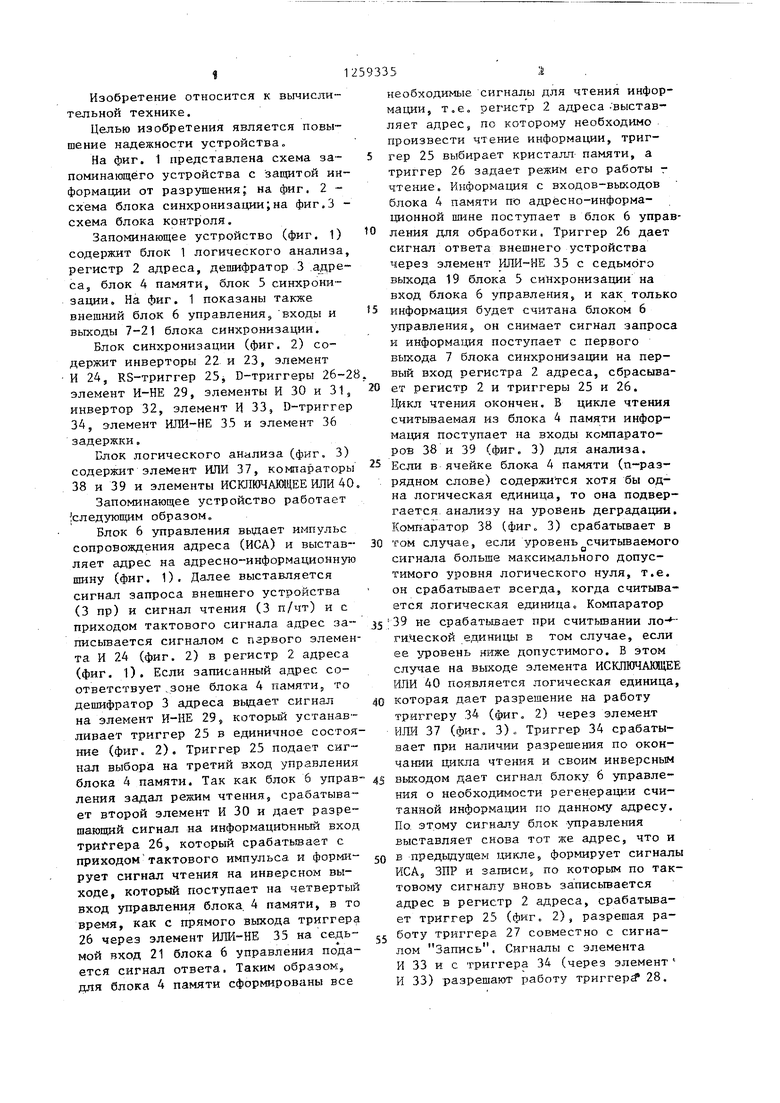

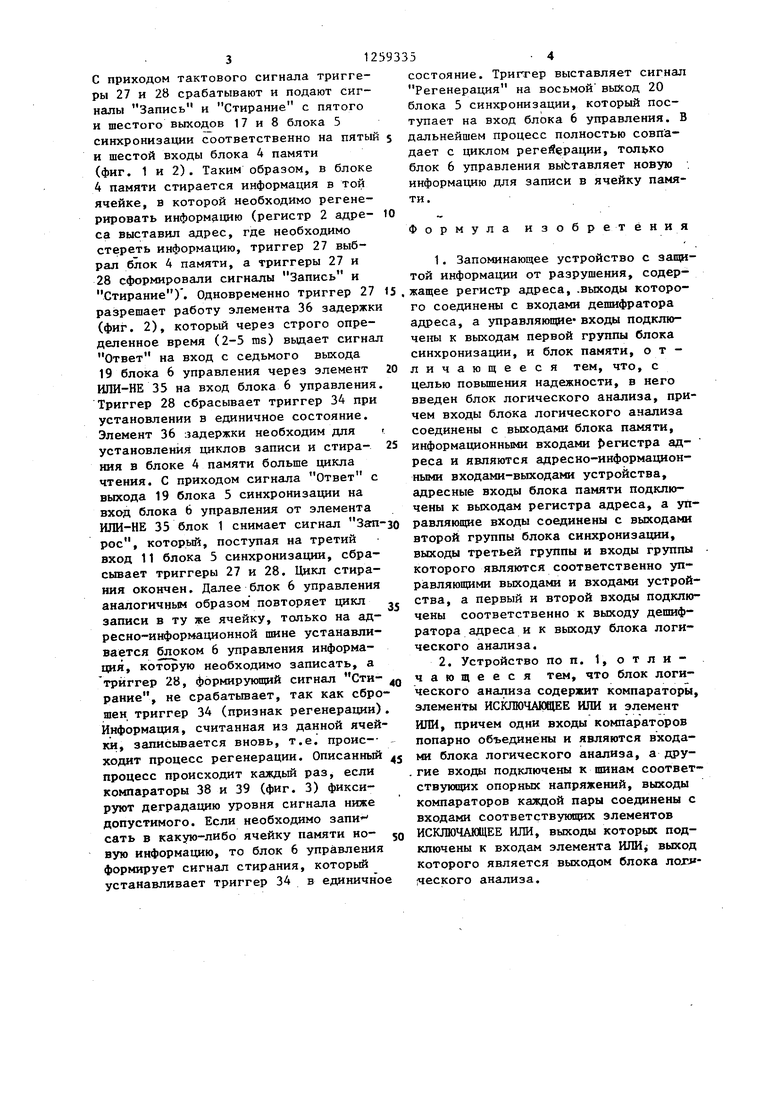

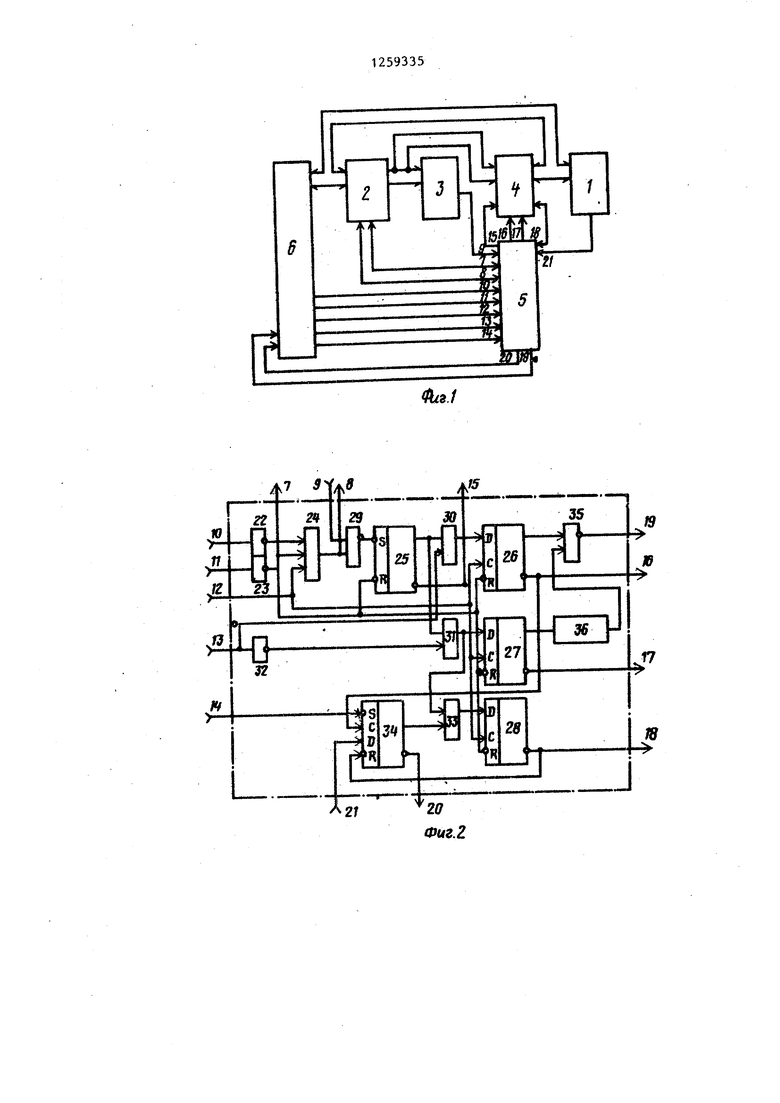

На фиг. 1 представлена схема запоминающего устройства с защитой информации от разрушенияJ на фиг. 2 - схема блока синхронизации;на фиг.З - схема блока контроля.

Запо шнающее устройство (фиг. 1) содержит блок 1 логического анализа, регистр 2 адреса, дешифратор 3 свд блок 4 памяти, блок 5 синхронизации. На фиг. 1 показаны также внешний блок 6 управления, входы и выходы 7-21 блока синхронизации.

Блок синхронизации (фиг. 2) содержит инверторы 22 и 23, элемент И 24, RS-триггер 25j D-триггеры 26-2 элемент И-НЕ 29, элементы И 30 и 31, инвертор 32, элемент И 33, D-триггер 34, элемент ИЛИ-НЕ 35 и элемент 36 задержки,

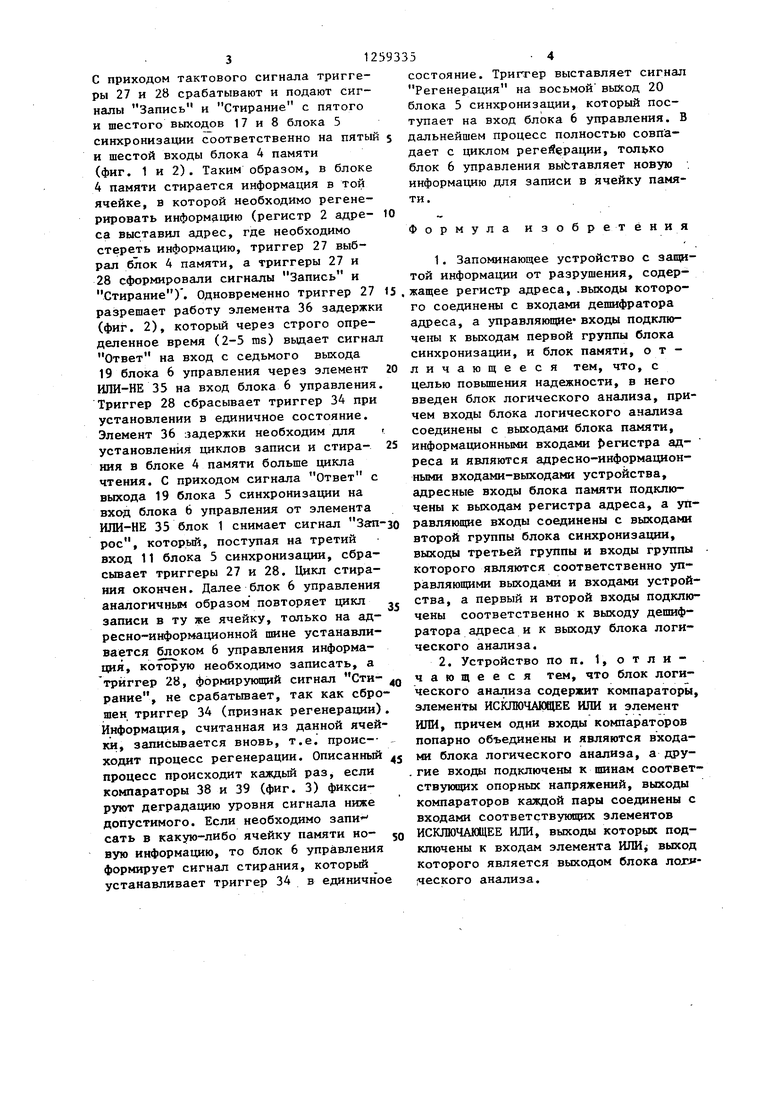

Блок логического анализа (фиг. 3) содержит элемент ИЛИ 37, компараторы 38 и 39 и элементы ИСКПЮЧАМЦЕЕ ИЛИ 40

Запоминающее устройство работает {следующим образом.

Блок 6 управления вьщает импульс сопровождения адреса (ИСА) и выставляет адрес на адресно-информационную шину (фиг. 1). Далее выставляется сигнал запроса внешнего устройства (3 пр) и сигнал чтения (3 п/чт) и с приходом тактового сигнала адрес за- письшается сигналом с парного элемента И 24 (фиг. 2) в регистр 2 адреса (фиг, 1). Если записанный адрес соответствует ,зоне блока 4 памяти, то дешифратор 3 адреса выдает сигнал на элемент И-НЕ 29, которьш устанавливает триггер 25 в единичное состояние (фиг. 2). Триггер 25 подает сигнал выбора на третий вход управления блока 4 памяти. Так как блок 6 управления задал режим чтения, срабатывает второй элемент И 30 и дает разрешающий сигнал на информационнг 1й вход триггера 26, который срабатывает с приходом тактового импульса и форг-ш- рует сигнал чтения на инверсном выходе, который поступает на четвертый вход управления блока. 4 памяти, в то время, как с прямого выхода триггера 26 через элемент ИЛИ-НЕ 35 на седьмой вход 21 блока 6 управления подается сигнал ответа. Таким образом, для блока 4 памяти сформированы все

необходимые сигналы для чтения информации, т.е, регистр 2 адреса- выставляет адрес, по которому необходимо . произвести чтение информации, триггер 25 выбирает кристалл- памяти, а триггер 26 задает режим его работы г чтение. И}Еформация с входов-вькодов блока 4 памяти по адресно-информационной шине поступает в блок 6 управ0 Ленин для обработки. Триггер 26 дает сигнал ответа внешнего устройства через элемент ИЛИ-НЕ 35 с седьмого выхода 19 блока 5 синхронизации на вход блока 6 управления, н как только

5 информация будет считана блоком 6

управления, он снимает сигнал запроса и информация поступает с первого выхода 7 блока синхронизации на пер- вый вход регистра 2 адреса, сбрасыва0 ет регистр 2 и триггеры 25 и 26.

чтения окончен. В цикле чтения считываемая из блока 4 памяти информация поступает на входы компараторов 38 и 39 (фиг. 3) для анализа.

S Если в ячейке блока 4 памяти (п-раз- рядном слове) содержи тся хотя бы одна логическая единица, то она подвергается, анализу на уровень деградации. Компаратор 38 (фиг. 3) срабатывает в

0 том случае, если уровень считьюаемого сигнала больше максимального допустимого уровня логического нуля, т.е. он срабатьшает всегда, когда считывается логическая единица. Компаратор

55 39 не срабатьшает при считьшании ги.иеской единицы в том случае, если ее уровень ниже допустимого. В этом на выходе элемента ИСКЛИНАЩЕЕ ИЛИ 40 появляется логическая единица,

0 которая .дает разрешение на работу триггеру 34 (фиг. 2) через элемент ИЛИ 37 (фиг, 3), Триггер 34 срабатывает при наличии разрешения по окончании цикла чтения и своим инверсным

5 вьрсодом дает сигнал блоку 6 управления о необходимости регенерации считанной информации по данному адресу. По. этому сигналу блок управления выставляет снова тот же адрес, что и

0 в предыдущем цикле, формирует сигналы PICA, ЗПР и записи по которым по тактовому сигнсшу вновь записьгоа€;тся адрес в регистр 2 адреса, срабатьшает триггер 25 (фиг. 2), разрешая ра5 боту триггера 27 совместно с сигналом Запись, Сигналы с элемента И 33 и с триггера 34 (через элемент И 33) разрешают работу триггер 28.

С приходом тактового сигнала триггеры 27 и 28 срабатывают и подают сигналы Запись и Стирание с пятого и шестого выходов 17 и 8 блока 5 синхронизации соответственно на пяты и шестой входы блока 4 памяти (фиг. 1 и 2). Таким образом, в блоке 4 памяти стирается информация в той ячейке, в которой необходимо регенерировать информацию (регистр 2 адре- са выставил адрес, где необходимо стереть информацию, триггер 27 выбрал блок 4 памяти, а триггеры 27 и 28 сформировали сигналы Запись и Стирание). Одновременно триггер 27 разрешает работу элемента 36 задержк (фиг. 2), который через строго определенное время (2-5 ms) выдает сигнал Ответ иа вход с седьмого выхода 19 блока 6 управления через элемент ИЛИ-НЕ 35 на вход блока 6 управления Триггер 28 сбрасывает триггер 34 при установ-пении в единичное состояние. Элемент 36 задержки необходим для установления циклов записи и стира- кия в блоке 4 памяти больше цикла чтения. С приходом сигнала Ответ с выхода 19 блока 5 синхронизации на вход блока 6 управления от элемента ИЛИ-НЕ 35 блок 1 снимает сигнал Зап рос, которьй, поступая на третий вход 11 блока 5 синхронизации, сбрасывает триггеры 27 и 28. Цикл стира- иия окончен. Далее блок 6 управления аналогичным образом повторяет цикл записи в ту же ячейку, только на адресно-информационной шине устанавливается блоком 6 управления информация, которую необходимо записать, а триггер 28, формирующий сигнал Стирание, не срабатывает, так как сброшен триггер 34 (признак регенерации) Информация, считанная из данной ячейки, записывается вновь, т.е. проис- ходит процесс регенерации. Описанный процесс происходит каждьй раз, если компараторы 38 и 39 (фиг. 3) фиксируют деградацию уровня сигнала ниже допустимого. Если необходимо запя сать в какую-либо ячейку памяти но- вую информацию, то блок 6 управления формирует сигнал стирания, который устанавливает триггер 34 в единично

0 5 0 5 о 0

5

0

5

состояние. Триггер выставляет сигнал Регенерация на восьмой выход 20 блока 5 синхронизации, который поступает на вход блока 6 управления. В дальнейшем процесс полностью совпадает с циклом регейерации, только блок 6 управления выЬтавляет новую информацию для записи в ячейку памяти.

Формула изобретения

1.Запоминающее устройство с защитой информации от разрушения, содер, жащее регистр адреса, .выходы которого соединены с входами дешифратора адреса, а управлякщие входы подключены к выходам первой группы блока синхронизации, и блок памяти, отличающееся тем, что, с целью повьш1ения надежности, в него введен блок логического анализа, причем входы блока логического анализа соединены с выходами блока памяти, информационными входами регистра адреса и являются адресно-информационными входами-выходами устройства, адресные входы блока памяти подключены к выходам регистра адреса, а управляющие входы соединены с выходами второй группы блока синхронизации, выходы третьей группы и входы группы которого являются соответственно управляющими выходами и входами устройства, а первый и второй входы подключены соответственно к выходу дешифратора адреса и к выходу блока логического анализа.

2.Устройство по п. 1, отличающееся тем, что блок логического анализа содержит компараторы, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент ИЛИ, причем одни входы компараторов попарно объединены и являются входами блока логического анализа, а дру. гие входы подключены к шинам соответствующих опорных напряжений, выходы компараторов каждой пары соединены с входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых подключены к входам элемента ИЛИ выход которого является выходом блока логя- ;ческого анализа.

.

и.

оп1

38

w

37

UonZ

I

39

IX

«

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными | 1984 |

|

SU1239724A2 |

| УСТРОЙСТВО СБОРА И РЕГИСТРАЦИИ ПОЛЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

SU1825189A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1587518A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| Буферное запоминающее устройство | 1987 |

|

SU1476533A1 |

| Устройство для связи микропроцессора с внешними устройствами | 1986 |

|

SU1372330A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

| Устройство для сопряжения ЭВМ с внешним накопителем | 1988 |

|

SU1672459A1 |

Изобретение относится к вычис- лительной технике и может быть ис- пользовано в постоянных запоми1Щ ощих устройствах на интегральных микросхемах. Целью изобретения является повышение надежности устройства. Устройство содержит блок логического анализа, регистр адреса, дешифратор адреса, блок памяти и блок синхронизации. Блок логического анализа содержит по два компаратора на каждый разряд блока памяти, анализирукицие уровни логического нуля и единицы выходных сигналов, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент ИЛИ, формирукяций сигнал регенерации слова блока памяти при обнаружении деградации логических уровней. В устройстве обеспе-. чивается контроль всех ячеек слова блока памяти при каждом цикле чтения информации. 1 з.п. ф-лы, 3 ил. (Л с ю СП « ее Од СП

Редактор А.Ворович

Составитель О.Исаев

Техред М.Ходанич Корректор И.Муска

Заказ 5128/50Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг.З

| Запоминающее устройство с защитой информации от разрушения | 1976 |

|

SU580587A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Долговременное запоминающее устройствоСО ВСТРОЕННыМ КОНТРОлЕМ | 1979 |

|

SU830588A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-09-23—Публикация

1984-10-08—Подача