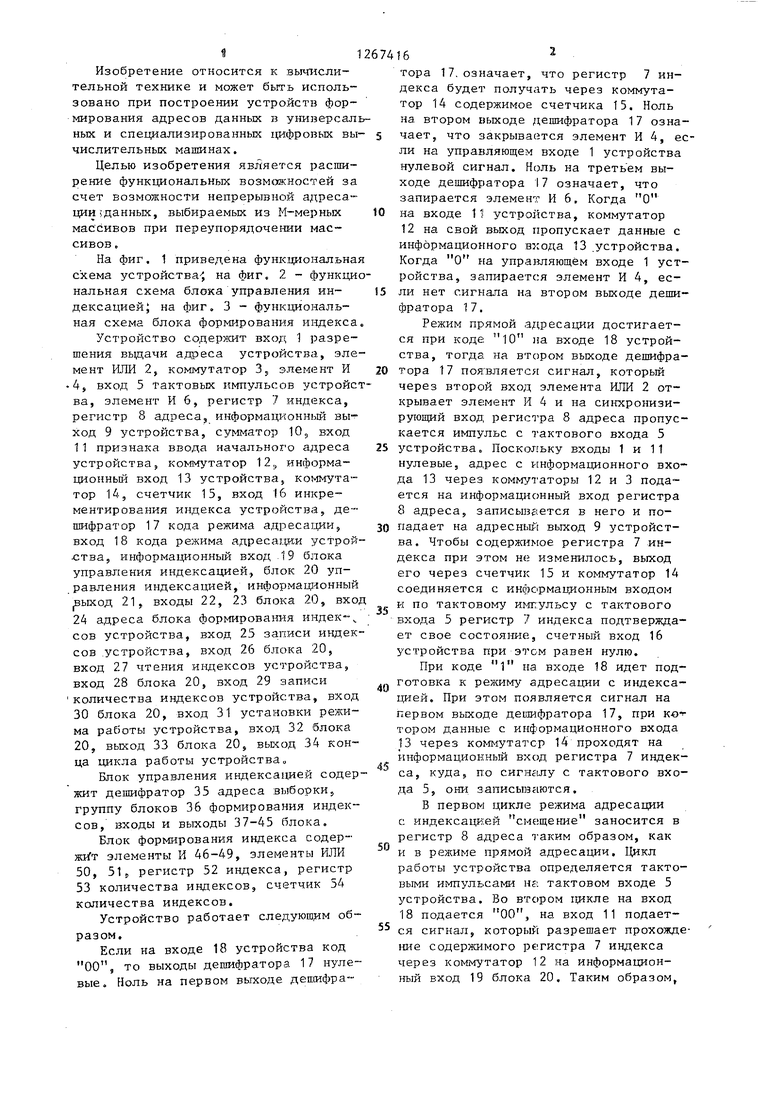

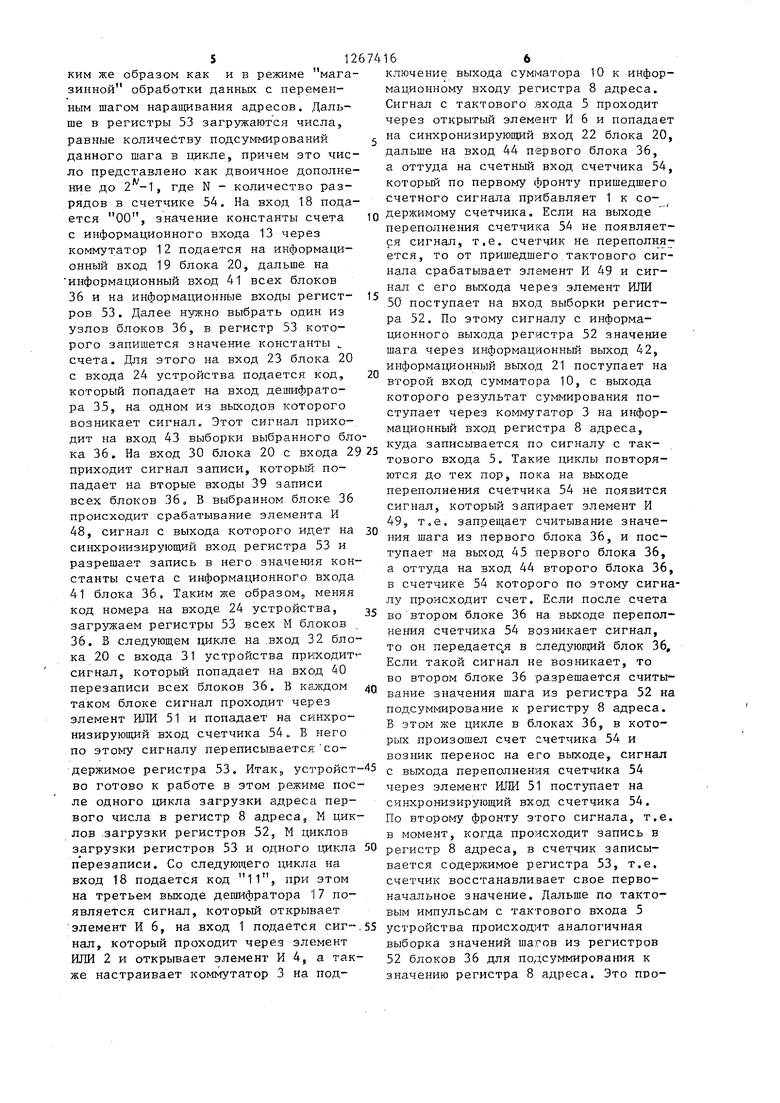

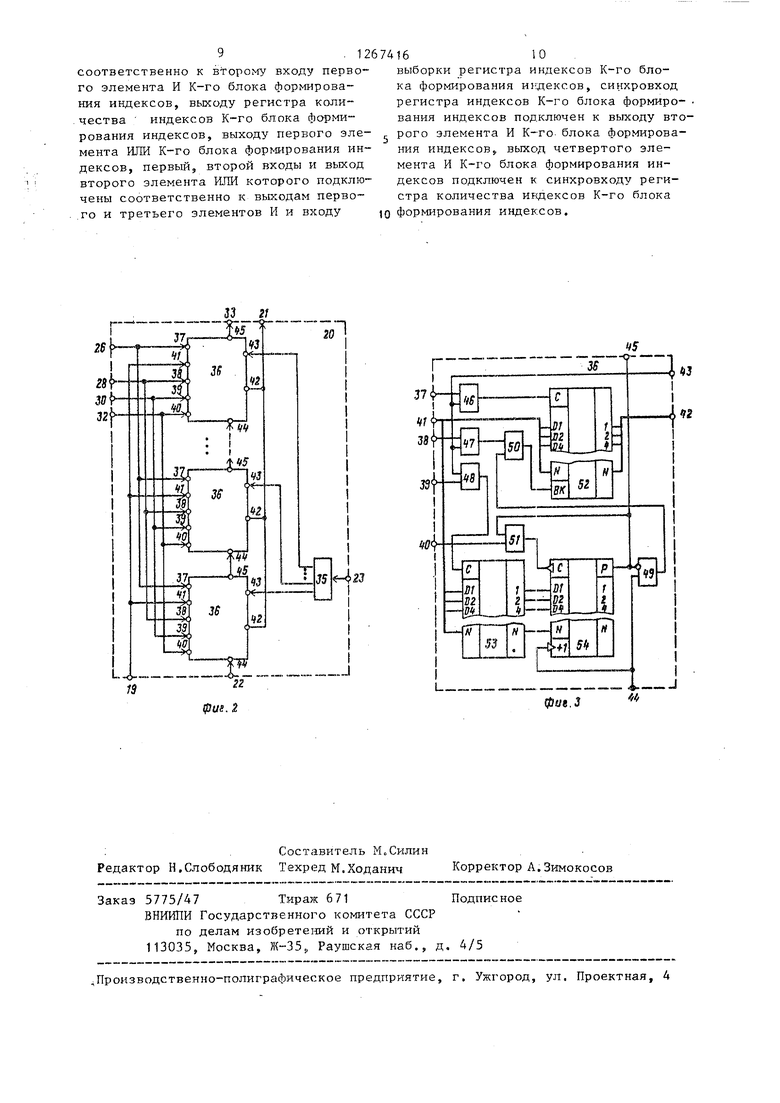

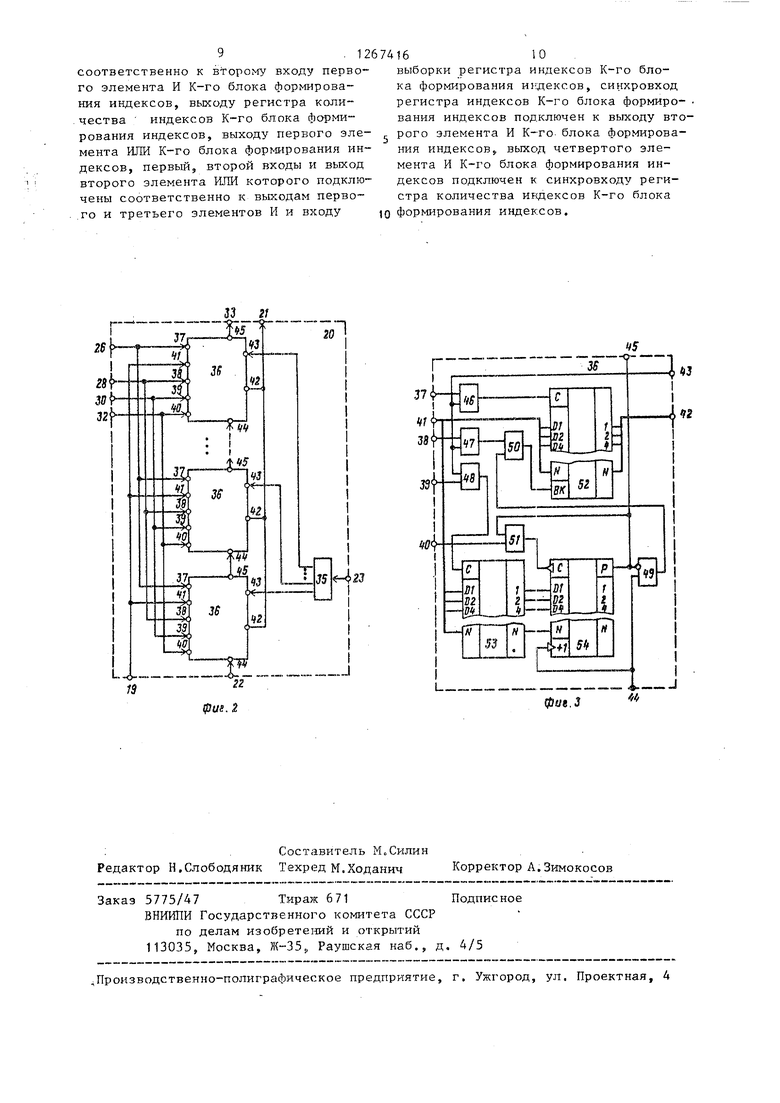

fl Изобретение относится к вычислительной технике и может быть использовано при построении устройств формирования адресов данных в универсал ных и специализированных цифровых вы числительных машинах. Целью изобретения является расширение функциональных возм«жностей за счет возможности непрерывной адресации гданных, выбираемых из М-мерных массивов при переупорядочении массивов . На фиг. 1 приведена функциональна схема устройства-J на фиг. 2 - функци нальная схема ботоха управления индексацией; на фиг. 3 - функциональная схема блока формирования и здекса Устройство содержит вход 1 разрешения выдачи адреса устройства, эле мент ИЛИ 2, коммутатор 3, элемент И 4, вход 5 тактовых импульсов устройс ва, элемент Мб, регистр 7 индекса, регистр 8 адреса, информационный выход 9 устройства, сумматор 10, вход 11 признака ввода начального адреса устройства, коммутатор 12,, информационный вход 13 устройства, Koi myTaтор 14, счетчик 15, вход 16 инкрементирования индекса устройства, дешифратор 17 кода режима адресами, вход 18 кода режима адресахрги устрой ства, информационный вход 19 блока управления индексацией,, блок 20 управления индексацией, информационный ыход 21, входы 22, 23 блока 20, вхо 24 адреса блока формировагош индексов устройства, вход 25 записи индек сов .устройства, вход 26 блока 20, вход 27 чтения индексов устройства, вход 28 блока 20, вход 29 записи количества индексов устройства, вход 30 блока 20, вход 31 установки режима работы устройства, вход 32 блока 20, выход 33 блока 20, вьссод 34 конца цикла работы устройства, Блок управления индексацией содер жит дезпифратор 35 адреса выборки, группу блоков 36 формирования индексов, входы и выходы 37-45 блока. Блок формирования индекса содерж т элементы И 46-49, элементы ИЛИ 50, 5Ь регистр 52 индекса, регистр 53 количества индексов, счетчик 54 количества индексов. Устройство работает след, образом. Если на входе 18 устройства код 00, то выходы дешифратора 17 нуле вые. Ноль на первом выходе денифра162тора 17. означает, что регистр 7 индекса будет получать через коммутатор 14 содержимое счетчика 15. Ноль на втором выходе дешифратора 17 означает, что закрывается элемент И 4, если на управляющем входе 1 устройства нулевой сигнал. Ноль на третьем выходе дешифратора 17 означает, что запирается элемент И 6. Когда О на входе 11 устройства, коммутатор 12на свой выход пропускает данные с информационного входа 13 .устройства. Когда О на упразшяющём входе 1 устройства, запирается элемент И 4, если нет сигнала на втором выходе дешифратора 17. Режим прямой адресации достигается при коде 10 на входе 18 устройства, тогда на втором выходе дешифратора 17 появляется сигнал, который через второй вход элемента ИЛИ 2 открывает элемент И 4 и на синхронизирующий вход регистра 8 адреса пропускается импульс с тактового входа 5 устройства. Поскольку входы 1 и 11 нулевые, адрес с информационного входа 13 через коммутаторы 12 и 3 подается на информационный вход регистра 8 адреса, записывается в него и попадает на адресньш выход 9 устройства. Чтобы содержи ое регистра 7 индекса при этом не изменилось, выход его через счетчик 15 и коммутатор 14 соединяется с информационным входом и по тактовому иГ1г;:ульсу с тактового входа 5 регистр 7 индекса подтверждает свое состояние, счетный вход 16 устройства при этом равен нулю. При коде 1 па входе 18 идет подготовка к реяшму адресации с индексацией. При этом появляется сигнал на первом выходе дешифратора 17, при котором данные с информационного входа 13через коммутатор 14 проходят на информационный вход регистра 7 индекса, куда, по сигнешу с тактового входа 5, они записываются. В первом цикле режима адресации с индексацией смещение заносится в регистр 8 адреса таким образом, как и в режиме прямой адресации. Цикл работы устройства определяется тактовыми импульсами на тактовом входе 5 устройства. Во втором 1щкле на вход 18 подается 00, на вход 11 подается сигнал, который разрешает прохождение содержимого регистра 7 индекса через коммутатор 12 на информационный вход 19 блока 20. Таким образом, 3 значение регистра 7 индекса попадает на информационные входы 41 всех блоков 36. Далее нужно выбрать один из них, в регистр 52 индекса которого запишется значение регистра 7 индекса. Для этого на вход 23 блока 20 с входа 24 устройства подается код номера блока, который попадает на вход дешифратора 35, на одном из выходов которого возникает сигнал. Этот сигнал приходит на вход 43 выборки выбранного блока 36 группы. На вход 26 блока 20 с входа 25 устройства прихо дит сигнал записи, который попадает на входы 37 записи всех блоков 36 группы. В выбранном блоке 36 группы происходит срабатывание элемента И 4 и на синхронизирующий вход регистра 52 подается сигнал записи, по которо му регистр 52 записывает значение ре гистра 7 индекса. В третьем цикле этого режима на вход 18 подается код 00. На вход 28 блока 20 с входа 27 устройства подается сигнал считывания, который попадает на вход 38 всех блоков 36 группы. На вход 23 блока 20 с входа 24 устройства подается код номера блока 36 группы, который попадает на вход дешифратора 33, на одном из выходов которого возника ет сигнал. Этот сигнал приходит на вход 43 выборки выбранного блока 36. В выбранном блоке 36 происходит срабатывание элемента И 47, с выхода ко торого через первый вход элемента ИЛ 50 и его выход, сигнал попадает на вход выборки регистра 52. Этот регистр считывает индекс на информационный вьпсод 42 блока 36. Оттуда зн чение индекса проходит на информационный выход 21 блока 20, дальше на второй вход сумматора 10. На вход 1 устройства подается сигнал, который проходит через первый вход элемента ИЛИ 2 через его выход на первый вход элемента И 4 и открывает его. Сигнал с входа 1 настраивает коммутатор 3 на передачу результата суммирования смещения и индекса с выхода сумматора 10 на информационный вход регистра 8 адреса, куда результат записьюается по тактовому сигналу с тактового входа 5. В этом же цикле информация с выхода регистра 7 индек са через счетчик 15 и коммутатор. 14 подается на информационный выход регистра 7 индекса и записьшается в него. Режим адресации с продвижением индекса отличается от предыдущего 164 тем, что в третьем цикле на вход 16 устройства подается сигнал, по которому индекс наращивается на 1. Режим магазинной обработки массива данных с постоянным шагом наращивания адресов начинается с .загрузки адреса первого числа в регистр 8 адреса по режиму прямой адресации. В следующем цикле значение шага наращивания адресов с информационного входа 13 устройства подается на первый вход коммутатора 12. Все остальные действия в этом цикле аналогичны второму циклу режима адресации с индексацией, с той лишь разницей, что на вход 11 не подается сигнал, в результате чего коммутатор 12 на свой выход будет пропускать не значение регистра 7 индекса, а значение шага с информационного входа 13 устройства. Все последующие циклы в этом режиме аналогичны третьему циклу режима адресации с индексацией без продвижения индекса. Режим магазинной обработки массива данных с переменным шагом нара-, ш вания адресов начинается с загрузки адреса первого числа в регистр 8 адреса по режиму прямой адресации. Дальше значения шагов, используемые в алгоритме адресации, загружаются в регистры 52 блоков 36. В один блок 36 загружается значение одного шага, причем количество М значений шагов должно быть меньше либо равно количеству блоков 36. Каждый цикл этой загрузки аналогичен второму циклу режима магазинной обработки массива данных с постоянным шагом, и от личаются между собой эти циклы кодом на входе 24 устройства. Все последующие циклы аналогичны третьему циклу режима адресации с индексацией без продвижения индекса, причем, после окончания формирования адресов массива данных с одним шагом для то го, чтобы со следующего цикла формировать адреса с другим шагом, на вход 24 подается код адреса блока 36, в котором хранится значение следующего шага. В режиме адресации для выборки элементов из М-мерных массивов данных устройство позволяет отсчитьгоать количество шагов адресации и переключать константы шага. Адрес первого числа -заносится в регистр 8 адреса по режиму прямой адресации. Регистры 52 всех М блоков 36 загружаются та-.

512

КИМ же образом как и в ре;«име магазинной обработки данных с переменным шагом наращивания адресов. Дальше в регистры 53 загружаются числа, равные количеству подсуммирований данного шага в цикле, причем это число представлено как двоичное дополнение до , где N - количество разрядов в счетчике 54. На вход 18 подается 00, значение константы счета с информационного входа 13 через коммутатор 12 подается на информационный вход 19 блока 20, дальше на информационный вход 41 всех блоков 36 и на информационные входы регистров 53. Далее нужно выбрать один из узлов блоков 36, в регистр 53 которого запишется значение константы счета. Для этого на вход 23 блока 20 с входа 24 устройства подается код, который попадает на вход депифратора 35, на одном из выходов которого возникает сигнал. Этот сигнал прихо-, дит на вход 43 выборки выбранного блока 36. На вход 30 блока 20 с входа 29 приходит сигнал записи, которьй: попадает на вторые входы 39 записи всех блоков 36, В выбранном блоке 36 происходит срабатывание элемента И 48, сигнал с выхода которого идет на синхронизирующий вход регистра 53 и разрешает запись в него . значени:я константы счета с информационного входа 41 блока 36, Таким же образом, меняя код номера на входе 24 устройства, загружаем регистры 53 всех М блоков 36. В следующем цикле на .вход 32 блока 20 с входа 31 устройства пррэсодит сигнал, который попадает на вход 40 перезаписи всех блоков 36. В каждом таком блоке сигнал проходит через элемент ИЛИ 51 и попадает на синхронизирующий вход счетчика 54„ В него по этому сигналу переписываетсясодержимое регистра 53. Итак, устройство готово к работе в этом режиме после одного цикла загрузки адреса первого числа в регистр 8 адреса, М циклов .загрузки регистров 52, М щжлов загрузки регистров 53 и одного цикла перезаписи. Со следующего цикла на вход 18 подается код 11, при этом на третьем выходе дешифратора 17 появляется сигнал, который открывает элемент И 6, на вход 1 подается сигнал, который проходит через элемент ИЛИ 2 и открывает элемент И 4, а также настраивает коммутатор 3 на под166

ключение выхода сумматора 10 к информационному входу регистра 8 адреса. Сигнал с тактового входа 5 проходит через открытый элемент И 6 и попадает на синхронизирующий вход 22 блока 20, дальше на вход 44 первого блока 36, а оттуда на счетный вход счетчика 54, который по первому фронту пришедшего счетного сигнала прибавляет 1 к содержимому счетчика. Если на выходе переполнения счетчика 54 не появляется сигнал, т.е. счетчик не переполняется, то от пришедшего.тактового сигнала срабатывает элемент И 49 и сигнал с его выхода через элемент ИЛИ 50 поступает на вход выборки регистра 52. По этому сигналу с информаицонного выхода регистра 52 значение шага через информационный выход 42, информапдонный выход 21 поступает на второй вход сумматора 10, с выхода которого результат суммирования поступает через коммутатор 3 на информационный вход регистра 8 адреса, куда записывается по сигналу с тактового входа 5, Такие циклы повторяются до тех пор, пока на выходе переполнения счетчика 54 не появится сигнал, который запирает элемент И 49, т.е. запрещает считывание значения шага из первого блока 36, и поступает на выход 45 первого блока 36, а оттуда на вход 44 второго блока 36, в счетчике 54 которого по этому сигналу происходит счет. Если после счета вовтором блоке 36 на выходе переполнения счетчика 54 возникает сигнал, то он передается в следующий блок 36, Если такой сигнал не возникает, то во втором блоке 36 разрешается считывание значения шага из регистра 52 на подсуммирование к регистру 8 адреса. В этом же цикле в блоках 36, в которых произошел счет счетчика 54 и возник перенос на его выходе, сигнал с выхода переполнения счетчика 54 через элемент ИЛИ 51 поступает на синхронизирующий вход счетчика 54. По второму фронту этого сигнала, т.е. в момент, когда происходит запись в регистр 8 адреса, в счетчик записывается содерлшмое регистра 53, т.е. счетчик восстанавли.вает свое первоначальное значение. Дальше по тактовым импульсам с тактового входа 5 устройства происходит аналогичная выборка значений шагов из регистров 52 блоков 36 для подсуммирования к значению регистра 8 адреса. Это про71должается до тех пор, пока в последнем М-м блоке 36 на выходе переполне ния счетчика 54 не появится сигнал, который через выход 45 М-го блока 36, выход 33 блока 20 попадает на выход 34 устройства. По этому сигналу на вход 18 подается код 00. Адресация по этому режиму закончена. Формула изобретения Устройство адресации, содержащее элемент ИЛИ, два элемента И, регистр адреса, сумматор, три коммутатора, регистр индекса, счетчик и дешифратор кода режима адресации, причем вход разрешения вьщачи адреса устройства подключен к первому входу элеме 1 И и к управляющему входу первого коммутатора, выход которого подключен к информационному входу регистра адреса, выход которого подключен к информационному выходу устройства и к первому входу сумматора, выход которого подключен к первому информационному входу первого коммутатора, второй информационный вход которого подключен к выходу второго коммутатора, управляющий вход которого подключен к входу признака ввода началь ного адреса устройства, информационный вход устройства подключен к первым информационным входам второго и третьего коммутаторов, вход инкрементирования индекса устройства подключен к счетному входу счетчика, вы ход которого подключен к второму информационному входу третьего коммута тора, выход которого подключен к информационному входу регистра индекса выход которого подключен к второму информационному входу второго коммутатора и к информационному входу счетчика, вход тактовых импульсов . устройства подключен к первьм входам первого и второго элементов И и к синхровходу регистра индекса, вход кода режима адресации устройства под ключен к входу дешифратора кода режима адресации, первьй, второй и тре тий выходы которого подключены соответственно к управляющему входу третьего коммутатора, второму входу эле мента ИЛИ и к второму входу первого элемента И, выход элемента ИЛИ подключен к второму входу второго эле мента И, выход которогоподключен к синхровходу регистра адреса, отли чающееся тем, что, с целью 168 расширения функциональных возможностей за счет возможности непрерывной адресации данных, выбираемых из Ммерных массивов при переупорядочении массивов, в него введен блок управления индексацией, причем блок управления индексацией содержит группу . блоков формирования индекса и дешифратор адреса выборки, каждый блок формирования индекса группы содержит четьфе элемента И, два элемента ИЛИ, регистр индекса, регистр количества индексов и счетчик количества индексов, причем выход второго коммутатора подключен к информационным входам регистра индекса и регистра количества индексов блоков формирования индексов группы, выходы регистров индекса блоков формирования индексов грутт пы подключены к второму входу сумматора, выход первого элемента И подключен к счетному входу счетчика количества индексов и к первому входу первого элемента И первого блока формирования индексов группы, вход адреса блока формирования индексов устройства подключен к входу дешифратора адреса выборки, К-й выхоДКоторо- го подключен к первым входам второго, третьего и четвертого элементов И К-го блока формирования индексов группы, (К 1,М, где М - размерность массива), вторые входы которых подключены соответственно к входу записи индексов устройства, входу чтения индексов устройства и к входу записи количества индексов устройства, вход установки режима работы устройства подключен к первому входу первого элемента ИЛИ К-го блока формирования индексов, второй вход первого элемента ИЛИ Р-го блока формирования индексов подключен к выходу переполнения счетчика количества индексов Р-го блока формирования индексов группы и соединен с счетным входом счетчика количества индексов и с первым входом первого элемента И (Р+1)го блока формирования индексов группы (Р 2, М - 1), выход счетчика количества индексов М-го блока формирования индексов группы подключен к второму входу первого элемента ИЛИ М-го блока формирования индексов и к выходу признака конца цикла работы устройства, выход переполнения,, информационный вход и синхровход счетчика количества индексов К-го блока формирования индексов группы подключены 9, 12 соответственно к второму входу первого элемента И К-го блока формирования индексов, выходу регистра коли. честна индексов блока формирования индексов, выходу первого элемента ИЛИ К-го блока формирования индексов, первый, второй входы и выход второго элемента ИЛИ которого подключены соответственно к вькодам перво.го и третьего элементов И и входу 1610 выборки регистра индексов К-го блока формирования индексов, синхровход регистра индексов К-го блока формирования индексов подключен к выходу второго элемента И К-то- блока формирования индексов, выход четвертого элемента И К-го блока формирования индексов подключен к синхровходу регистра количества икдэексов К-го блока формирования индексов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство адресации | 1987 |

|

SU1418712A1 |

| Устройство для формирования адреса | 1985 |

|

SU1297045A1 |

| Устройство для формирования адреса данных | 1982 |

|

SU1068939A1 |

| Устройство для формирования адресов команд и данных | 1985 |

|

SU1312573A1 |

| Устройство для параллельного формирования адресов | 1987 |

|

SU1418711A1 |

| Устройство для формирования исполнительных адресов | 1985 |

|

SU1298745A2 |

| Устройство для формирования исполнительных адресов | 1989 |

|

SU1837285A1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

Изобретение относится к вьтислительной технике и может быть использовано при построении устройств формирования адресов данных в универсальных и специализированных цифровых вычислительных машинах. Целью изобретения является расширение функциональных возможностей за счет возможности непрерывной адресации данных, выбираемых из М-мерных массивов при переупорядочении массивов.Устройство содержит элемент ИЛИ 2, три коммутатора 3, 12, 14,два элемента И 4, 6 регистр 7 индекса, регистр 8 адреса, сумматор 10, счетчик 15, дешифратор 17, блок 20 управления индексацией, входы и выходы устройства. 3 ил.

23

13

««

фак.З

| Устройство для формирования адреса | 1979 |

|

SU826350A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования адреса данных | 1982 |

|

SU1068939A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-30—Публикация

1985-01-03—Подача