Ю

Изобретение относится к вычИсли- тельн ой технике и может быть использовано при построении устройств формирования адресов данных в универсаль ных и специализированных цифровых вычислительных машинах.

Целью изобретения является расширение функциональных возможностей устройства путем осуществления режима адресации многомерных массивов данных.

Расширение функциональных возможностей происходит за счет блока циклов, который в режиме адресации многомерных массивов данных производит переключение значений шагов адресации, отсчет подсуммированний казкдого шага адресации, вьщает сигнал окончания адресации по данному режиму. Использование М узлов управления циклом20 синхронизирующий вход регистра расширяет возможности адресадаи, так 1 адреса, в который записывается /как при такой организации можно использовать несколько индексных регистров. Кроме того, при отсчете количества адресуемых данных внутри

элемент И-НЕ 40 и два элемента ИЛИ и 42.

Узел 22 имеет информационный в 43, вход 44 записи индекса, вход считывания, вход 46 записи шага, вход 47 переноса, счетный вход 48 вход 49 выборки, информационный в ход 50, вход 51 перезаписи, выход 52 переноса.

Работу устройства адресации ра сматривают в различных режимах.

Режим прямой адресации. На вхо 9 подается сигнал, который настраи вает мульти глексор 2 на передачу J5 данных с входа 11 на информационны вход регистра 1 адреса, этот же си нал проходит через элемент ИЛИ 6 и открывает элемент И 4, сигнал с входа 8 проходит через элемент И

адрес, но после этого попадает на выход 1О.

Режим ад1)есации с индексацией 25 без продвижения индекса. В первом

блока циклов экономится память команд и упрощаются программы вычислений.

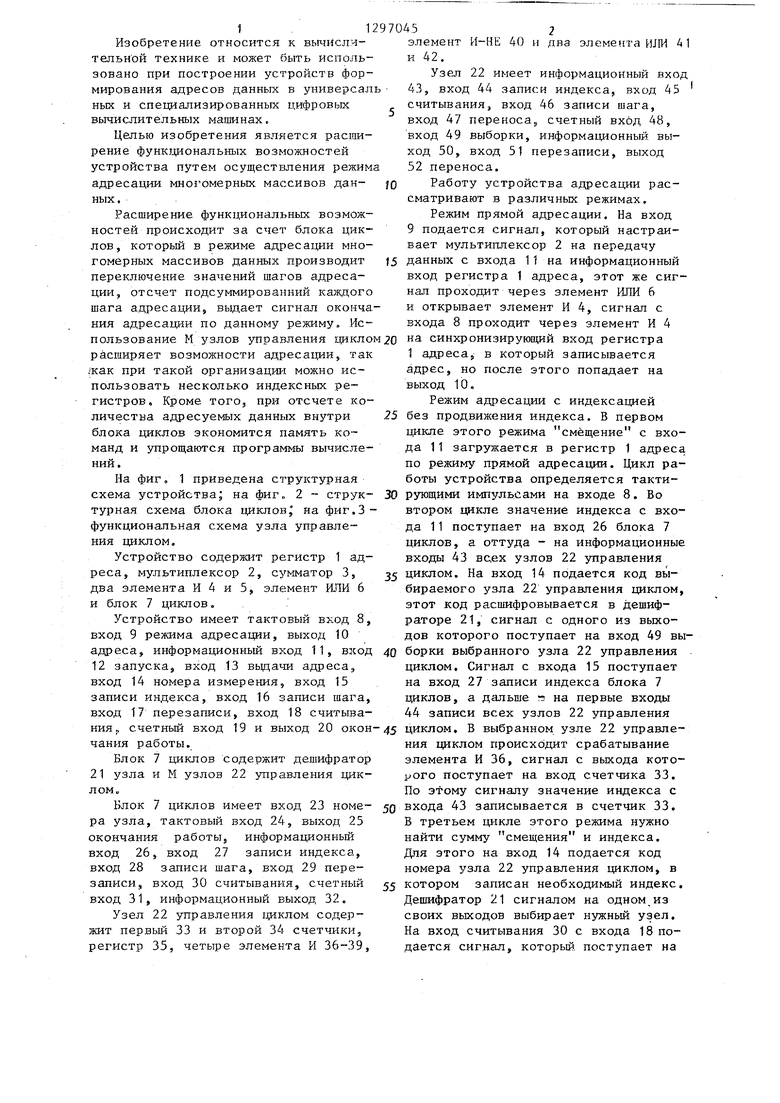

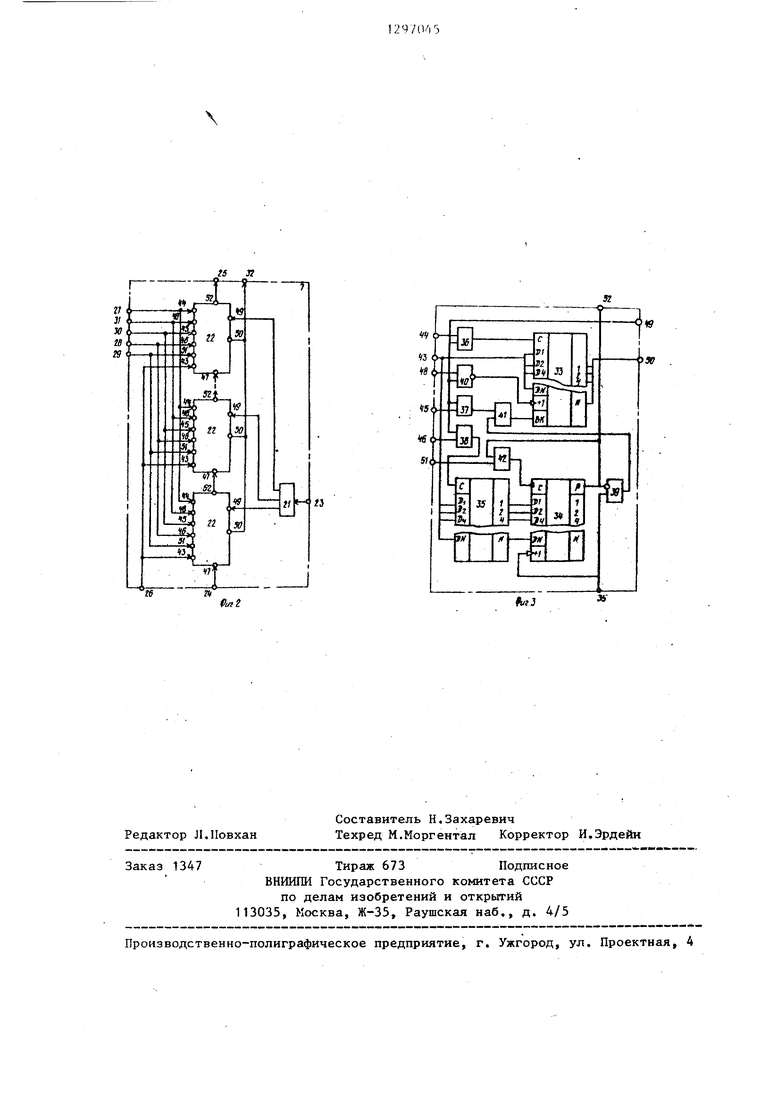

На фиг, 1 приведена структурная

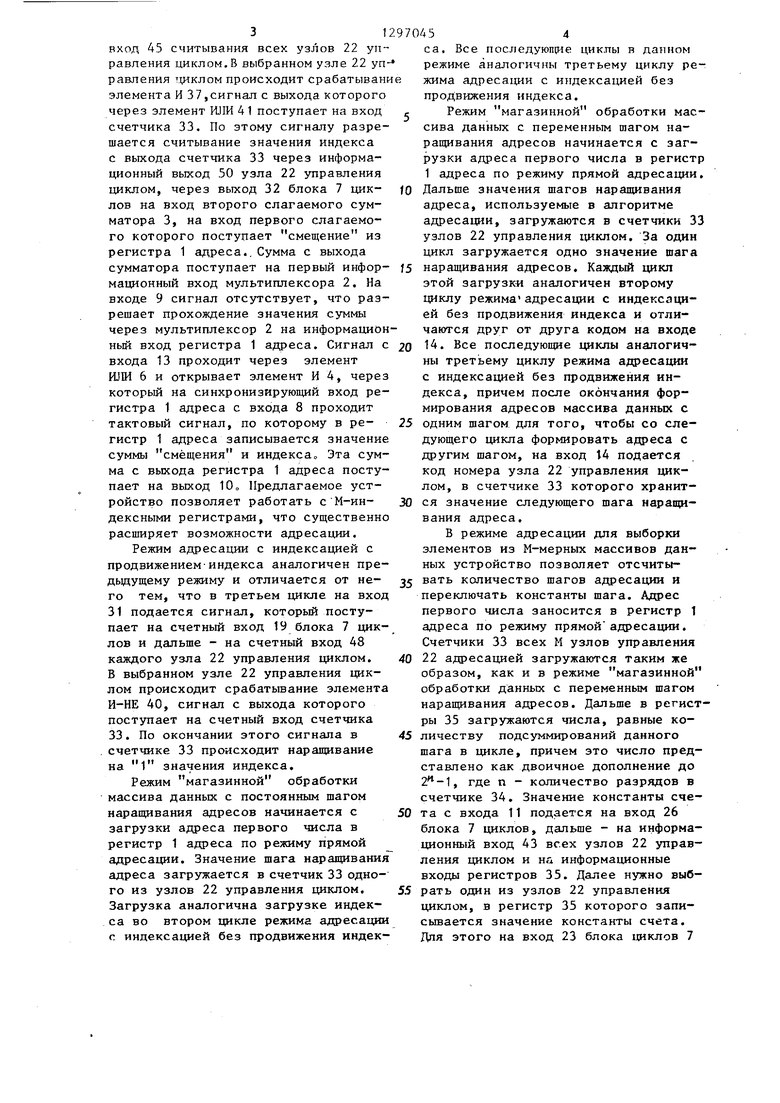

схема устройства; на фиг,, 2 струк- 30 рующими импульсами на входе 8. Во

турная схема блока циклов «а фиг.З- функционапьная схема узла управления циклом.

Устройство содержит регистр 1 адреса, мультиплексор 2, сумматор 3, два элемента И 4 и 5, элемент ИЛИ 6 и блок 7 циклов,

Устройство имеет тактовый вход 8, вход 9 режима адресации, выход 10

адреса, информационный вход 11, вход 40 борки выбранного узла 22 управления 12 запуска, вход 13 въщачи адреса, циклом. Сигнал с входа 15 поступает вход 14 номера измерения, вход 15 на вход 27 записи индекса блока 7

циклов, а - на первые входы 44 записи всех узлов 22 управления

записи индекса, вход 16 записи шага, вход 17 перезаписи, вход 18 считывания,, счетный вход 19 и выход 20 окон- 5 циклом, В выбранном узле 22 управле- чания работы.ния циклом происхЬдит срабатывание

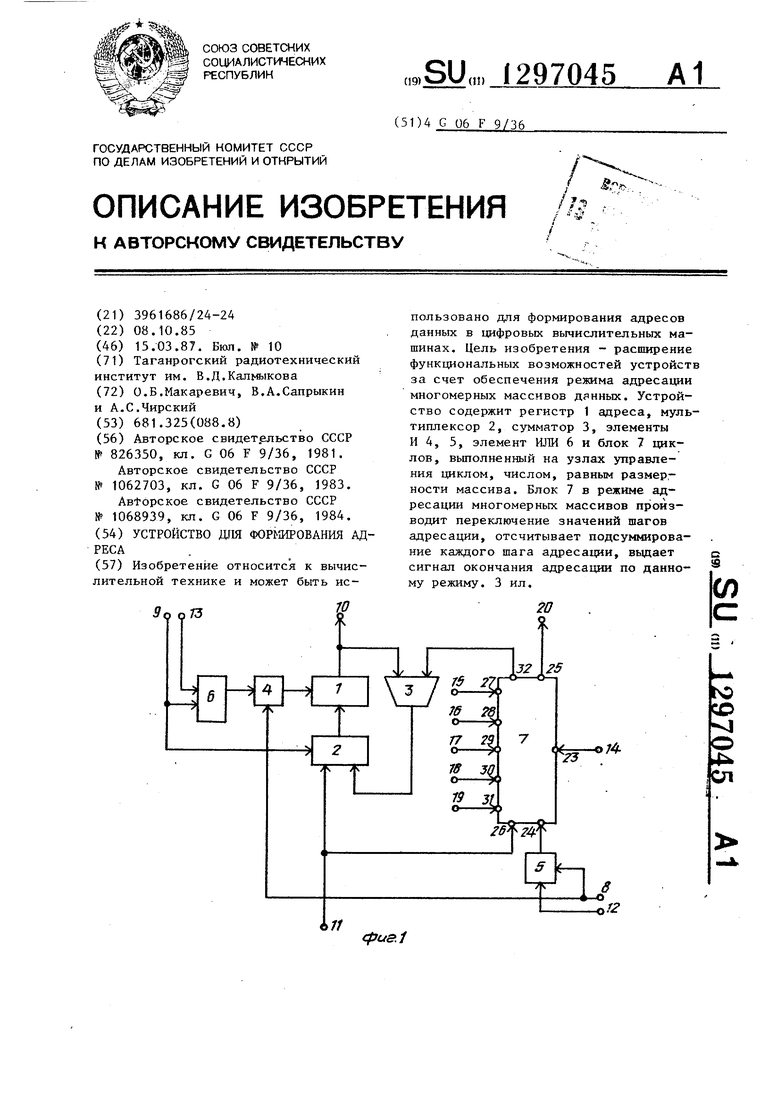

Блок 7 циклов содержит дешифратор

элемента И 36, сигнал с выхода которого поступает на вход счетчика 33, По этому сигналу значение индекса с

21 узла и М узлов 22 управления циклом.

Блок 7 циклов имеет вход 23 номе- Q зхоца 43 записывается в счетчик 33,

ра узла, тактовый вход 24, выход 25 окончания работы, информационный вход 26, вход 27 записи индекса, вход 28 записи шага, вход 29 перезаписи, вход 30 считывания, счетный вход 3 1, информационный выход, 32.

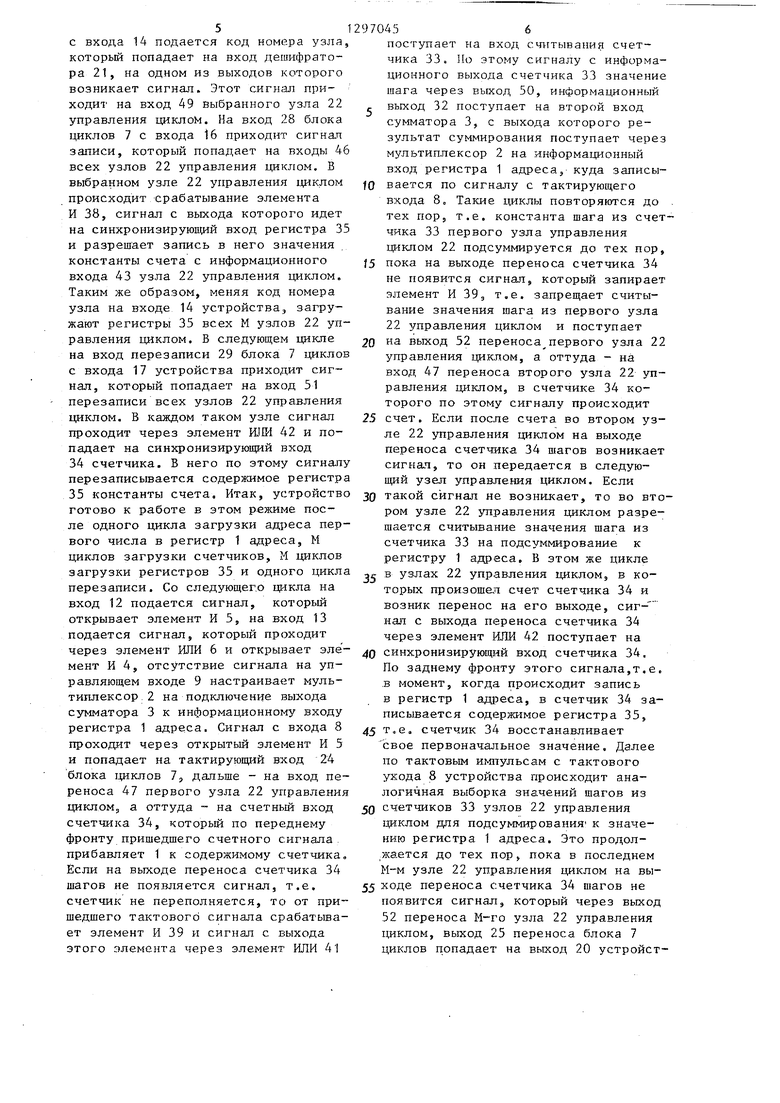

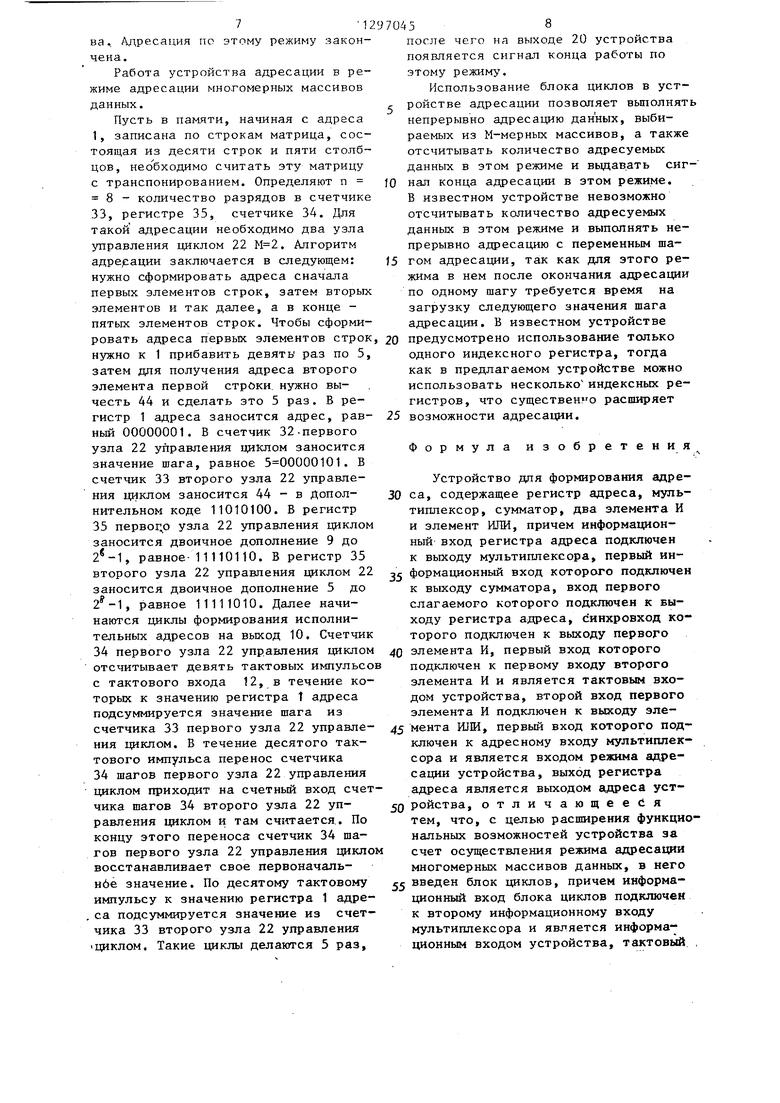

Узел 22 управления исиклом содержит первый 33 и второй 34 счетчики, регистр 35, четыре элемента И 36-39,

В третьем цикле этого режима нужно найти сумму смещения и индекса. Для этого на вход 14 подается код номера узла 22 управления циклом, в 55 котором записан необходимый индекс Дешифратор 21 сигналом на одном,из своих выходов выбирает нужный узел. На вход считывания 30 с входа 18 по дается сиг.НеШ, который, поступает на

0 синхронизирующий вход регистра 1 адреса, в который записывается

элемент И-НЕ 40 и два элемента ИЛИ 41 и 42.

Узел 22 имеет информационный вход 43, вход 44 записи индекса, вход 45 считывания, вход 46 записи шага, вход 47 переноса, счетный вход 48, вход 49 выборки, информационный выход 50, вход 51 перезаписи, выход 52 переноса.

Работу устройства адресации рассматривают в различных режимах.

Режим прямой адресации. На вход 9 подается сигнал, который настраивает мульти глексор 2 на передачу 5 данных с входа 11 на информационный вход регистра 1 адреса, этот же сигнал проходит через элемент ИЛИ 6 и открывает элемент И 4, сигнал с входа 8 проходит через элемент И 4

синхронизирующий вход регистра 1 адреса, в который записывается

адрес, но после этого попадает на выход 1О.

Режим ад1)есации с индексацией без продвижения индекса. В первом

цикле этого режима смещение с входа 11 загружается в регистр 1 адреса по режиму прямой адресации. Цикл работы устройства определяется тактивтором 1Щкле значение индекса с входа 11 поступает на вход 26 блока 7 циклов, а оттуда - на информационные входы 43 всех узлов 22 управления 35 циклом. На вход 14 подается код выбираемого узла 22 управления циклом, этот код расшифровывается в дешифраторе 21, сигнал с одного из выходов которого поступает на вход 49 выэлемента И 36, сигнал с выхода которого поступает на вход счетчика 33, По этому сигналу значение индекса с

В третьем цикле этого режима нужно найти сумму смещения и индекса. Для этого на вход 14 подается код номера узла 22 управления циклом, в 55 котором записан необходимый индекс. Дешифратор 21 сигналом на одном,из своих выходов выбирает нужный узел. На вход считывания 30 с входа 18 подается сиг.НеШ, который, поступает на

вход 45 считывания всех узлов 22 управления циклом, В выбранном узле 22 уп равления тщклом происходит срабатыван элемента И 37,сигнал с выхода которого через элемент ИЛИ 41 поступает на вход счетчика 33. По этому сигналу разрешается считывание значения индекса с выхода счетчика 33 через информационный выход 50 узла 22 управления циклом, через выход 32 блока 7 цик- лов на вход второго слагаемого сумматора 3, на вход первого слагаемого которого поступает смещение из регистра 1 адреса.. Сумма с выхода сумматора поступает на первый инфор- мационный вход мультиплексора 2. На входе 9 сигнал отсутствует, что разрешает прохождение значения суммы через мультиплексор 2 на информацион ньй вход регистра 1 адреса. Сигнал с входа 13 проходит через элемент ИЛИ 6 и открывает элемент И 4, через который на синхронизирующий вход регистра 1 адреса с входа 8 проходит тактовый сигнал, по которому в ре- гистр 1 адреса записывается значение суммы смещения и индекса. Эта сумма с выхода регистра 1 адреса поступает на выход 10о Предлагаемое устройство позволяет работать с М-ин- дексными регистрами, что существенно расширяет возможности адресации.

Режим адресации с индексацией с продвижением-индекса аналогичен пре- дьщущему режиму и отличается от не- го тем, что в третьем цикле на вход 31 подается сигнал, который поступает на счетный вход 19 блока 7 циклов и дальше - на счетный вход 48 каждого узла 22 управления циклом. В выбранном узле 22 управления циклом происходит срабатывание элемента И-НЕ 40, сигнал с выхода которого поступает на счетный вход счетчика 33. По окончании этого сигнала в счетчике 33 происходит наращивание на 1 значения индекса.

Режим магазинной обработки массива данных с постоянным шагом наращивания адресов начинается с загрузки адреса первого числа в регистр 1 адреса по режиму прямой адресации. Значение шага наращивания адреса загружается в счетчик 33 одного из узлов 22 управления циклом. Загрузка аналогична загрузке индекса во втором цикле режима адресации с индексацией без продвижения индекса. Все последуюп(ие циклы н данном режиме аналогичны третьему циклу режима адресации с индексацией без продвижения индекса.

Режим магазинной обработки массива данных с переменным шагом наращивания адресов начинается с загрузки адреса первого числа в регист 1 адреса по режиму прямой адресации Дальше значения шагов наращивания адреса, используемые в алгоритме адресации, загружаются в счетчики 3 узлов 22 управления циклом. За один цикл загружается одно значение шага наращивания адресов. Каждый цикл этой загрузки аналогичен второму циклу режима адресации с индексацией без продвижения индекса и отличаются друг от друга кодом на входе 14. Все последующие циклы аналогичны третьему циклу режима адресации с индексацией без продвижения индекса, причем после окончания формирования адресов массива данных с одним шагом для того, чтобы со следующего цикла формировать адреса с другим шагом, на вход t4 подается код номера узла 22 управления циклом, в счетчике 33 которого хранится значение следующего шага наращивания адреса.

В режиме адресации для выборки элементов из М-мерных массивов данных устройство позволяет отсчитывать количество шагов адресации и переключать константы шага. Адрес первого числа заносится в регистр 1 адреса по режиму прямой адресации. Счетчики 33 всех М узлов управления 22 адресацией загружаются таким же образом, как и в режиме магазинной обработки данных с переменным шагом наращивания адресов. Дальше в регистры 35 загружаются числа, равные количеству подсумм}фований данного шага в цикле, причем это число представлено как двоичное дополнение до , где п - количество разрядов в счетчике 34. Значение константы счета с входа 11 подается на вход 26 блока 7 циклов, дальше - на информационный вход 43 всех узлов 22 управления циклом и на информационные входы регистров 35. Далее нужно выбрать один из узлов 22 управления циклом, в регистр 35 которого записывается значение константы счета. Для этого на вход 23 блока циклов 7

5

с входа 14 подается код номера узла, который попадает на вход дешифратора 21, на одном из выходов которого возникает сигнал. Этот сигигзл приходит на вход 49 выбранного узла 22 управления циклом. На вход 28 блока циклов 7 с входа 16 приходит сигнал записи, который попадает на входы 46 всех узлов 22 управления циклом, В выбранном узле 22 управления циклом происходит срабатывание элемента И 38, сигнал с выхода которого идет на синхронизирующий вход регистра 35 и разрешает запись в него значения константы счета с информационного входа 43 узла 22 управления циклом. Таким же образом, меняя код номера узла на входе 14 устройства, загружают регистры 35 всех М узлов 22 управления циклом. В следующем цикле на вход перезаписи 29 блока 7 циклов с входа 17 устройства приходит сигнал, который попадает на вход 51 перезаписи всех узлов 22 управления циклом. В каждом таком узле сигнал проходит через элемент ИЛИ 42 и попадает на синхронизирующий вход

34счетчика, В него по этому сигналу перезаписывается содержимое регистра

35константы счета. Итак, устройство готово к работе в этом режиме после одного цикла загрузки адреса первого числа в регистр 1 адреса, М циклов загрузки счетчиков, М циклов загрузки регистров 35 и одного цикла перезаписи. Со следующего цикла на вход 12 подается сигнал, который открывает элемент И 5, на вход 13 подается сигнал, который проходит через элемент ИЛИ 6 и открывает эле - мент И А, отсутствие сигнала на управляющем входе 9 настраивает мультиплексор 2 на подключение выхода сумматора 3 к информационному входу регистра 1 адреса. Сигнал с входа 8 проходит через открытый элемент И 5 и попадает на тактирующий вход 24 блока 1ДИКЛОВ 7, дальше - на вход переноса 47 первого узла 22 управления циклом, а оттуда - на счетный вход счетчика 34, который по переднему фронту пришедшего счетного сигнала прибавляет 1 к содержимому счетчика. Если на выходе переноса счетчика 34 шагов не появляется сигнал, т.е. счетчик не переполняется, то от пришедшего тактового сигнала срабатывает элемент И 39 и сигнал с выхода этого элемента через элемент ИЛИ 41

970456

поступает на вход сч11тывания счетчика 33. Но этому сигналу с информационного выхода счетчика 33 значение шага через выход 50, информационный

с выход 32 поступает на второй вход сумматора 3, с выхода которого результат суммирования поступает через мультиплексор 2 на информаи;ионный вход регистра 1 адреса, куда записы10 веется по сигналу с тактирующего

входа 8 Такие циклы повторяются до . тех пор, т.е. константа шага из счетчика 33 первого узла управления циклом 22 подсуммируется до тех пор,

}5 пока на выходе переноса счетчика 34 не появится сигнал, который запирает элемент И 39, т.е. запрещает считывание значения шага из первого узла 22 управления циклом и поступает

20 на выход 52 переноса первого узла 22 управления циклом, а оттуда - на вход 47 переноса второго узла 22 управления циклом, в счетчике 34 которого по этому сигналу происходит

2.5 счет. Если после счета во втором узле 22 управления циклом на выходе переноса счетч:ика 34 шагов возникает сигнал, то он передается в следующий узел управления циклом. Если

30 такой сигнал не возникает, то во втором узле 22 управления циклом разрешается считывание значения шага из счетчика 33 на подсуммирование к регистру 1 адреса, В этом же цикле

jr в узлах 22 управления циклом, в которых произоше а счет счетчика 34 и возник перенос на его выходе, сиг- нал с выхода переноса счетчика 34 через элемент ШШ 42 поступает на

40 синхронизирующий вход счетчика 34. По заднему фронту этого сигнала,т.е. .в момент, когда происходит запись в регистр 1 ад1зеса, в счетчик 34 записывается содержимое регистра 35,

45 т.е. счетчик 34 восстанавливает свое первоначальное значение. Далее по тактовым импульсам с тактового ухода 8 устройства происходит аналогичная выборка значений шагов из

50 счетчиков 33 узлов 22 управления 1Д1КЛОМ для под суммирования к значению регистра 1 адреса. Это продолжается до тех пор, пока в последнем М-м узле 22 управления циклом на вы55 ходе переноса счетчика 34 шагов не появится сигнал, который через выход 52 переноса М-го узла 22 управления циклом, выход 25 переноса блока 7 циклов попадает на выход 20 устройства.. Адресация по этому режиму закончена.

Работа устройства адресации в режиме адресации многомерных массивов данных.

Пусть в пам.чти, начиная с адреса 1, записана по строкам матрица, состоящая из десяти строк и пяти столбцов, неоЪходимо считать эту матрицу с транспонированием. Определяют п 8 - количество разрядов в счетчике 33, регистре 35, счетчике 34. Для такой адресации необходимо два узла управления циклом 22 . Алгоритм адресации заключается в следующем: нужно сформировать адреса сначала первых элементов строк, затем вторых элементов и так далее, а в конце - пятых элементов строк. Чтобы сформировать адреса первых элементов строк, 20 предусмотрено использование только

нужно к 1 прибавить девять раз по 5, затем для получения адреса второго элемента первой строки, нужно вычесть 44 и сделать это 5 раз. В регистр 1 адреса заносится адрес, равный 00000001. В счетчик 32-первого узла 22 управления циклом заносится значение шага, равное 5 00000101. В счетчик 33 второго узла 22 управления циклом заносится 44 - в дополнительном коде 11010100. В регистр 35 первог о узла 22 управления циклом заносится двоичное дополнение 9 до , равное- 11110110. В регистр 35 второго узла 22 управления циклом 22 заносится двоичное дополнение 5 до , равное 11111010. Далее начинаются циклы формирования исполнительных адресов на выход 10. Счетчик 34 первого узла 22 управления циклом отсчитывает девять тактовых импульсо с тактового входа 12, в течение которых к значению регистра t адреса подсуммируется значение шага из счетчика 33 первого узла 22 управления циклом. В течение десятого тактового импульса перенос счетчика 34 шагов первого узла 22 управления циклом приходит на счетный вход счетчика шагов 34 второго узла 22 управления циклом и там сч1тгается. По концу этого переноса счетчик 34 шагов первого узла 22 управления цикло восстанавливает свое первоначаль- нбе значение. По десятому тактовому импульсу к значению регистра 1 адреса подсуммируется значение из счетчика 33 второго узла 22 управления ЦИКЛОМ. Такие циклы делаются 5 раз.

после чего на выходе 20 устройства появляется сигнал конца работы по этому режиму.

Использование блока циклов в устройстве адресации позволяет выполнять непрерывно адресацию данных, выбираемых из М-мерных массивов, а также отсчитывать количество адресуемых данных в этом режиме и вьщавать сигнал конца адресации в этом режиме. В известном устройстве невозможно отсчитывать количество адресуемых данных в этом режиме и выполнять непрерывно адресацию с переменным шагом адресации, так как для этого режима в нем после окончания адресации по одному шагу требуется время на загрузку следующего значения шага адресации, В известном устройстве

одного индексного регистра, тогда как в предлагаемом устройстве можно использовать несколько индексных регистров, что существенно расширяет 25 возможности адресации.

Формула изобретения

Устройство дпя формирования адре30 са, содержащее регистр адреса, мультиплексор, сумматор, два элемента И и элемент ИЛИ, причем информационный вход регистра адреса подключен к выходу мультиплексора, первый инj формационный вход которого подключен к выходу сумматора, вход первого слагаемого которого подключен к выходу регистра адреса, йинхровход которого подключен к выходу первого

40 элемента И, первый вход которого подключен к первому входу второго элемента И и является тактовым входом устройства, второй вход первого элемента И подключен к выходу эле-

45 мента ИЛИ, первый вход которого подключен к адресному входу мультиплексора и является входом режима адресации устройства, выход регистра адреса является выходом адреса уст50 ройства, отличающееся

тем, что, с целью расширения функциональных возможностей устройства за счет осуществления режима адресации многомерных массивов данных, в него

55 введен блок циклов, причем информационный вход блока циклов подключен к второму информационному входу мультиплексора и является информационным входом устройства, тактовый

9

вход блока циклов подключен к выходу второго элемента И, второй вКод которого является входом запуска устройства, второй вход элемента ИЛИ является входом вьщачи адреса устройства, вход номера узла блока циклов является входом номера измерния yctpoйcтвa, входы записи индекс записи шага, перезаписи, считывания и счетный вход блока циклов являются соответственно одноименными входами устройства, информационный выход блока циклов подключен к входу второго слагаемого устройства, выход окончания работы блока циклов является выходом окончания работы устройства, причем блок циклов содержит дешифратор узла и узлов управления циклом (где М - максимальная размерность адресуемого массива), причем вход дешифратора узла является входом номера узла блока циклов, i-й выход дешифратора узла (i 1, М) подключен к входу выборки i-ro узла управления циклом, вход переноса i-узла управления циклом подключен к выходу переноса (L - 1)-го узла управления циклому вход переноса первого узла управле-

узел управления никлом содержит два счетчика, регистр, четыре элемента И, элемент И-НЕ и два элемента ИЛИ, причем информационные входы первого счетчика и регистра подключены к информационному входу узла управления циклом, первые входы первого, второго, третьего и четвертого элементов И являются соответственно входом записи индекса, входом считывания, входом записи шага и входом переноса узла управления циклом, выход первого элемента И подключен к входу разрешения записи первого счетчика, счетный вход которого подключен к выходу элемента И-НЕ, первый вход которого является счетным входом узла управления циклом, вторые .входы первого, второго, третьего элементов И и элемента И-НЕ подключены к входу выборки узла управления циклом, выход второ го элемента И подключен к первому входу первого элемента ИЛИ, второй вход которого под- 25 ключен к выходу четвертого элемента И, а выход соединен с входом разрешения считывания первого счетчика, выход которого является информационным выходом узла управления циклом.

ния циклом подключен к тактовому вхо-30 первый вход второго элемента ИЛИ яв- ду блока циклов, выход переноса М-го узла управления циклом является выходом окончания работы блока циклов, .информационные входы узлов управления циклом подключены к информаи юн- 35 ному входу блока циклов, входы запиляется входом перезаписи узла управления циклом, второй вход подключен к выходу переноса второго счетчика, к второму входу четвертого элемента И и является выходом переноса узла управления циклом, выход второго элемента ИЛИ подключен к входу разрешения записи второго счетчика, информационный вход которого подключен к выходу регистра, вход разрешения записи которого подключен к выходу третьего элемента И, счетный вход второго счетчика подключен к входу переноса узла управления циклом.

си индекса, записи шага, перезаписи, считывания и счетные входы узлов управления циклом подключены соответг ственно к входам записи индекса, за- писи шага, перезаписи, считывания и счетному входу блока циклов, информационные выходы узлов управления циклом подключены к информационному выходу блока циклов, причем каждый

10

0

узел управления никлом содержит два счетчика, регистр, четыре элемента И, элемент И-НЕ и два элемента ИЛИ, причем информационные входы первого счетчика и регистра подключены к информационному входу узла управления циклом, первые входы первого, второго, третьего и четвертого элементов И являются соответственно входом записи индекса, входом считывания, входом записи шага и входом переноса узла управления циклом, выход первого элемента И подключен к входу разрешения записи первого счетчика, счетный вход которого подключен к выходу элемента И-НЕ, первый вход которого является счетным входом узла управления циклом, вторые .входы первого, второго, третьего элементов И и элемента И-НЕ подключены к входу выборки узла управления циклом, выход второ го элемента И подключен к первому входу первого элемента ИЛИ, второй вход которого под- 5 ключен к выходу четвертого элемента И, а выход соединен с входом разрешения считывания первого счетчика, выход которого является информационным выходом узла управления циклом.

5

0

первый вход второго элемента ИЛИ яв-

ляется входом перезаписи узла управления циклом, второй вход подключен к выходу переноса второго счетчика, к второму входу четвертого элемента И и является выходом переноса узла управления циклом, выход второго элемента ИЛИ подключен к входу разрешения записи второго счетчика, информационный вход которого подключен к выходу регистра, вход разрешения записи которого подключен к выходу третьего элемента И, счетный вход второго счетчика подключен к входу переноса узла управления циклом.

п

Сиг г

чч

9игЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство адресации | 1987 |

|

SU1418712A1 |

| Устройство адресации | 1985 |

|

SU1267416A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| Процессор быстрого преобразования Фурье | 1987 |

|

SU1425709A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Устройство для сжатия информации | 1982 |

|

SU1043711A1 |

| Динамическое запоминающее устройство с восстановлением информации | 1989 |

|

SU1689990A1 |

| Устройство для цифровой фильтрации | 1987 |

|

SU1621045A1 |

Изобретение относится к вычислительной технике и может быть использовано для формирования адресов данных в цифровых вычислительных машинах. Цель изобретения - расширение функциональных возможностей устройств за счет обеспечения режима адресации многомерных массивов данных. Устройство содержит регистр 1 адреса, мультиплексор 2, сумматор 3, элементы И 4, 5, элемент ИЛИ 6 и блок 7 циклов, выполненный на узлах управления циклом, числом, равным размерг ности массива. Блок 7 в режиме адресации многомерных массивов производит переключение значений шагов адресации, отсчитывает подсуммирова- ние каждого шага адресации, выдает сигнал окончания адресации по данному режиму. 3 ил. с 5 (Л фи5.1

Редактор Л.Иовхан

Составитель Н.Захаревич

Техред М.Моргентал Корректор И.Эрдейн

Заказ 1347Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для формирования адреса | 1979 |

|

SU826350A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Формирователь адреса | 1982 |

|

SU1062703A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования адреса данных | 1982 |

|

SU1068939A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-15—Публикация

1985-10-08—Подача