Изобретение относится к вычислительной технике и может быть использовано для построения множительных устройств для вычислительных средств с после; овательной поразрядной обработкой операндов.

Цель изобретения - повьшение быстродействия устройства.

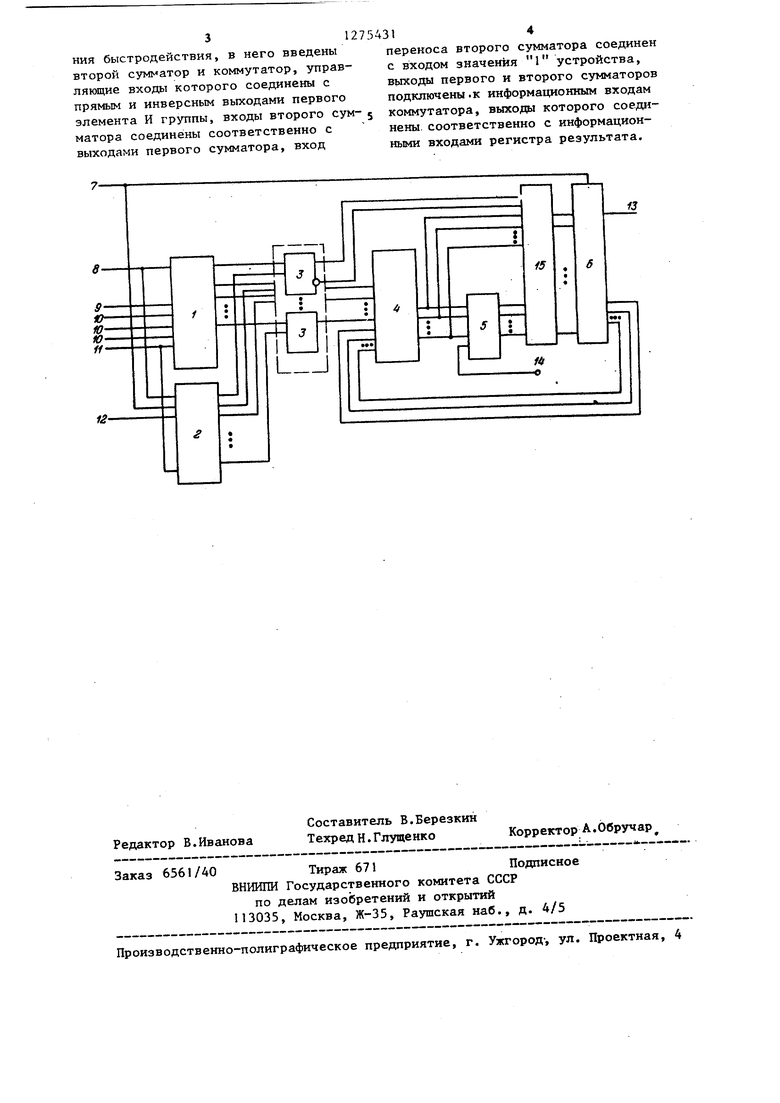

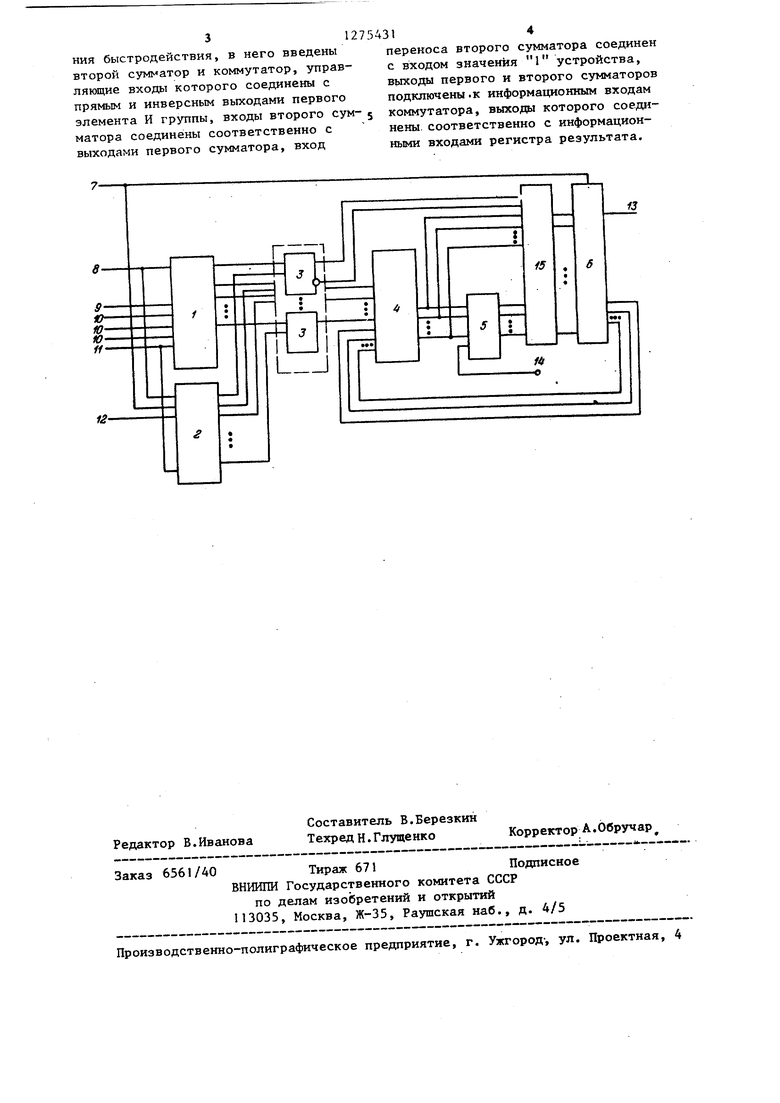

На чертеже представлена структурная схема устройства для умножения.

Устройство для з множения содержит регистр 1 множимого, регистр 2 множителя, группу элементов И 3, первый сумматор 4, второй сумматор 5, регистр 6 результата, первый вход 7 записи, информационный вход 8, второй вход 9 записи, адресные входы 10, вход 11 сброса, третий вход 12 записи, выход 13 результата вход 14 значения I и коммутатор 15,

Устройство работает следующим образом.

В младший разряд, предварительно обнуленного импульсом по входу 11 регистра , заносится с входа 8 по импульсу на входе 9 младший разряд множимого. Номер разряда регистра множимого, в который производится занесение, определяется информацией на входах 10. Информация с выхода регистра 1 поступает на входы элементов ИЗ. Затем в владший разряд регистра 2 заносится с входа 8 по импульсу на входе 12 младший разряд множителя. Информация с выхода регистра 2 поступает на другие входы элемента ИЗ. Частные произведения с выходов элементов И 3 (кроме первого) поступают на входы первого разряда сумматора 4, который, таким образом, представляет собой схему подсчета числа единиц. Выход первого элемента И 3 в прямом и инверсном виде поступает на управляющие входы коммутатора 15 .При равенстве его нулю на выходы коммутато- 45 вый

ра 15 передается содержимое выходов сумматора 4, а при равенстве единице передается содержимое сумматора 5 (увеличенное на единицу). После этого информация с выходов коммутатора 15 записьшается по импульсу с входа 7 в регистр 6, на младшем выходе которого появляется младший разряд произведения, а на старших - переносы в следующие разряды, поступающие на входы разрядов сумматора 4. Одновременно с записью в регистр 6 импульсом с входа 7 осзпцествляется сдвиг содержимого регистра 2 на один разряд в сторону старших разрядов с занесением в младший разряд нуля. Затем в следующий разряд регистра 1 заносится следующий разряд множимого. С этого момента начинается вычисление очередного разряда произведения, причем в результате подготавливаются два значения: одно в предположении равенства очередного разряда множителя нулю, другое в предположении равенства его единице (соответственно сумматором 4 и сумматором 5).

Поступающий в регистр 2 (в младщий разряд) очередной разряд множителя определяет, какой из предварительно полученных результатов является верным и передает его на выходе коммутатора 15 для записи в регистр 6.

Формулаиз обретения

Устройство для умножения, содержащее группу элементов И, первый сумматор, регистр множимого, регистр множителя и регистр результата, выход младшего разряда которого соединен с выходом результата устройства, тактовый вход регистра результата соединен с первым входом записи устройства и входом сдвига регистра множителя, выходы старших разрядов регистра результата соединены соответственно с входами соответствующих разрядов первого сумматора, входы первого разряда которого соединены с выходами элементов И группы, начиная с второго, первые входы элементов И группы соединены с выходами соответствующих разрядов регистра множимого, информационный вход которого соединен с информационньм входом регистра множителя и с информационным входом устройства, тактонен с вторым входом записи устройства, управляющие входы разрешения записи регистра множимого соединены с адресными входами устройства, вход

50 сброса, устройства соединен с входом сброса регистра множимого и входом сброса регистра множителя, тактовый вход которого соединен с третьим входом записи устройства, выходы разря95 дов регистра множителя соединены с вторыми входами соответствуняцих элементов И грзп1пы, отличающ а ее я тем, что, с целью повьш1евход регистра множимого соединия быстродействия, в него введены второй сумматор и коммутатор, управляющие входы которого соединены с прямым и инверсным выходами первого элемента И группы, входы второго сумматора соединены соответственно с выходами первого сумматора, вход

переноса второго сумматора соединен с входом значения 1 устройства, выходы первого и второго сумматоров подключены.к информационным входам коммутатора, выходы которого соединены соответственно с информационными входами регистра результата.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1984 |

|

SU1265762A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Устройство для умножения данных переменной длины | 1985 |

|

SU1291972A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для умножения | 1983 |

|

SU1200280A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

Изобретение относится к области вычислительной техники и может быть использовано для построения множительных устройств для вычислительных средств с последовательной поразрядной обработкой операндов. Цель изобретения - повышение быстродействия. Быстродействие устройства повышается за счет предварительного анализа очередного разряда множителя и вьщачи результата в соответствии с действительным значением этого разряда. Анализ осуществляется на введенном коммутаторе, конъюнкция очередных разрядов множимого и множителя управляет вьщачей результ.ата на регистр результата. Операнды поступают в регистры множимого и множителя, начиная с младших разрядов. После формирования частных произведений элементами И группы первым сумматором осуществляется формирование первого произведения без учета младшего частного произведения. Сформированное первое произведение поступает на введенный второй суммаi тор, который формирует второе произведение в предположении равенства (Л единице младшего частного произведения, действительное значение которого определяется после занесения в регистр множителя очередного разряда множителя, и управляет выдачей на регистр результата первого или второto ел го произведения. 1 ил. 4 СО

| Lehman М | |||

| Serial arithmetic technigues | |||

| - Proc | |||

| AFIPSFK., 1965, pp | |||

| ВЕНТИЛЯЦИОННАЯ ПОТОЛОЧНАЯ КРЫШКА ДЛЯ ВАГОНОВ | 1923 |

|

SU715A1 |

| Baker P.W., McCren P.G | |||

| Highspeed serial tree multiplier | |||

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Питательное приспособление к трепальной машине для лубовых растений | 1923 |

|

SU343A1 |

Авторы

Даты

1986-12-07—Публикация

1984-12-28—Подача