Изобретение относится к постоянным запоминающим устройствам и может использоваться в электронных вычислительных машинах (ЭВМ) высокой надежности.

Цель изобретения - уменьшение потребляемой мощности.

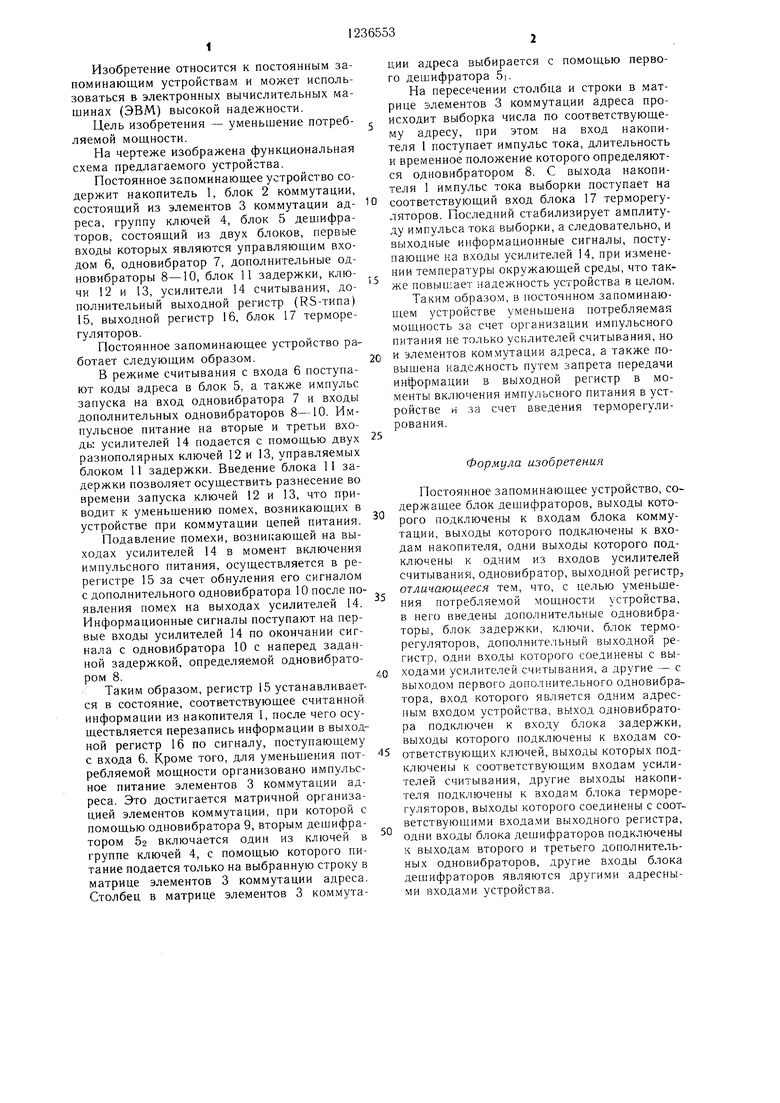

На чертеже изображена функциональная схема предлагаемого устройства.

Постоянное запоминающее устройство содержит накопитель 1, блок 2 коммутации, состоящий из элементов 3 коммутации адреса, группу ключей 4, блок 5 дешифраторов, состоящий из двух блоков, первые входы которых являются управляющим входом 6, одновибратор 7, дополнительные од- новибраторы 8-10, блок 11 задержки, ключи 12 и 13, усилители 14 считывания, дополнительный выходной регистр (RS-типа) 15, выходной регистр 16, блок 17 терморегуляторов.

Постоянное запоминающее устройство работает следующим образом.

В режиме считывания с входа 6 поступают коды адреса в блок 5, а также импульс запуска на вход одновибратора 7 и входы дополнительных одновибраторов 8-10. Импульсное питание на вторые и третьи входы усилителей 14 подается с помощью двух разнополярных ключей 12 и 13, управляемых блоком 11 задержки. Введение блока 11 задержки позволяет осуществить разнесение во времени запуска ключей 12 и 13, что приводит к уменьшению помех, возникающих в устройстве при коммутации цепей питания.

Подавление помехи, возникающей на выходах усилителей 14 в момент включения импульсного питания, осуществляется в ре- регистре 15 за счет обнуления его сигналом с дополнительного одновибратора 10 после появления помех на выходах усилителей 14. Информационные сигналы поступают на первые входы усилителей 14 по окончании сигнала с одновибратора 10 с наперед заданной задержкой, определяемой одновибрато- ром 8.

Таким образом, регистр 15 устанавливается в состояние, соответствующее считанной информации из накопителя 1, после чего осуществляется перезапись информации в выходной регистр 16 по сигналу, поступающему с входа 6. Кроме того, для уменьшения потребляемой мощности организовано импульсное питание элементов 3 коммутации адреса. Это достигается матричной организацией элементов коммутации, при которой с помощью одновибратора 9, вторым дешифратором 52 включается один из ключей в группе ключей 4, с помощью которого питание подается только на выбранную строку в матрице элементов 3 коммутации адреса. Столбец в матрице элементов 3 коммута

ции адреса выбирается с помощью первого дешифратора 5i.

На пересечении столбца и строки в матрице элементов 3 коммутации адреса происходит выборка числа по соответствующему адресу, при этом на вход накопителя 1 поступает импульс тока, длительность и временное положение которого определяются одновибратором 8. С выхода накопителя 1 импульс тока выборки поступает на соответствующий вход блока 17 терморегуляторов. Последний стабилизирует амплитуду импульса тока выборки, а следовательно, и выходные информационные сигналы, поступающие на 5ходы усилителей 14, при изменении температуры окружающей среды, что также повышает надежность устройства в целом.

Таким образом, в постоянном запоминающем устройстве уменьшена потребляемая мощность за счет организации импульсного питания не только усилителей считывания, но и элементов коммутации адреса, а также повышена надежность путем запрета передачи информации в выходной регистр в моменты включения импульсного питания в устройстве и за счет введения терморегулирования.

0

0

5

0

Формула изобретения

Постоянное запоминающее устройство, со- держашее блок дешифраторов, выходы которого подключены к входам блока коммутации, выходы которого подк тючены к входам накопителя, одни выходы которого подключены к одним из входов усилителей считывания,одновибратор, выходной регистр, отличающееся тем, что, с целью уменьшения потребляемой мощности устройства, в него введены дополнительные одновибра- торы, блок задержки, ключи, блок терморегуляторов, дополните.чьный В1з1ходной регистр, одни входы которого соединены с выходами усилителей считывания, а другие - с выходом первого дополнительного одновибратора, вход которого является одним адресным входом устройства, выход одновибратора подключен к входу блока задержки, выходы которого подключены к входам соответствующих ключей, выходы которых подключены к соответствующим входам усилителей считывания, другие выходы накопителя подключены к входам блока терморегуляторов, выходы которого соединены с соответствующими входами выходного регистра, одни входы блока дешифраторов подключены к выходам второго и третьего дополнительных одновибраторов, другие входы блока дешифраторов являются другими адресными входами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1985 |

|

SU1280455A1 |

| Запоминающее устройство | 1983 |

|

SU1117709A1 |

| Запоминающее устройство | 1976 |

|

SU608197A1 |

| Устройство для контроля микросхем постоянной памяти | 1987 |

|

SU1478258A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Запоминающее устройство | 1980 |

|

SU873275A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1247949A1 |

| Оперативное запоминающее устройство | 1981 |

|

SU970462A1 |

| Запоминающее устройство | 1979 |

|

SU773723A1 |

| Запоминающее устройство | 1975 |

|

SU627539A1 |

Изобретение относится к постоянным запоминающим устройствам и .может быть использовано в ЭВМ высокой надежности. Цель изобретения - уменьшение потребляемой мощности. Постоянное запоминающее устройство содержит накопитель, блок коммутации, состоящий из элементов коммутации адреса, группу ключей, блок дешифраторов, состоящий из двух блоков, основной и три дополнительны.х одновибратора, блок задержки, ключи, усилители считывания, основной и дополнительный вы.ходные регистры, блок терморегуляторов. В устройстве достигается уменьшение потребляе.мой мощности за счет организации импульсного питания не только усилителей считывания, но и элементов коммутации адреса, а также повышена надежность за счет запрета передачи информации в вы.ходной регистр в г.юменты передачи информации в вы.ход- .чой регистр, в мо.менты включения импульсного питания в устройстве, а также за счет введения терморегулирования. 1 ил. S (Л 00 05 СП СП СО

| Постоянное запоминающее устройство | 1977 |

|

SU746730A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Модуль постоянной памяти | 1979 |

|

SU905858A1 |

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

Авторы

Даты

1986-06-07—Публикация

1984-11-19—Подача