Изобретение относится к вычислительной технике и может быть использовано при построении буферных запоминающих устройств многоканальных систем сбора и обработки измерительной информации.

Цель изобретения - повьпиение надежности устройства.

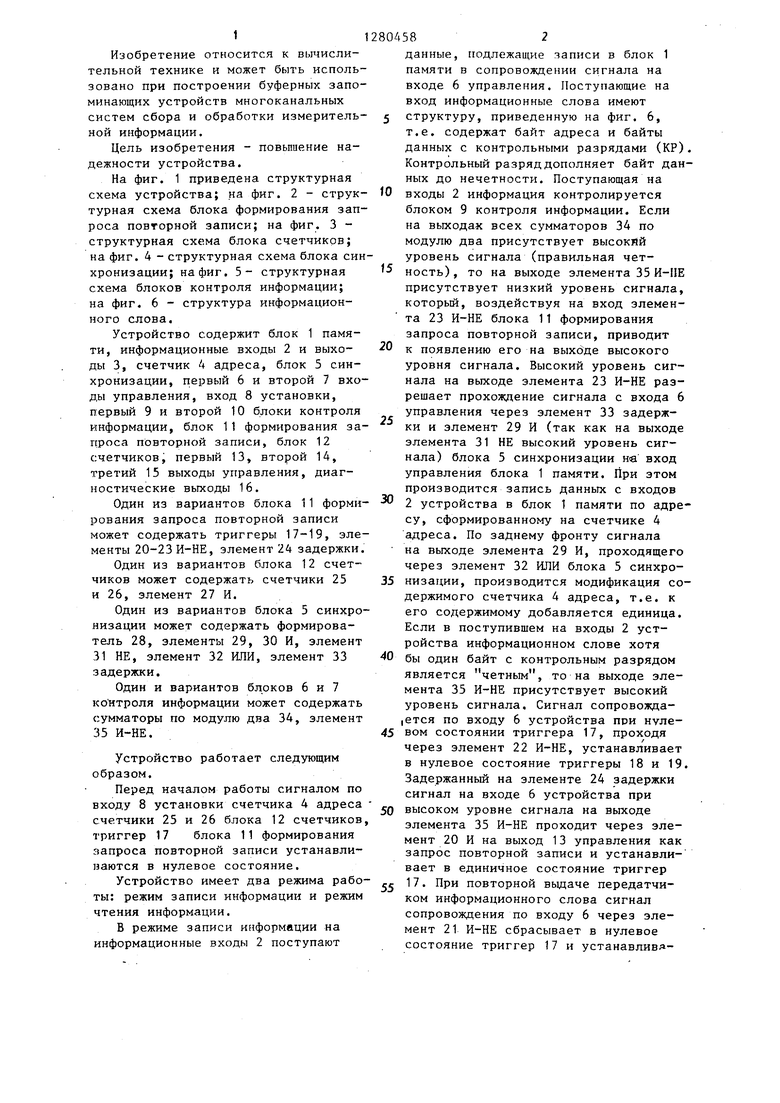

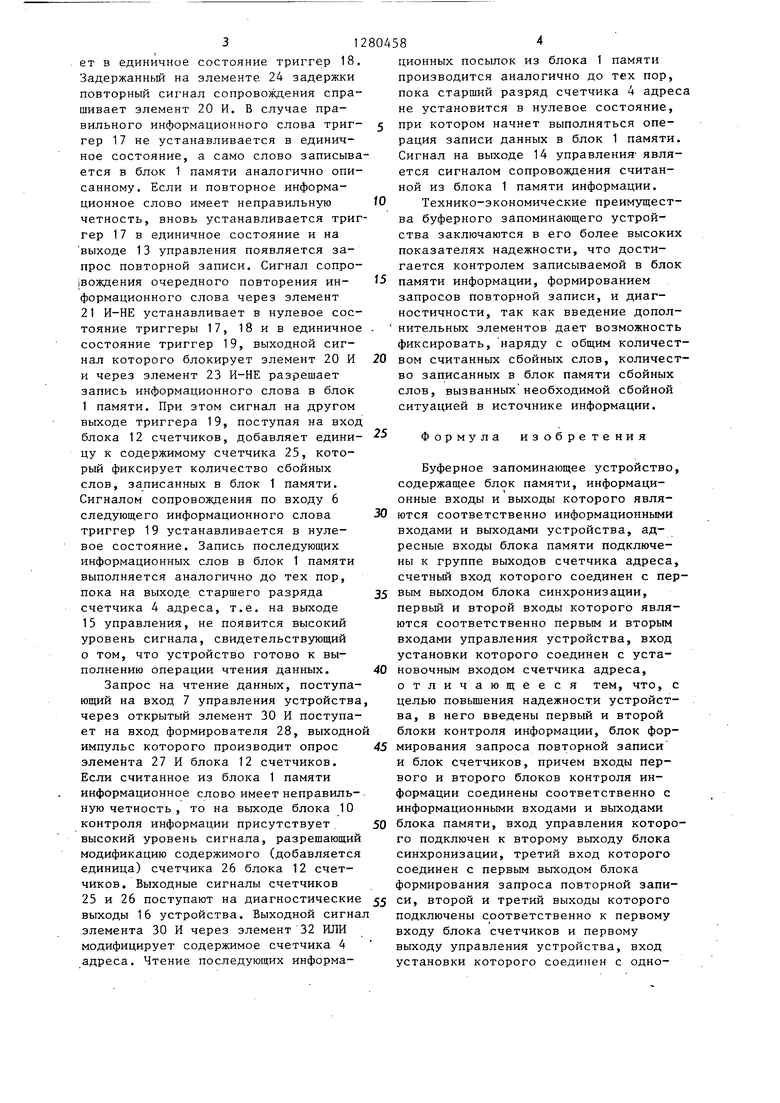

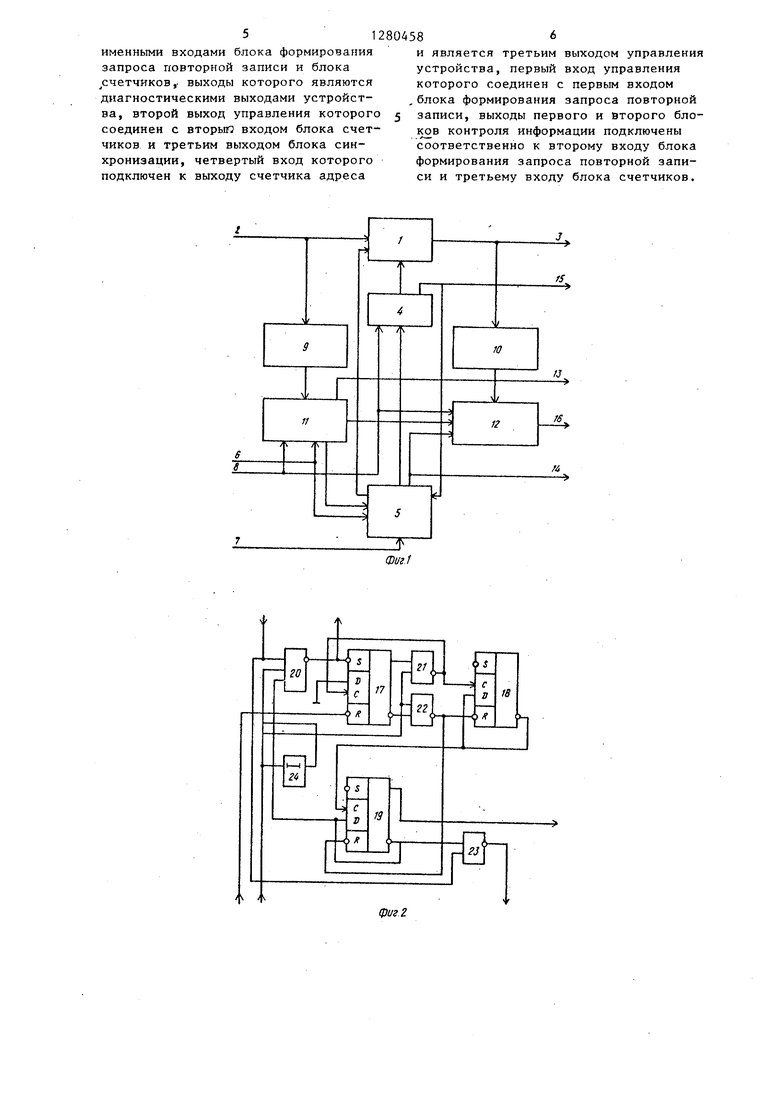

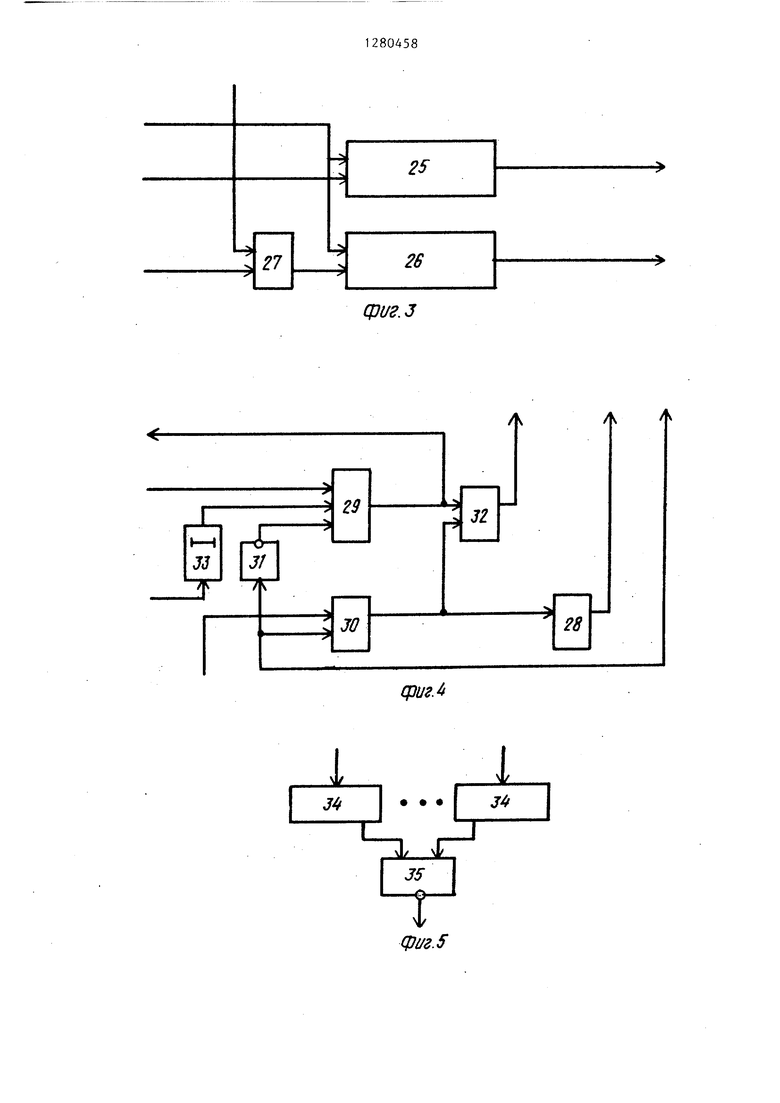

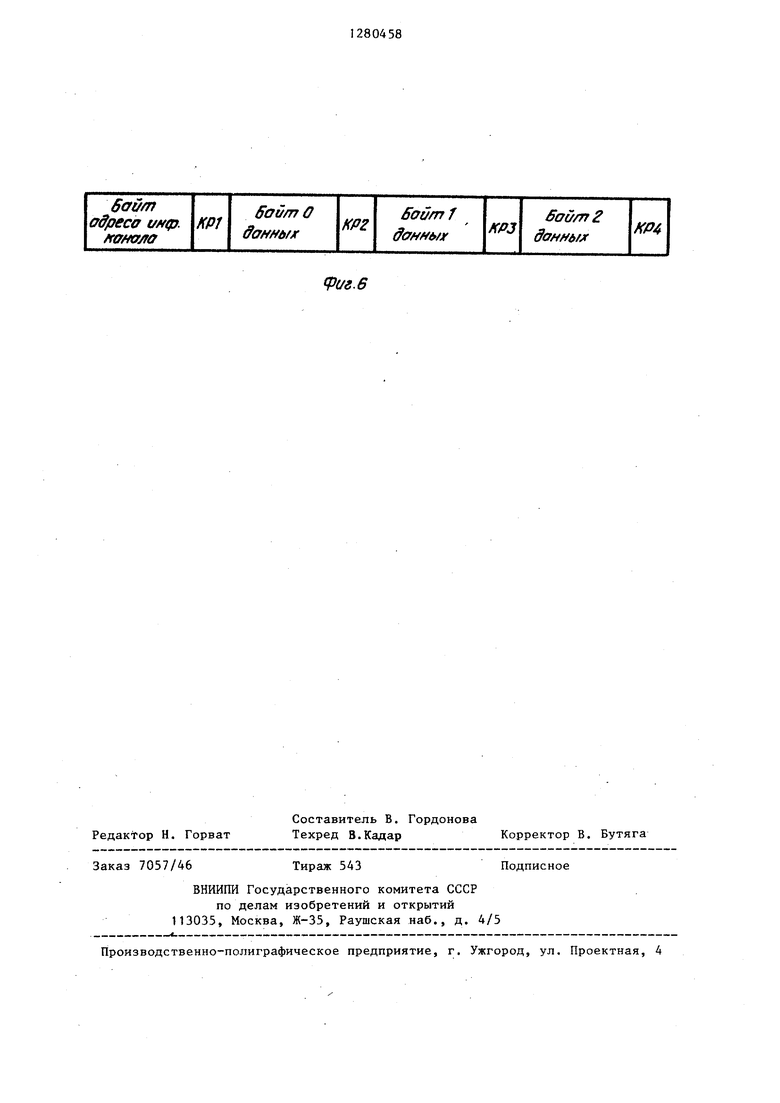

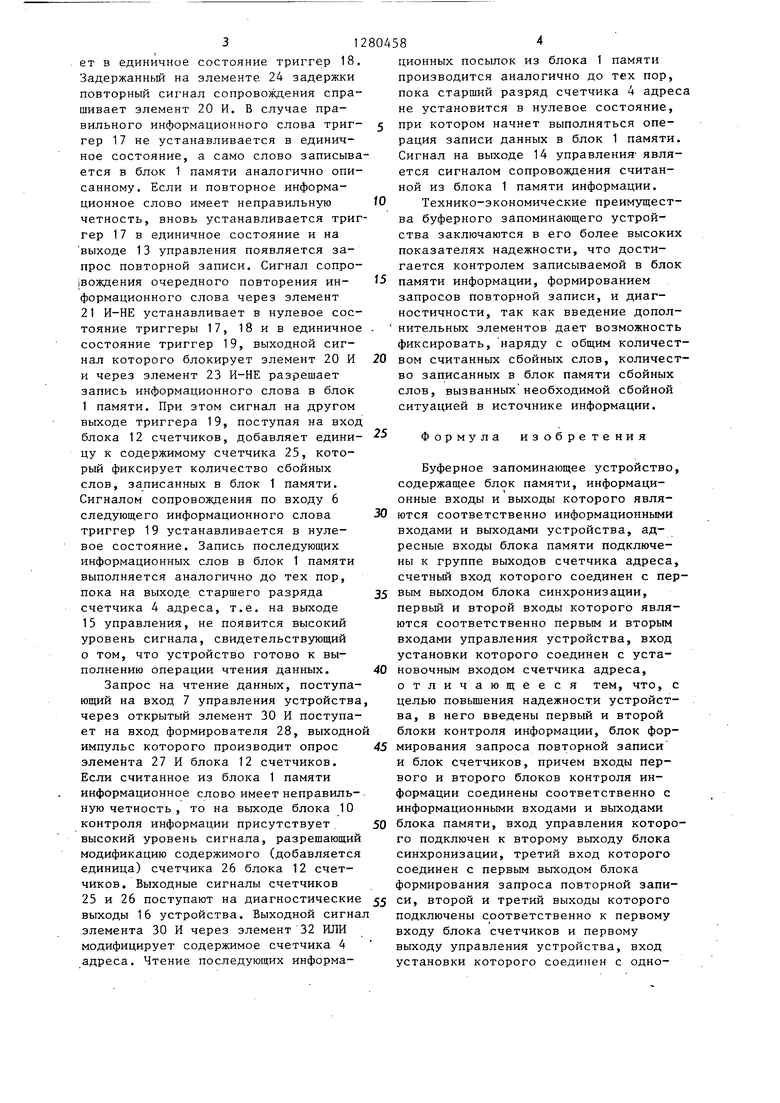

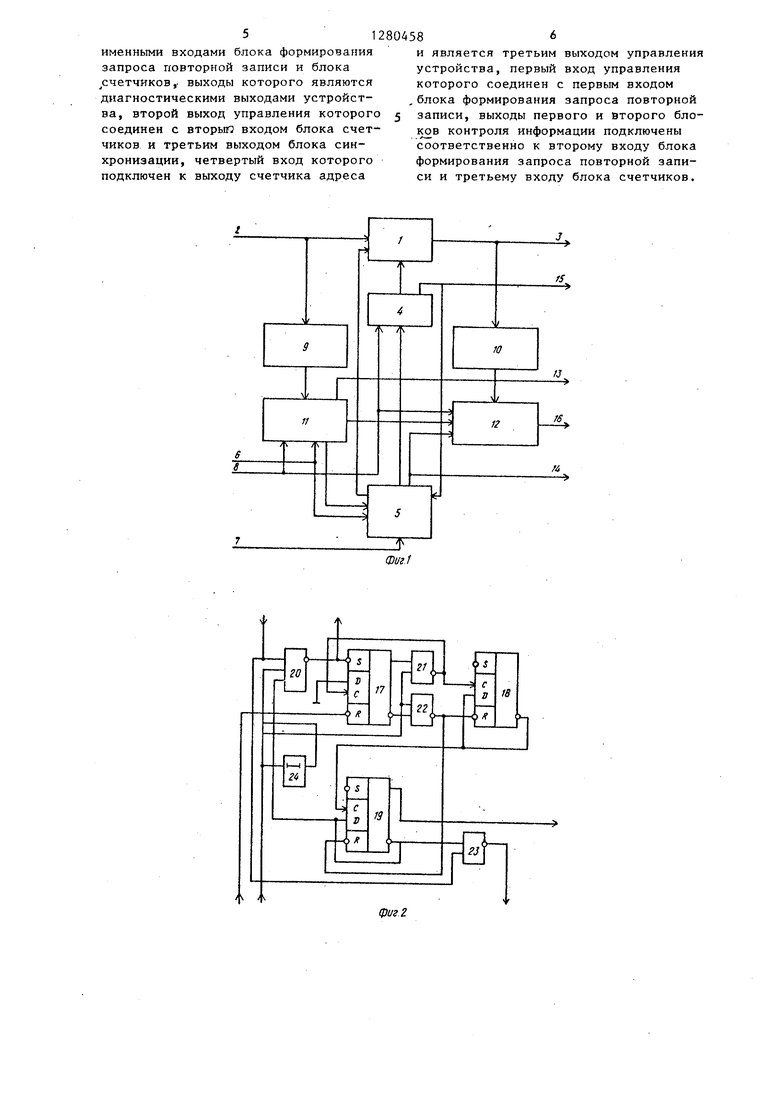

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - структурная схема блока формирования запроса повторной записи; на фиг. 3 - структурная схема блока счетчиков; на фиг. 4 - структурная схема блока синхронизации; на фиг. 5- структурная схема блоков контроля информации; на фиг. 6 - структура информационного слова.

Устройство содержит блок 1 памяти, информационные входы 2 и выходы 3, счетчик 4 адреса, блок 5 синхронизации, первый 6 и второй 7 входы управления, вход 8 установки, первый 9 и второй 10 блоки контроля информации, блок 11 формирования запроса повторной записи, блок 12 счетчиков, первый 13, второй 14, третий 15 выходы управления, диагностические выходы 16.

Один из вариантов блока 11 формирования запроса повторной записи может содержать триггеры 17-19, элементы 20-23 И-НЕ, элемент 24 задержки.

Один из вариантов блока 12 счетчиков может содержать счетчики 25 и 26, элемент 27 И.

Один из вариантов блока 5 синхронизации может содержать формирователь 28, элементы 29, 30 И, элемент 31 НЕ, элемент 32 ИЛИ, элемент 33 задержки.

Один и вариантов блоков 6 и 7 контроля информации может содержать сумматоры по модулю два 34, элемент 35 И-НЕ.

Устройство работает следующим образом.

Перед началом работы сигналом по входу 8 установки счетчика 4 адреса счетчики 25 и 26 блока 12 счетчиков триггер 17 блока 11 формирования запроса повторной записи устанавливаются в нулевое состояние.

Устройство имеет два режима рабо- 17. При повторной выдаче передатчи- ты: режим записи информации и режим ком информационного слова сигнал чтения информации.

В режиме записи информации на

сопровождения по входу 6 через элемент 21 И-НЕ сбрасывает в нулевое состояние триггер 17 и устанавливдинформационные входы 2 поступают

данные, подлежащие записи в блок 1 памяти в сопровождении сигнала на входе 6 управления. Поступающие на вход информационные слова имеют структуру, приведенную на фиг. 6, т.е. содержат байт адреса и байты данных с контрольными разрядами (КР). Контрольный разряд дополняет байт данных до нечетности. Поступающая на входы 2 информация контролируется блоком 9 контроля информации. Если на выходах всех сумматоров 34 по модулю два присутствует высокий уровень сигнала (правильная чет- ность), то на выходе элемента 35 И-11Е присутствует низкий уровень сигнала, который, воздействуя на вход элемента 23 И-НЕ блока 11 формирования запроса повторной записи, приводит к появлению его на выходе высокого уровня сигнала. Высокий уровень сигнала на выходе элемента 23 И-НЕ разрешает прохождение сигнала с входа 6 управления через элемент 33 задержки и элемент 29 И (так как на выходе элемента 31 НЕ высокий уровень сигнала) блока 5 синхронизации не вход управления блока 1 памяти. При этом производится запись данных с входов

2 устройства в блок 1 памяти по адре

су, сформированному на счетчике 4 адреса. По заднему фронту сигнала на выходе элемента 29 И, проходящего через элемент 32 ИЛИ блока 5 синхронизации, производится модификация содержимого счетчика 4 адреса, т.е. к его содержимому добавляется единица. Если в поступившем на входы 2 устройства информационном слове хотя бы один байт с контрольным разрядом является четным, то на выходе элемента 35 И-НЕ присутствует высокий уровень сигнала. Сигнал сопровожда- ется по входу 6 устройства при нулевом состоянии триггера 17, проходя

через элемент 22 И-НЕ, устанавливает в нулевое состояние триггеры 18 и 19. Задержанный на элементе 24 задержки сигнал на входе 6 устройства при высоком уровне сигнала на выходе элемента 35 И-НЕ проходит через элемент 20 И на выход 13 управления как запрос повторной записи и устанавли- вает в единичное состояние триггер

17. При повторной выдаче передатчи- ком информационного слова сигнал

17. При повторной выдаче передатчи- ком информационного слова сигнал

сопровождения по входу 6 через элемент 21 И-НЕ сбрасывает в нулевое состояние триггер 17 и устанавливдет в единичное состояние триггер 18. Задержанньш на элементе 24 задержки повторный сигнал сопровождения спрашивает элемент 20 И. В случае правильного информационного слова триггер 17 не устанавливается в единичное состояние, а само слово записывается в блок 1 памяти аналогично описанному. Если и повторное информационное слово имеет неправильную четность, вновь устанавливается триггер 17 в единичное состояние и на выходе 13 управления появляется запрос повторной записи. Сигнал сопро- |вождения очередного повторения информационного слова через элемент 21 И-НЕ устанавливает в нулевое состояние триггеры 17, 18 и в единичное состояние триггер 19, выходной сигнал которого блокирует элемент 20 И и через элемент 23 И-НЕ разрешает запись информационного слова в блок 1 памяти. При этом сигнал на другом выходе триггера 19, поступая на вход блока 12 счетчиков, добавляет единицу к содержимому счетчика 25, который фиксирует количество сбойных слов, записанных в блок 1 памяти. Сигналом сопровождения по входу 6 следующего информационного слова триггер 19 устанавливается в нулевое состояние. Запись последующих информационных слов в блок 1 памяти выполняется аналогично до тех пор, пока на выходе старшего разряда счетчика 4 адреса, т.е. на выходе 15 управления, не появится высокий уровень сигнала, свидетельствующий о том, что устройство готово к выполнению операции чтения данных.

Запрос на чтение данных, поступающий на вход 7 управления устройства через открытый элемент 30 И поступает на вход формирователя 28, выходно импульс которого производит опрос элемента 27 И блока 12 счетчиков. Если считанное из блока 1 памяти информационное слово имеет неправильную четность , то на выходе блока 10 контроля информации присутствует высокий уровень сигнала, разрешающий модификацию содержимого (добавляется единица) счетчика 26 блока 12 счетчиков. Выходные сигналы счетчиков 25 и 26 поступают на диагностические выходы 16 устройства. Выходной сигна элемента 30 И через элемент 32 ИЛИ модифицирует содержимое счетчика 4 адреса. Чтение последующих информационных посылок из блока 1 памяти производится аналогично до тех пор, пока старший разряд счетчика 4 адреса не установится в нулевое состояние,

при котором начнет выполняться операция записи данных в блок 1 памяти. Сигнал на выходе 14 управления- является сигналом сопровождения считанной из блока 1 памяти информации.

Технико-экономические преимущества буферного запоминающего устройства заключаются в его более высоких показателях надежности, что достигается контролем записываемой в блок

памяти информации, формированием запросов повторной записи, и диаг- ностичности, так как введение допол- нительных элементов дает возможность фиксировать, наряду с общим количеством считанных сбойных слов, количество записанных в блок памяти сбойных слов, вызванных необходимой сбойной ситуацией в источнике информации.

25

Формула изобретения

Буферное запоминающее устройство, содержащее блок памяти, информационные входы и выходы которого являются соответственно информационными входами и выходами устройства, адресные входы блока памяти подключены к группе выходов счетчика адреса, счетный вход которого соединен с первым выходом блока синхронизации,

первый и второй входы которого являются соответственно первым и вторым входами управления устройства, вход установки которого соединен с установочным входом счетчика адреса,

отличающееся тем, что, с целью повышения надежности устройства, в него введены первый и второй блоки контроля информации, блок формирования запроса повторной записи и блок счетчиков, причем входы первого и второго блоков контроля информации соединены соответственно с информационными входами и выходами

блока памяти, вход управления которого подключен к второму выходу блока синхронизации, третий вход которого соединен с первым выходом блока формирования запроса повторной записи, второй и третий выходы которого подключены соответственно к первому входу блока счетчиков и первому выходу управления устройства, вход установки которого соединен с одноименньми входами блока формирования запроса повторной записи и блока счетчиков,, выходы которого являются диагностическими выходами устройства, второй выход управления которого соединен с вторып входом блока счетчиков и третьим выходом блока синхронизации, четвертый вход которого подключен к выходу счетчика адреса

0458

и является третьим выходом управления устройства, первый вход управления которого соединен с первым входом блока формирования запроса повторной записи, выходы первого и второго блоков контроля информации подключены соответственно к второму входу блока формирования запроса повторной записи и третьему входу блока счетчиков.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Устройство для контроля блоков буферной памяти | 1987 |

|

SU1501175A1 |

| Устройство для сопряжения источника и приемника информации | 1989 |

|

SU1730630A2 |

| Буферное запоминающее устройство | 1985 |

|

SU1295451A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1658160A1 |

| Устройство для буферизации информации | 1988 |

|

SU1559350A1 |

| Устройство для буферизации информации | 1988 |

|

SU1541624A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163357A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1249583A1 |

Изобретение может быть использовано при построении буферных запоминающих устройств многоканальных систем сбора, регистрации и обработки измерительной информации. Цель изобретения - повышение надежности и диагностической способности устройства за счет введения контроля записываемой информации, формирования запросов повторной записи и фиксации сбойных сообщений, записанны в блок памяти устройства, из-за необратимой сбойной ситуации в источнике сообщений. 6 ил. с S

фиг г

27

3

26

фие.з

ери г Л

3

Ч.

35

фиг.5

чрс/г.6

Редактор Н. Горват

Составитель В. Гордонова

Техред В.КадарКорректор В. Бутяга

Заказ 7057/46

Тираж 543

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Подписное

| № 3955178/24-24 18.09.85 30.12.86 | |||

| Бюл | |||

| Приспособление для автоматической односторонней разгрузки железнодорожных платформ | 1921 |

|

SU48A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1986-12-30—Публикация

1985-09-18—Подача