Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах на КМДП транзисторах для считывания информации .

Цель изобретения - повышение быстродействия усилителя.

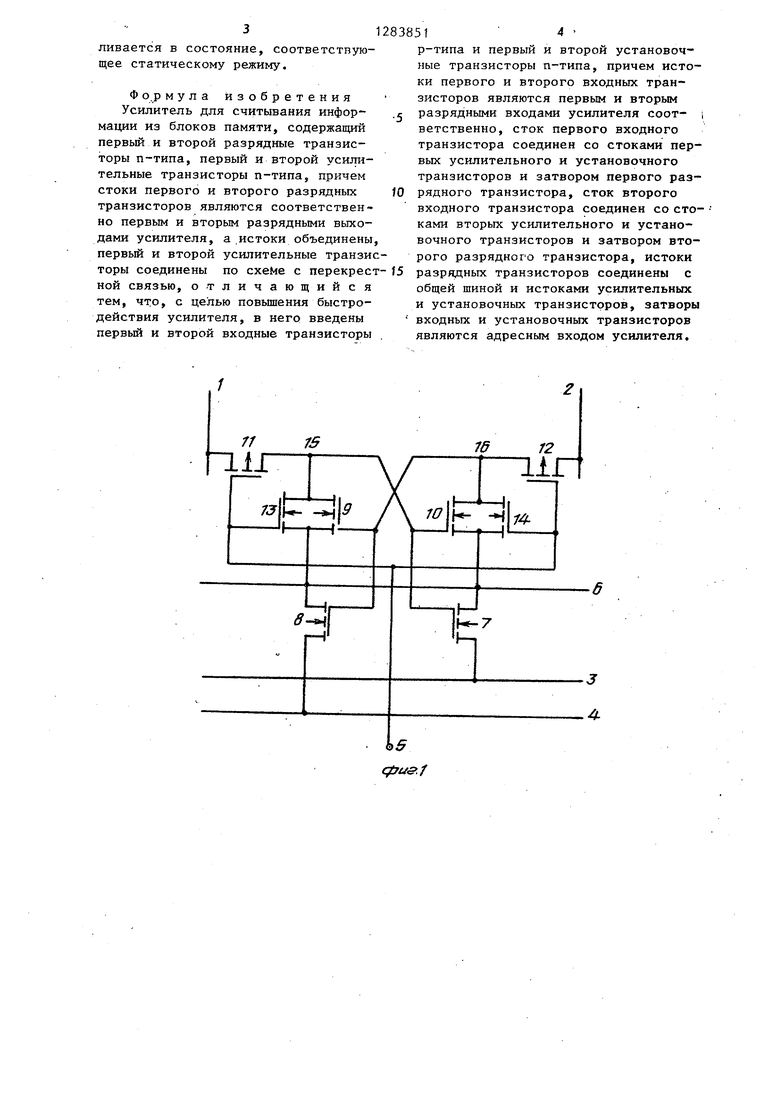

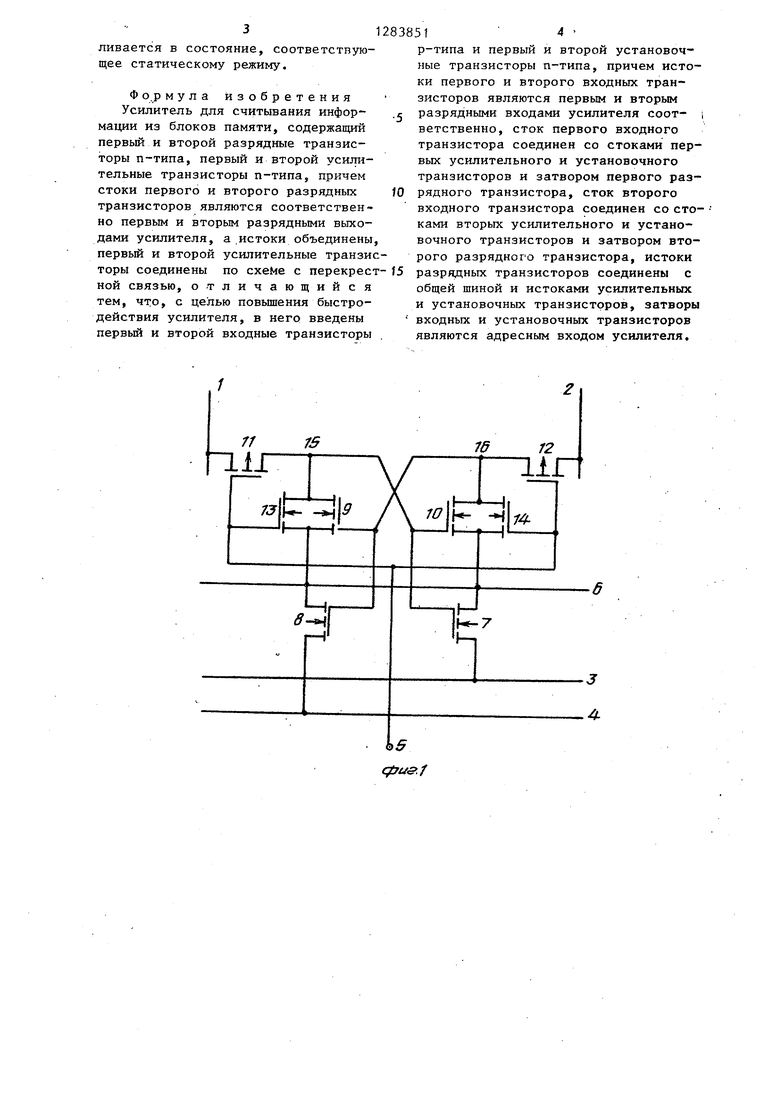

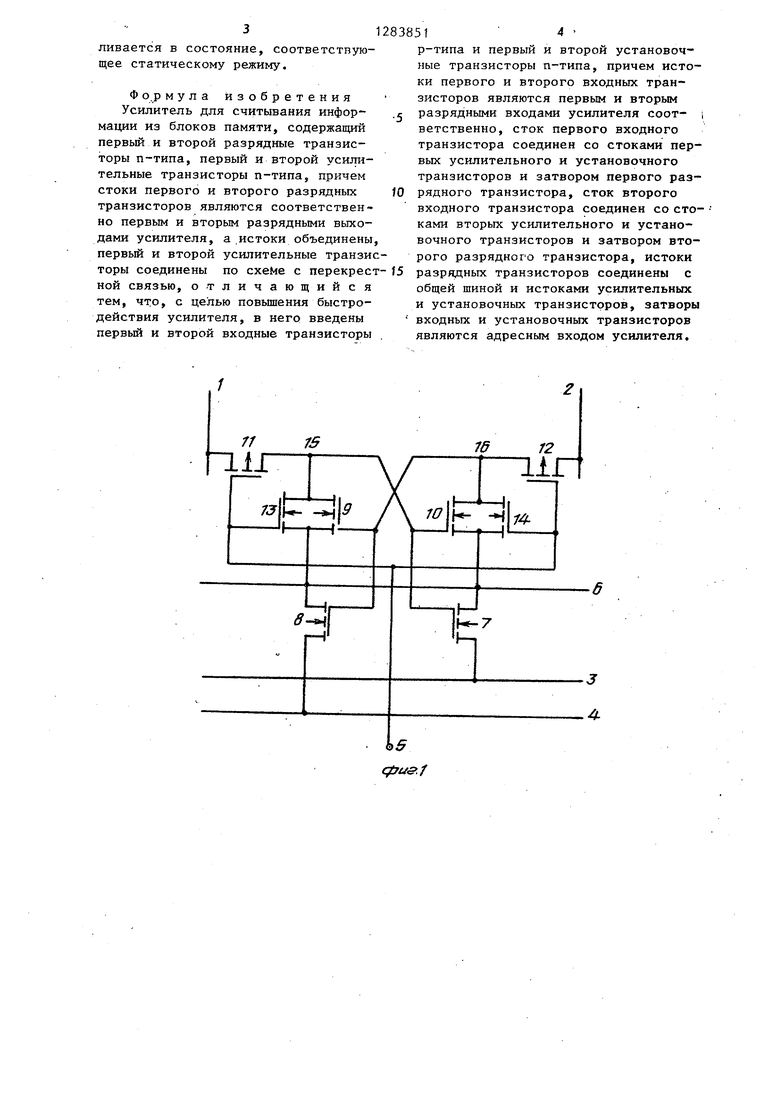

На фиг. 1 показана схема предлагаемого устройства; на фиг. 2 - диаграмма работы усилителя считывания.

Устройство для считывания инфор- маидяи из блоков памяти содержит первый 1 и второй 2 разрядные йходы, первый 3 и второй 4 разрядные выходы, адресный вход 5, общую шину 6, первый 7 и второй В разрядные транзисторы п-типа, первый 9 и второй 10 усилительные транзисторы п-типа, а также первый 11 и второй 12 входные транзисторы р-типа, первый 13 и второй 14 установочные транзисторы п- типа, внутренние узлы 15 и 16, причем стоки первого и второго разрядных транзисторов 7 и 8 соединены с первым и вторым выходными разрядными выходами 3 и 4 соответственно, а ис- тойй объединены, первый и второй усилительные транзисторы 9 и 10 соединены по схеме с перекрестной связью, истоки первого и второго входных транзисторов 11 и 12 соединены с первым и вторьш разрядными входами 1 и 2 соответственно, сток первого входного транзистора 11 соединен со стоками первых усилительного 9 и установочного 13 транзисторов и затвором первого разрядного транзистора 7, сток второго входного транзистора 12 соединэн со стоками вторых усилительного 10 и установочного 14 транзисторов и затвором второго разрядног транзистора 8, истоки разрядных транзисторов 7 и 8 соединены с общей шиной 6 и истоками усилительных и ус- тановочных транзисторов 9-10 и 13-14 затворы входных и установочных транзисторов 11-14 соединены с адресным входом 5 устройства.

Усилитель работает следующим образом.

В статическом режиме на адресном входе 5 поддерживается напряжение логического нуля (логический 0). При

этом открыты установочные транзисто-55 считьшания. В„момент t4 на адресный ры 13-14, а остальные транзисторы 7 - вход 5 подается напряжение логичес- 12 закрыты, благодаря чему во внут- кой 1, а напряжения на разрядных вхо- ренинх узлах 15 и 16 установлены на- дах 1-4 устанавливаются до уровней пряжения логического 0. Сквозное прО логической 1, и устройство устанавтекание тока через устройство, а, следовательно, и потребление мощности, отсутствует.

Режим считывания информации поясняется с помощью временной диаграммы на фиг. 2. В начальный момент

пряжения на разрядных входах 1 и 2 в соответствии со считываемой инфор- мацией. Для определенности напряжение на втором разрядном входе 2 остается равным логической 1, а на первом входе 1 уменьшается по линейному закону

Vi(t)V - Vt,

(1)

0

0 5

0

v

V

t где V(t) - напряжение на первой разрядной шине 1; напряжение логической 1 , коэффициент, характеризующий скорость изменения напряжения на разрядной шине; время.

Когда разность напряжений на раз- 5 рядных входах 1 и 2 станет достаточной для того, чтобы скомпенсировать разбаланс плеч усилительной части устройства на транзисторах 9-12, вызванный разбросом параметров симмет- 0 ричньгх транзисторов (обозначим эту , разность напряжений, компенсирующую разбаланс плеч, через ), на адресный вход 5 подается напряжение логического О (момент времени tj). В результате закрываются установочные транзисторы 13 и 14 и открываются входные транзисторы 11 и 12. Поскольку усилительные транзисторы 9 и 10 в устройстве с перекрестной связью (положительной обратной связью), то в устройстве развивается регенеративный переходной процесс, в результате чего в узле 16 формируется высокий уровень напряжения, близкий логической 1, а в узле 15 - напряжение логического 0. Транзисторы 8-9 и 11-12 оказьшаются открытыми, а транзисторы 7, 10 и 13-14 - запертыми, в момент времени t начинается разряд емкости током разрядного транзистора 8. В момент времени t напряжение на разрядной шине 4 дос- тига.ет уровня V , по которому определяется быстродействие в режиме

31

ливается в состояние, соответствующее статическому режиму.

Ф о.р мула изобретения Усилитель для считывания информации из блоков памяти, содержащий первый и второй разрядные транзисторы , первый и второй усилительные транзисторы п-типа, причем стоки первого и второго разрядных транзисторов являются соответственно первым и вторым разрядными выходами усилителя, а истоки объединены, первый и второй усилительные транзис торы соединены по схеме с перекрест ной связью, отличающийся тем, что, с целью повьшения быстродействия усилителя, в него введены первый и второй входные транзисторы

83851 4

р-типа и первый и второй установочные транзисторы п-типа, причем истоки первого и второго входных транзисторов являются первым и вторым г разрядными входами усилителя соот- i ветственно, сток первого входного транзистора соединен со стоками первых усилительного и установочного транзисторов и затвором первого раз- 10 рядного транзистора, сток второго

входного транзистора соединен со стоками вторых усилительного и установочного транзисторов и затвором второго разрядного транзистора, истоки

15 разрядных транзисторов соединены с общей шиной и истоками усилительных и установочных транзисторов, затворы входных и установочных транзисторов являются адресным входом усилителя.

.f

г 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания на КМДП-транзисторах | 1983 |

|

SU1088065A1 |

| Устройство для считывания информации из блоков памяти | 1985 |

|

SU1280452A1 |

| Усилитель на кмдп-транзисторах | 1979 |

|

SU862236A1 |

| Усилитель считывания на кмдп-транзисторах | 1978 |

|

SU771716A1 |

| Усилитель для запоминающего устройства | 1981 |

|

SU999103A1 |

| Входной усилитель-формирователь с запоминанием информации | 1980 |

|

SU903970A1 |

| Усилитель записи-считывания на КМДП-транзисторах | 1988 |

|

SU1571673A1 |

| Усилитель считывания на КМДП транзисторах | 1984 |

|

SU1241285A1 |

| Усилитель записи-считывания для запоминающего устройства на дополняющих мдп-транзисторах | 1977 |

|

SU739643A1 |

| Усилитель-формирователь для оперативного запоминающего устройства на КМДП транзисторах | 1981 |

|

SU999104A1 |

Изобретение относится к вычислительной технике и может быть использовано в ЗУ на КМДП транзисторах для считывания информации. Цель изобретения - повышение быстродействия устройства. Устройство для считывания информации из блоков памяти содержит две входные шины, дне входные разрядные шины, адресный вход, общую шину, два разрядных транзистора п-ти- па, два усилительных транзистора п- типа, два входных транзистора р-типа, два установочных транзистора п- типа, причем стоки первого и второго разрядных транзисторов соединены с первой и второй входными разрядными шинами соответственно, а истоки объединены, первый и второй,усилительные транзисторы соединены по схеме с перекрестной связью, истоки первого и второго входных транзисторов соединены с первой и второй входными разрядными шинами соответственно сток первого входного транзистора соединен со стоками первых усилительного и установочного транзисторов и затвором первого разрядного транзистора, сток второго входного транзистора соединен со стоками вторых усилительного и установочного транзисторов и затвором второго разрядного транзистора, истоки разрядных транзисторов соединены с общей шиной и истоками усилительных и установочных транзисторов, затворы входных и установочных транзисторов соедине- ны с адресным входом устройства. 1 ил. О

| СПОСОБ ОЧИСТКИ СТОЧНЫХ ВОД И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2071948C1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Патент США Р 4272832, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-01-15—Публикация

1985-04-05—Подача