элементы , элемент ИЛИ-НЕ. 25, шифратор 3, На входы элемента РШИ-НЕ

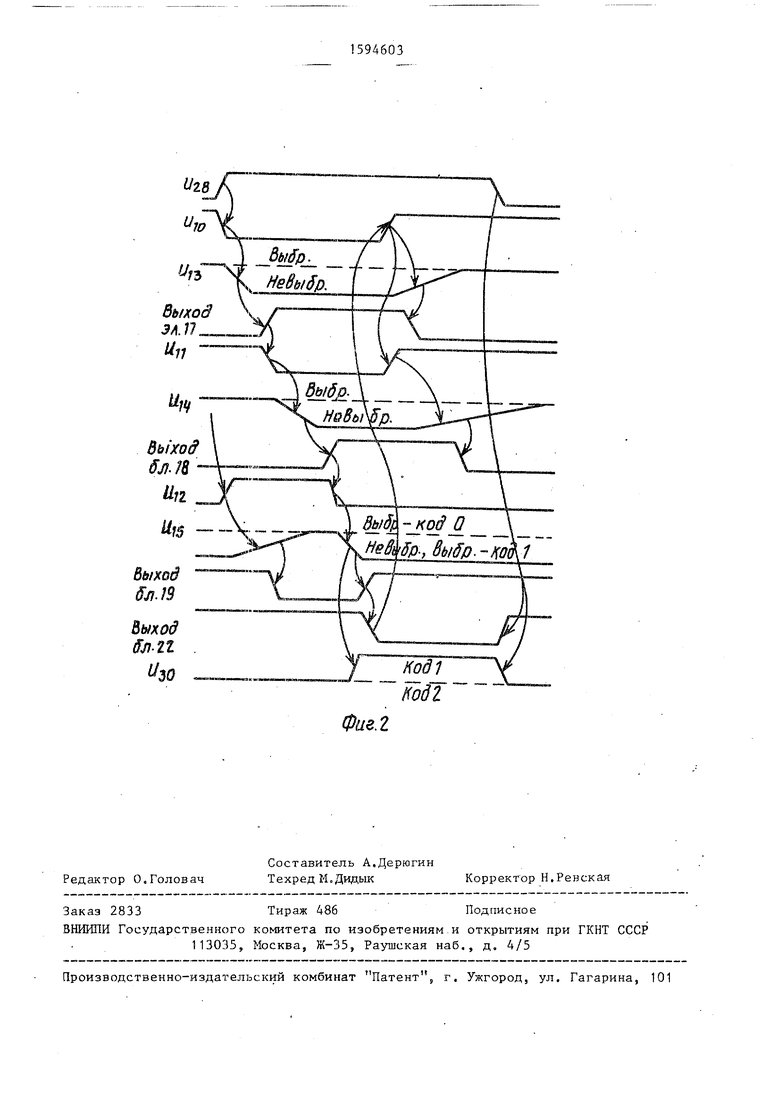

вый 26 и второй 27 инверторы,/вход 28 обращения к устройству, адресные входы 29, информационный выход 30, шину 31 нулевого потенциала и шину 32 питания. На фиг, 2

и

f.40

45

пок аз аны напряжения

/JJ на соответствующи;х айнах напряжения ,g, Ujj на выходах .соответствующих элементов и блоков напряжения , и зв на входе 28 обращения и выходе 30 устройства.

Устройство работает атедующим об- .разом,

При отсутствии обращения к ЗУ, а также после фиксации счит анной инфор- en йации в выходном блоке 16 осуществляется предзаряд адресных шин 13, шин 14 и 15 строк и столбцов через нагрузочные транзисторы 9 и 6, стоки кото- )5ых подключены к шине 32 питания, Фор- 1-дарователь 22 сигнала запрета работы устройства в активном режиме выполнен по схеме RS-триггера, 8--вход которого соединен с выходом второго блока раз55

25 поступают сигналы с выходов элемента 23 и блока 18 разрядных ключей который содержит эталонную шину 14 и элемент дешифратора (транзисторы 5 и 6), Элемент ИЛИ-НЕ 25 вырабатывает третий стробирующий сигнал (шина 12) .который активизирует работу накопителя 1 и второго дешифратора 4 путем подключения истоков транзисторов 2 и 4 к шине 31 нулевого потенциала, что создает условия для разряда выбранной шины 15 столбца накопителя через выбранный элемент памяти и невыбранных шин 15 столбцов через второй дешифратор 4,

Величина емкости шины 15 столбца накопителя зависит от кода информации, хранящейся в накопителе, поэтему блок 19 аналогично блоку 18 содержит эталонную шину 15 столбца с максимально возможным числом транзис то- ров 2, имитирующих элементы памяти, Кроме того, блок 19 содержит нагрузочный транзистор 6 и инвертор на

е шифратор 3, На входы элемента РШИ-НЕ

0

5

n

5

25 поступают сигналы с выходов элемента 23 и блока 18 разрядных ключей, который содержит эталонную шину 14 и элемент дешифратора (транзисторы 5 и и 6), Элемент ИЛИ-НЕ 25 вырабатывает третий стробирующий сигнал (шина 12), .который активизирует работу накопителя 1 и второго дешифратора 4 путем подключения истоков транзисторов 2 и 4 к шине 31 нулевого потенциала, что создает условия для разряда выбранной шины 15 столбца накопителя через выбранный элемент памяти и невыбранных шин 15 столбцов через второй дешифратор 4,

Величина емкости шины 15 столбца накопителя зависит от кода информации, хранящейся в накопителе, поэте- му блок 19 аналогично блоку 18 содержит эталонную шину 15 столбца с максимально возможным числом транзис то- ров 2, имитирующих элементы памяти, Кроме того, блок 19 содержит нагрузочный транзистор 6 и инвертор на

1

транзисторах 20 и 21. По окончании управляющего сигнала соответствующий блок (управляемый данным сигналом) Переводится в режим предзаряда. Выходной блок 16 хранит считанную информацию, пока на его вход сброса 4eiie3 инвертор 27 не поступит сигнал установки в исходное состояние (сигнал окончания обращения к ЗУ).

Использование изобретения в схемах TaKTHpyeNbix запоминающих устройств позволяет практически полностью исключить из времени выборки сост- тавляющие, обусловленные задержками в формирователях управляющих сигналов.

ормула изобретения

30

Постоянное запоминающее устройство, содержащее накопитель, первый и второй дешифраторы, выходг которых соединены соответственно с адресными и информационным входами накопителя первой и второй групп, прямой и инверсный входы адресных формирователей первой и второй групп соединены соответственно с информационными входами первого и второго дешифраторов, аин- формадионные входы являются адресными входами устройства, блок формирования выходного сигнала, информационные входы которого соединены с выходами второго дешифратора, а выход является информационным выходом устройства, первый элемент И-НЕ, входы ко- торого соединены с выходами одного

.

10

5

из адресных формирователей, первый , блок разрядных ключей, входы первой группы которого соединены с выхода- | ми другого адресного формирователя, а входы второй группы - с выходами второго дешифратора, второй блок разрядных ключей, входы которого соединены с выходами первого дешифратора, отличающееся тем, что, с целью повышения быстродействия и упрощения устройства, оно содержит второй и третий элементы И-НЕ, элементы ИЛИ-НЕ, два инвертора и формирователь сиг-лапа запрета, первый вход которого соединен с выходом второго блока разрядных ключей, второй вход - с входом сброса блока формирования выходного сигнала и выходом первого инвертора, вход которого является входом обращения к устройству, входы второго элемента И-НЕ соединены -соответственно с входом первого инвертора и выходом формирователя сигнала запрета, а выход .соединен со строби- рующими входами адресных формирователей, входом второго инвертора и первым входом элемента ИЛИ-НЕ, второй вход которого соединен с выходом пер- 0 вого блока разрядных ключей, а выход со стробирующими входами второго,дешифратора, накопителя и второго блока разрядных ключей, первый и второй входы третьего элемента И-НЕ соединены соответственно с выходом первого

5

5

элемента И-НЕ и второго инвертора, а выход соединен со cтpoбиpyющIiми входами первого дешифратора и первого блока разрядных ключей.

Игв

и

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1269209A1 |

| Оперативное запоминающее устройство | 1986 |

|

SU1483493A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Полупроводниковое запоминающее устройство | 1988 |

|

SU1674261A1 |

| Полупроводниковое запоминающее устройство с произвольной выборкой | 1984 |

|

SU1215135A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Полупроводниковое запоминающее устройство | 1984 |

|

SU1238157A1 |

| Оперативное запоминающее устройство | 1985 |

|

SU1283854A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1098035A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании запоминающих устройств с низким потреблением мощности в режиме хранения (тактируемых запоминающих устройств). Целью изобретения является повышение быстродействия и упрощение устройства благодаря введению в устройство схем формирования управляющих напряжений на элементах ИЛИ-НЕ 25, И-НЕ 23 и 24, инверторах 26,27 и формирователе 22 сигнала запрета. При этом сокращаются составляющие времени выборки, обусловленные задержками в формирователях управляющих сигналов, а также исключаются линейные элементы, трудно воспроизводимые в интегральном исполнении. 2 ил.

Фае.г

| Полупроводниковое запоминающее устройство | 1979 |

|

SU788176A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Полупроводниковое запоминающее устройство | 1981 |

|

SU1008791A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-09-23—Публикация

1988-07-22—Подача