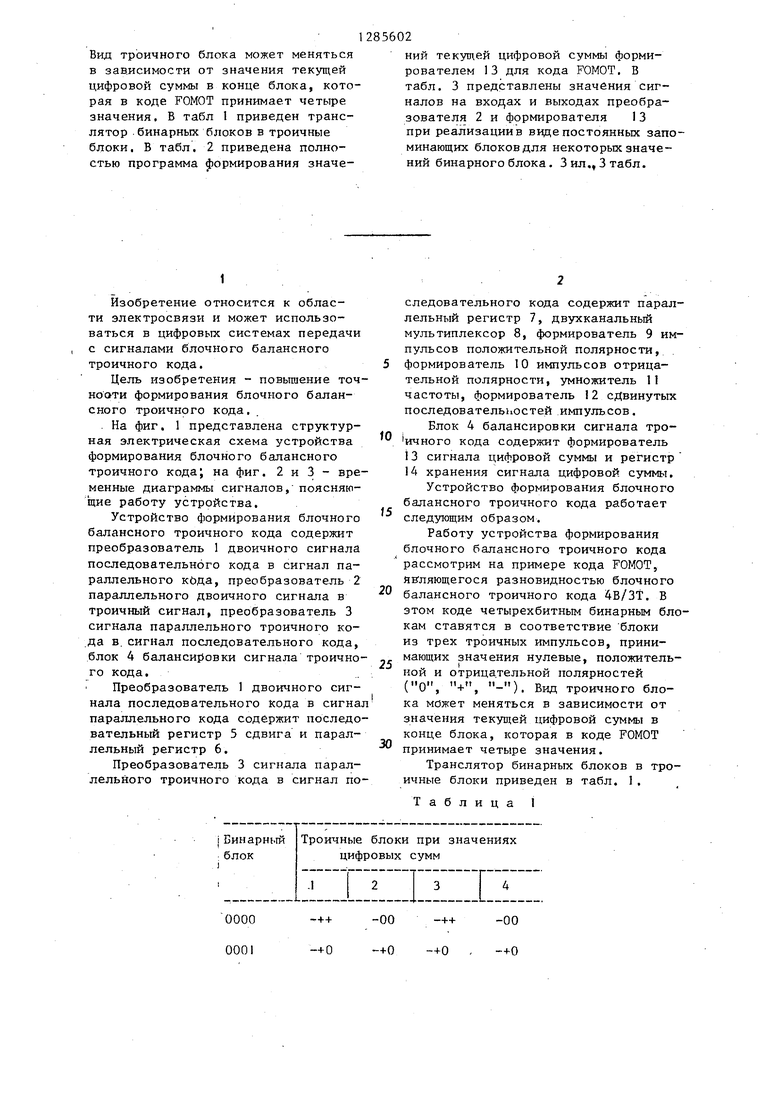

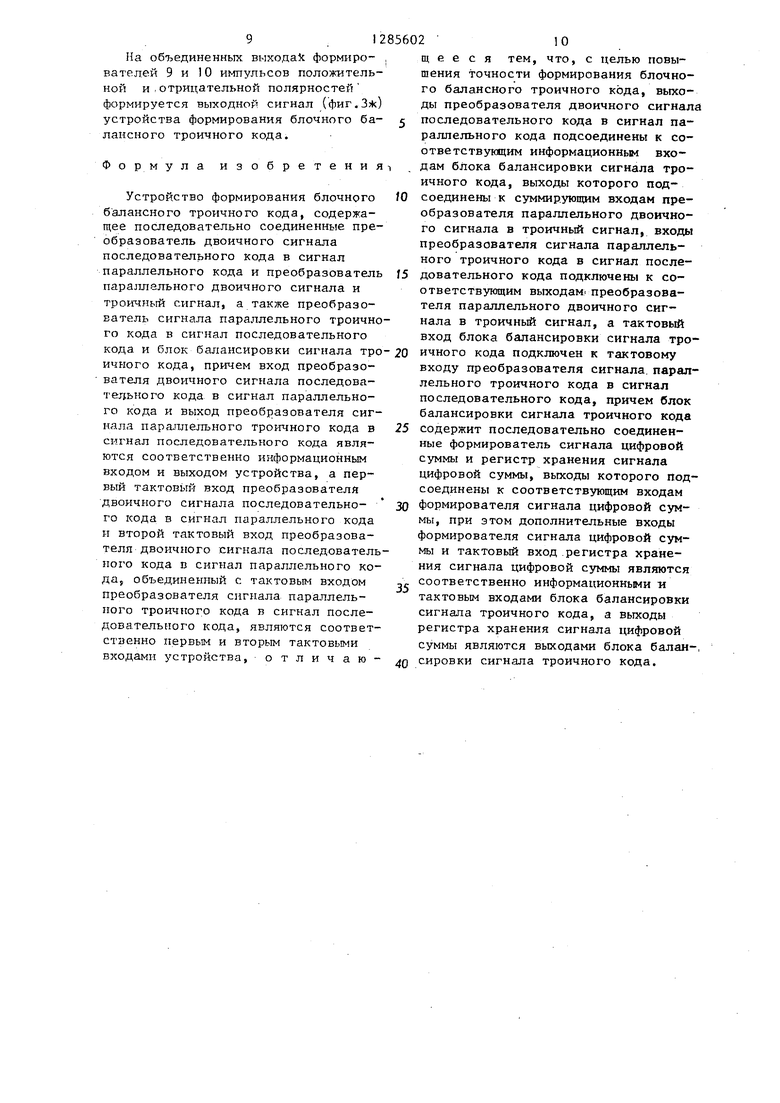

Вид троичного блока может меняться в зависимости от значения текущей цифровой суммы в конце блока, которая в коде FOMOT принимает четьтре значения, В табл 1 приведен транслятор .бинарных блоков в троичные блоки. В табл. 2 приведена полностью программа формирования значе1

Изобретение относится к области электросвязи и может использоваться в цифровых системах передачи с сигналами блочного балансного троичного кода.

Цель изобретения - повышение точ- нооти формирования блочного балансного троичного кода.

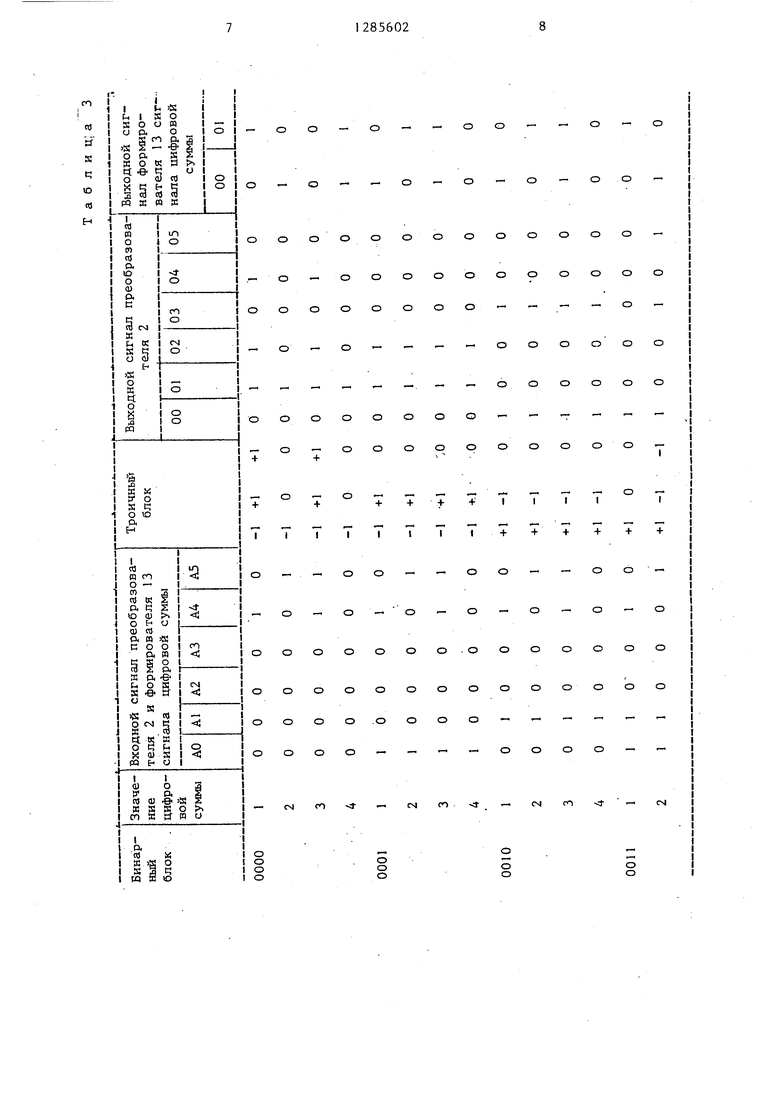

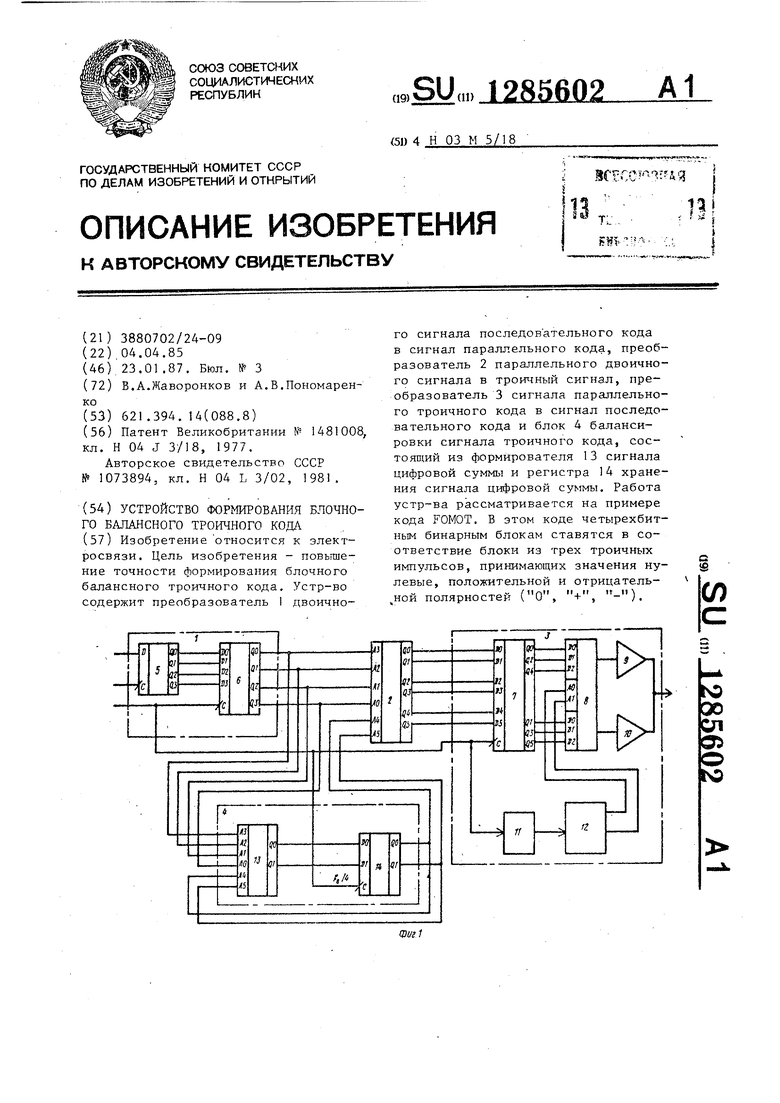

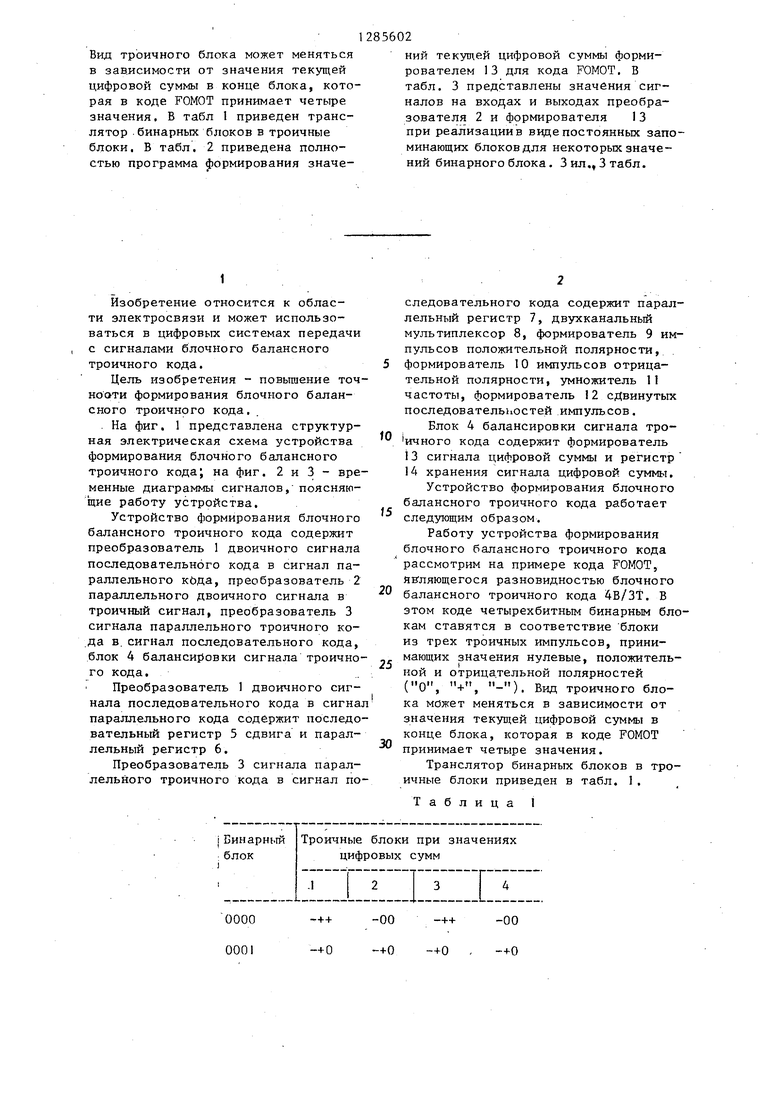

. На фиг. 1 представлена структурная электрическая схема устройства формирования блочного балансного троичного кода; на фиг. 2 и 3 - временные диаграммы сигналов, поясняющие работу устройства.

Устройство формирования блочного балансного троичного кода содержит преобразователь 1 двоичного сигнала последовательного кода в сигнал параллельного кьда, преобразователь 2 параллельного двоичного сигнала в троичный сигнал, преобразователь 3 сигнала параллельного троичного ко- .да в. сигнал последовательного кода, блок 4 балансировки сигнала троичного кода.

Преобразователь 1 двоичного сигнала последовательного кода в сигнал параллельного кода содержит последовательный регистр 5 сдвига и параллельный регистр 6.

Преобразователь 3 сигнала параллельного троичного кода в сигнал по1285602

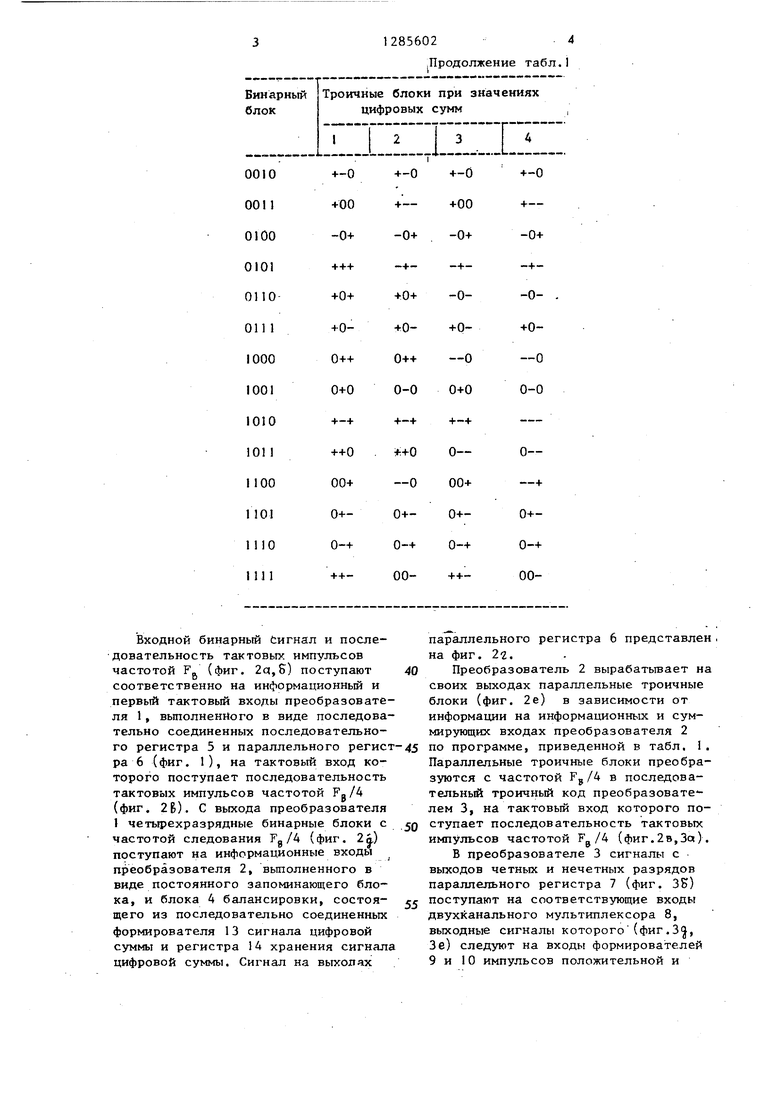

НИИ те куплей цифровой суммы формирователем 13 для кода FOMOT, В табл. 3 представлены значения сигналов на и выходах преобразователя 2 и формирователя 13 при реализации в вццепостоянных запоминающих блоков для некоторых значений бинарного блока. Зил., 3 табл.

5

0

5

0

следовательного кода содержит параллельный регистр 7, двухканальный мультиплексор 8, формирователь 9 импульсов положительной полярности, формирователь 10 импульсов отрицательной полярности, умножитель 11 частоты, формирователь 12 сдвинутых последовательностей импульсов.

Блок 4 балансировки сигнала тро- ичного кода содержит формирователь

13сигнала цифровой суммы и регистр

14хранения сигнала цифровой суммы. Устройство формирования блочного

балансного троичного кода работает следующим образом.

Работу устройства формирования блочного балансного троичного кода рассмотрим на примере кода FOMOT, яв ляющегося разновидностью блочного балансного троичного кода 4В/ЗТ. В этом коде четырехбитным бинарным блокам ставятся в соответствие блоки из трех троичных импульсов, принимающих значения нулевые, положительной и отрицательной полярностей (О, +, -). Вид троичного блока может меняться в зависимости от значения текуп1ей цифровой суммы в конце блока, которая в коде FOMOT принимает четыре значения.

Транслятор бинарных блоков в троичные блоки приведен в табл. 1.

Таблиц

Входной бинарный Сигнал и после- довательность тактовых, импульсов частотой Fg (фиг. 2а,б) поступают соответственно на информационный и первый тактовый входы преобразователя 1, выполненного в виде последовательно соединенных последовательного регистра 5 и параллельного регист ра 6 (фиг. 1), на тактовый вход которого поступает последовательность тактовых импульсов частотой Fg/4 (фиг, 2В). С выхода преобразователя 1 четьфехразрядные бинарные блоки с частотой следования Fg/А (фиг. 2п.) поступают на информационные входы преобразователя 2, выполненного в виде постоянного запоминающего блока, и блока 4 балансировки, состоящего из последовательно соединенных формирователя 13 сигнала цифровой суммы и регистра 14 хранения сигнала цифровой суммы. Сигнал на выходах

12856024

.Продолжение табл.1

40

45

50

55

параллельного регистра 6 представлен на фиг. 22.

Преобразователь 2 вырабатывает на своих выходах параллельные троичные блоки (фиг. 2е) в зависимости от информации на информационных и суммирующих входах преобразователя 2 по программе, приведенной в табл. 1. Параллельные троичные блоки преобразуются с частотой FJ/4 в последовательный троичный код преобразователем 3, на тактовый вход которого поступает последовательность тактовых импульсов частотой (фиг.2в,За).

В преобразователе 3 сигналы с выходов четных и нечетных разрядов параллельного регистра 7 (фиг. 3S) поступают на соответствующие входы двухканального мультиплексора 8, выходные сигналы которого (фиг .31, Зе) следуют на входы формирователей 9 и 10 импульсов положительной и

отрицательной полярностей. Последо- вате.льность тактовых импульсов часттой Fg/A после умножения на три в умножителе 11 частоты (фиг. Зв) поступает на вход формирователя 12, вырабатывающего две сдвинутые последовательности импульсов (фиг. Зг), подаваемые на управляющие входы двухканального мультиплексора 8.

В блоке 4 балансировки, выполненном в виде последовательно соединенных формирователя 13 сигнала цифровой суммы (постоянного запоминающего блока) и регистра 14 хранения сигнала цифровой суммы, содержатся значения текущей цифровой суммы в зависимости от вида передаваемого в канал.связи (на выход устройства формирования блочного балансного троичного кода) троичного блока и цифровой суммы, при которой он формируется. Так, если на вход блока 4 балансировки поступает бинарный блок 1000 при значении цифровой суммы 3, то преобразователь 2 в соответствии с табл. 1 выдает троичный блок вида - - О. При этом блок 4 балансировки (формирователь 13 сигнала цифровой суммы) вырабатывает новое значение цифровой суммы, равное 1, сигнал которой является исходным для кодирования следующего троичного блока текущей цифровой суммы. Новое значение.цифровой суммы переписывается с формирователя 13 сигнала цифровой суммы в регистр 14 хранения сигнала цифровой суммы по- сле занесения сформированного троичного блока в преобразователь 3.

Полностью программа формирования значений текущей цифровой суммы формирователем 13 сигнала цифровой суммы для кода FOMOT приведена в табл. 2.

В табл. 3 представлены значения сигналов на входах (АО, А1, А2, A3, А4, А5) и выходах (QO, Q1 , Q2, 0,3, Q4, Q5) преобразователя 2 и значения сигналов на входах (АО, А1, А2, A3, А4, А5) и выходах (QO,,Ql) формирователя 13 сигнала цифровой суммы при их реализации в виде постоянных запоминающих блоков для некоторых, значе,ний бинарного блока.

r

i

« я s R

Ю

n)

H

На объединенных выхода5с формиро- , вателей 9 и 10 импульсов положительной и,отрицательной полярностей формируется выходной сигнал (фиг.З) устройства формирования блочного балансного троичного кода.

Формула изобретения

Устройство формирования блочного балансного троичного кода, содержащее последовательно соединенные преобразователь двоичного сигнала последовательного кода в сигнал параллельного кода и преобразователь параллельного двоичного сигнала и троичный сигнал, а также преобразователь сигнала параллельного троичного кода в сигнал последовательного кода и блок балансировки сигнала тро ичного кода, причем вход преобразователя двоичного сигнала последовательного кода в сигнал параллельного кода и выход преобразователя сигнала парштельного троичного кода в сигнал последовательного кода являются соответственно информационным входом и выходом устройства, а первый тактовый вход преобразователя двоичного сигнала последовательного кода в сигнал параллельного кода и второй тактовый вход преобразователя двоичного сигнала последовательного кода в сигнал параллельного кода, объединенный с тактовым входом преобразователя сигнала параллельного троичного кода в сигнал последовательного кода, являются соответственно первым и вторым тактовыми входами устройства, отличаю-

10

f5

-20

8560210

щ е е с я тем, что, с целью повышения точности формирования блочного балансного троичного кода, выходы преобразователя двоичного сигнала последовательного кода в сигнал параллельного кода подсоединены к соответствующим информационньм входам блока балансировки сигнала троичного кода, выходы которого подсоединены к суммирующим входам преобразователя параллельного двоичного сигнала в троичньА сигнал, входы преобразователя сигнала параллельного троичного кода в сигнал последовательного кода подключены к соответствующим выходам преобразователя параллельного двоичного сигнала в троичный сигнал, а тактовый вход блока балансировки сигнала троичного кода подключен к тактовому входу преобразователя сигнала, параллельного троичного кода в сигнал последовательного кода, причем блок балансировки сигнала троичного кода содержит последовательно соединенные формирователь сигнала цифровой суммы и регистр хранения сигнала цифровой суммы, выходы которого подсоединены к соответствующим входам формирователя сигнала цифровой суммы, при этом дополнительные входы формирователя сигнала цифровой суммы и тактовьй вход .регистра хранения сигнала цифровой суммы являются соответственно информационными и тактовым входами блока балансировки сигнала троичного кода, а выходы регистра хранения сигнала цифровой суммы являются выходами блока балан-, сировки сигнала троичного кода.

25

30

35

V ,1. S .. 8

JuulruгJlrulлллJШЛяrшллJuгJШЛллллляпллnл.

s.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоичной последовательности в блочный балансный троичный код | 1986 |

|

SU1324115A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА ВО МНОГОЗНАЧНЫЙ КОД (ВАРИАНТЫ) | 1997 |

|

RU2109400C1 |

| Преобразователь последовательного кода в параллельный | 1989 |

|

SU1795557A1 |

| Декодер балансного кода | 1990 |

|

SU1795556A1 |

| Устройство для преобразования двоичной последовательности в балансный троичный код | 1991 |

|

SU1807561A1 |

| Преобразователь двоичного кода в трехпозиционный код | 1984 |

|

SU1317675A1 |

| Устройство для формирования балансного троичного кода | 1983 |

|

SU1184104A1 |

| Кодер балансного кода 3B2Q | 1987 |

|

SU1531223A1 |

| Преобразователь двоичного кода в трехпозиционный код | 1989 |

|

SU1633499A1 |

| Устройство для индикации экстремального значения последовательности цифровых величин | 1988 |

|

SU1529461A1 |

Изобретение относится к электросвязи. Цель изобретения - повьоте- ние точности формирования блочного балансного троичного кода. Устр-во содержит преобразователь 1 двоичного сигнала последовательного кода в сигнал параллельного кода, преобразователь 2 параллельного двоичного сигнала в троичный сигнал, преобразователь 3 сигнала параллельного троичного кода в сигнал последовательного кода и блок 4 балансировки сигнала троичного кода, сос- тояпдай из формирователя 13 сигнала цифровой суммы и регистра 14 хранения сигнала цифровой суммы. Работа устр-ва рассматривается на примере кода FOMOT. В этом коде четырехбитным бинарным блокам ставятся в соответствие блоки из трех троичных импульсов, принимающих значения нулевые, положительной и отрицатель- .ной полярностей (О, +, -). i СЛ

f nnjuu}jnj rmju suu r jm

Редактор H.Тупица

Составитель В.Орлов Техред Л.Олейник

Заказ 7535/57 Тираж 899Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

Корректор М.Максимишинец

| Способ сварки давлением с подогревом | 1987 |

|

SU1481008A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство формирования блочного балансного троичного кода | 1981 |

|

SU1073894A1 |

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-01-23—Публикация

1985-04-04—Подача