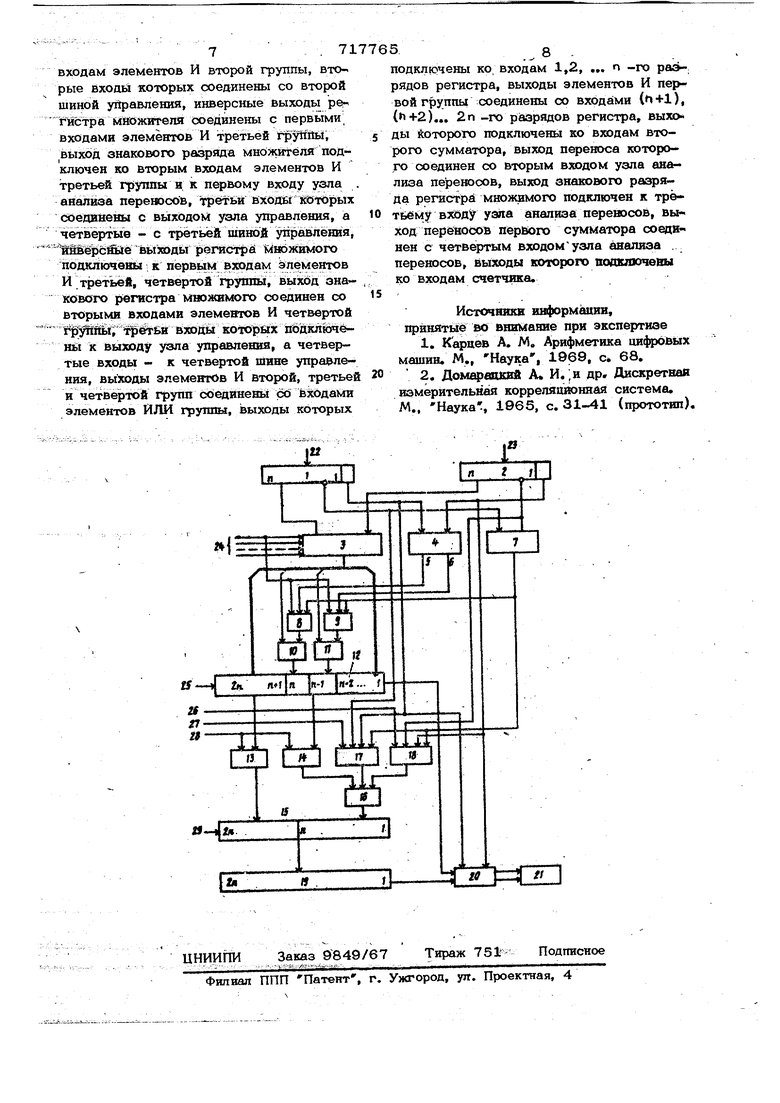

Изобретение относится к области &ъ томйтики и вычислительной техники и может быть использовано в корр© ляторах и цифровых фильтрах. Известно устройство для умнюжения чисел непосредственно в дополнительном коде, причем умножение производится так же, квза в прямом (получение псевдопроизведения ъа. накашшвакмцем сумматоре), с последующей корре ляцией псевдопроизведения (сложение псевдопроизведения с дополнением отрицательного сомиюжителя) М . Однако это устройство сложно. Наиболее близким по технической сущности к предложенному является устройство для вьрсисления суммы произведе1шй, содержащее о -разрядный регистр множимого, п -разрядный регистр множителя, узел сдвига, узел кявлтлза, узел управления, сумматоры, регистр, элементы И, ИЛИ, группы элементов И, группу элементов ИЛИ,узел ananyi3&. переноса, счет чик, причем прямые выходы регистра MHOжимого соединены с первой группой вхо дов уолв. сдвига, соответствующие выходы которого соединены со BKOD.UMVL первого сумматора и первыми входами первого и второго элементов ИЛИ. Инверсные выходы регистра мвожимого подключены к первому входу узла управления. Выход знаксвого разряда регистра мнохснмого соединен с первым входом узла еашяои аа Прямые выходы регистра множителя подключены ко второй группе входов уопй сдвига. Инверсные выходы регистра множителя соединены со вторым входом узпа управления. Выход знакового разряда регистра множителя подключен ко второму входу узпа акахиаа, первый выход которого соединен с первым входом первого элемента И, а второй выход узпа анализа подключен к первому входу второго зпсыета И, Вторые входы первого и второго элементов И соединены с первой шиной управления, а их третьи входы - с выходом узаа управления. Выходы первого и второго элементов И подключены ко .;:;. „,.,;;,;..,,;,.,. ,i..,,,;;;r:...,.7i вторым входам первого и вторргоэлемен-. трв ИЛИ схютветственно, выходы-первого и второго элементов ИЛИ соединены со входами л-го и (п-1)г6 разрядов первого сумматора t2l , Однако это устройство имеет низков быстродействие, так как в нём проиэво- дится предварительно перевод в прямой код затем вьшолняется умножение, а для дальнейшей обработки - обратный перевод, Цель изобретения - повышение быстродействия, .,.,.. --г .: . Это достигается тем, что в устройстве выходы 2п , {2п-1),.,.(г| +1)-го разря:Дов первого сумматора соединены с пёрвьИ ми 1входами Элементов И первой группь, вторые входы кЬторШ пЖвяШеньГ рой шине управления. Выходы,п ,(п-1),,. 1-4ч разрядов сумматора подключены к первым входам элементов И второй rpyiiпы, вторые &ходы которых сЪёдйНёШ со второй шиной управления, Инверсвше выходы регистра Множит епя соединены с первыми входами элементов И третьей группы. Выход Знакового разрзда множи г й1 пОдключен ко вторёгм вхО)цам элементов И Третьей группы , и к первому вхо-. ду узла анализа перешсов, третьи входы которых соединены с выходом узла уп рЖвлеяия а четвёртые - с третьей шиной управления. Инверсные выходы регистра мнЬжимохЧэ подключены к первым входам элементов И четвертой группы. Выход 1зйш:оел1х регистфа мнояшкю со вторыми входами элементов И четвертой группы, третьи вйторых подключены к выходу узла управления, а четsepTbie входы - к четвертой шине управления. Выходы элементов И второй, тре- i тьей и четеертой групп соедннеяь оо вхо-; дами элементов ИЛИ группы, выходы ко торых подключены ко входам 1,2,,..п-го разрядов регистра. Выходы элементов И первой ттруппы соединены со Входами (пч-i), {n-t-2),.,,, 2 п-го разрядов регистра, выходы которого подключень ко входам второго сумматора, вьгхЬд Ъередаса соединен€е ёторь1й вХоа узла анализа переносов. Выход iJiSSp l рёгЙст г1йШ%йШШ ПбШйшбн JK TjpeTeeKty ВХОДУ узла анализа переноррв, riepeHOcOBi Шрвб1 5 дйнёя с четвертым входом узла анализа переносов, выходы тюдключевы ко входам счетчика. Функциональная схема устройствга приведена на чертеже. ,4 Устройство содержит п-разрядный рё рдстр мйожимогс 1,п -разрядный регистр множителя 2, узел сдвига 3, представляющий собой комбинашюиную схему и ocyw ествляющий смещение кода множимого на один разряд в каждом такте. Выходы знаковых разрядов регистров 1 и 2 подключень ко входам узла анализа 4, выдающего уровень логической единицы на выходе 5, если сомножители разного знака, и на выходе 6 - если оба еомножите ла отрицат-ельйме, узел управлений 7, aia выходе которого вырабатывается запре щающий уровень логического нуля, если хотя быЪдин из сомножителей равен нулю, элементы И 8 и 9, элементы ИЛИ 1О и II, сумматор 12, группу элемен-й элемент И 14, регистр 15, элемент ИЛИ 16, элементы И 17 и 18, сумматор 19, узел анализа переносов 2О, счетчик 21, входньсе шины 22-29, Устройство работает следующим образом. В каждом i -ом цикле работы очередные сомдамэдтели находятся на регистре 1 и 2. По сигналу по шине 28 содержимое сумматора 12 через группу элементов И 13, элемент И 14 и элемент ИЛИ 16 занскзитсяна регастр 15, и в сумматоре 19 осуществляется сложение ранее накопленной суммы с псевдойроизведениек вычисленным в предьщущем цикле работы. При этом перенос в сумматоре 19 распространяется на 2 h разрядов. Сйгналрм по шине 25 сбрасывается сумматор 12, По сигналу на первой из шин 24 с выходов узла сдвига,3 в Г) младших разрядов сумматора 12 поступает Мйожнмое, если младший разряд множителя равен 1 и нули, равен О. По этому же сигналу с выхода 5 узла анадиза 4 через элемент И 8 и элемент ИЛИ Ю ааносИтся единица в п -ый разряд сумматора 12, если сомножители рабного Эйака, или заносится единица в (1-1) разряд с выхода 6 - при отрицательных со множителя зс. Тем самым выполняется часть коррекции псевдопроизведений, Зайесение единицы в п -ый или (П-1)-ый разряд запрещается уровнем rtOfK4ecK6tx) нуля с выхода узла управ ления 7, если хотя бы один из сомножителей равен О, По сигналу на второй из шин 24 мйржимое со сдвигом на один вправо поступает на входы сумматора 12, если (п -1)-ый разряд множвтепя равен 1 и т.д. При каждом очередном сйсШёШй Сдвииутйго множимого с содержанием сумматора 12 перенос распространяется не болеечем нап разрядов, что и определяет длительность такта получения псевдопроизведения. До момента окончания второго такта получения псевдопроизведения на сумматоре 12 заканчивается распространение переноса в сумматоре 19, первым сигналом по шине 29 сбрасывается регистр 15, и по сигаалу на шине 26 в п старших разрядов регистра 15 через элементы И 18 и элемент ИЛИ 16 заносится инверсный код множителя, если множитель отрицдтольный и ни один из сомножителей не равен нулю, т.е. на сумматоре 15 вьтолняется первая коррекция псевдопроизведения, формируемого на сумматоре 12, Вторым сигналом по шине 29 сбрасьшается в нуль регистр 15, а сигналом по шине 27 в его п старших разрядов заносится код с инверсных выходов регистра 1, если множимое отрицательно и ни один из сомножителей не равен нулю, т.е осуществляется вторая коррекция псевдопроизведения, форкшруеьдаго на сумматоре 12. При выполнении корречик: ; перенос в сумматоре 19 расгфостраняется не более чем на л разрадсж, т.е. такт ксррвкцнв по времени равен такту получения псевдопроизведения, что к позволяет совместить вьшолнение этих операций. По . окончании, второй коррекции регистр 15 сбрасывается третьим сигналом по щине 29. К моменту окончакаа ва Юоследней шине 24 на су лматоре 12 сф ч мёруется псевдопроизведение, ко|фекй:иа которого была выполнека на сумматоре: 19. По сигналу на шике 28 содержимое сумматора 12 записывается на регистр 15, и в сумматоре 19 начинается сп зж&кше псевдопроизведения сомноЗ Ш №пей С ранее вакопненной суммой. Сумматсф 12 сбрасывается, цикл работы повторяется сначала для очередных С И)-ых СОМ1И жителей. В каждом цикле работы переносы из старших разрядов сумматоров 12 н 19 поступают в схему анализа переносов 20. В течение цикла могут поступать О, 1 или 2 переноса. Схема перШа чи переноса управляется знаковыми разрядами регистров 1 и 2 и вьфабатывает сигналы сложения или вьгчитания в счет-чик 21. В результате вьтолнения т циклов работы на сумматоре 19 и счетчике 21 сформируются в дополнительном коде значения суммы произведений, знак которой определяется старшим разрядом счет усреднения. Таким образом при получении суммы произведений чисел, представленных в дополнительном коде быстродействие устройства, которое задает допустимую частоту подачи сомножителей, определяется лишь временем формирования псевдопроизведения, операции коррекции псевдопроизведения и суммирование произведений не отражаются на общем быстродействии устройства. Формула и 3 о б .р е т е и и я Устройство для вычисления суммы произведевий, содержащее п -разрядный .рем гистр МНОЖИМОГО, п -разрядный регистр множителя, узел сдвига, узел анализа, узел управления, сумматоры, регистр, элементы И, ИЛИ, гр5ппы элеме1ггов И, группу элементов ИЛИ узел ааализа п реноса, счетчик, причем прямые выходы регистра множимого соединения с первой группой входов узла сдвига, соответствующие выходы которого соединены со входами первого сумматора и первыми взоодами левого и второго элементов ИЛИ, инверсшле выходы регистра множимого подключены к первому входу узла управленкя, выход знакового разряда регистра MHOJtaiworo соединен с первыми входом узла анализа, прямые выходы регистра множителя подключены ко второй группе входов узла сдвига, инверсныевыходы регистра множителя соединены со вторым взводом узла управления, выход знакового разряда регистра множителя подключен ко Второму входу узла анализа, первый выход которого сюединен с первым входом первого элемента И, а второй выход уэла анализа подключен к первому входу второго элемента И, вторые входы первого и B7,t)poin элементов И соединены с первой щкной управления, а их третьи входы - с выходом узла управления, выходы первого и Второго элементов И подключены ко вторым входам первого и второго элементов ИЛИ соответственно, выходы первого и второго элементов ИЛИ соединены со входами п -го и (n-l)-ro разрядов nepJEsoro сумматора, отличающееся тем, что, с целью повышения быстродействия, в нем выходы 2п ,(2n1),... (п-J-D-ro разрядов первого сумматора соединены с первыми входами элементов И первой группы, вторые входы которых подключены ко второй шине управления, выходы п , ()..Д-го раз-, рядов сумматора подключены к первым

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1976 |

|

SU703804A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для умножения последовательных двоичных кодов | 1987 |

|

SU1495786A1 |

| Устройство для умножения п-разрядных двоичных чисел | 1974 |

|

SU575651A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Вычислительная ячейка | 1985 |

|

SU1287145A1 |

| Множительное устройство | 1981 |

|

SU1024909A1 |

Авторы

Даты

1980-02-25—Публикация

1973-07-04—Подача