Изобретение относится к вычислительной технике и автоматике и может быть использовано при построении уп- равляющих автоматов микропрограммных процессоров.

Цель изобретения - сокращение ап паратных затрат.

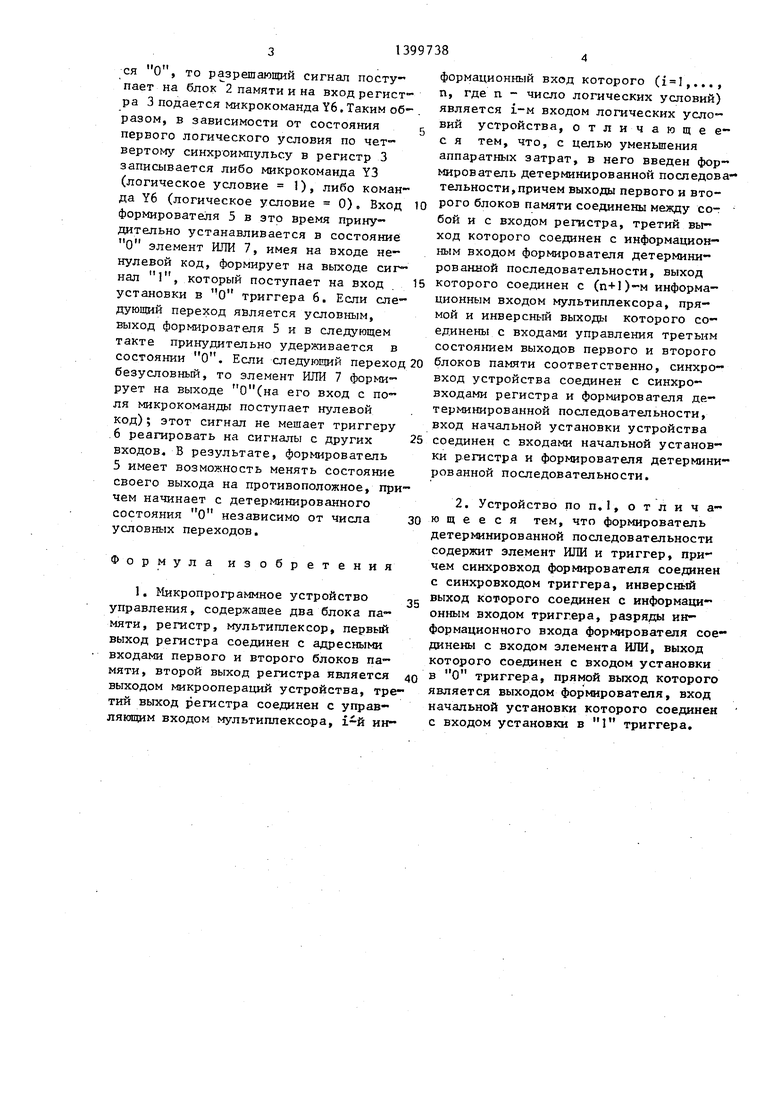

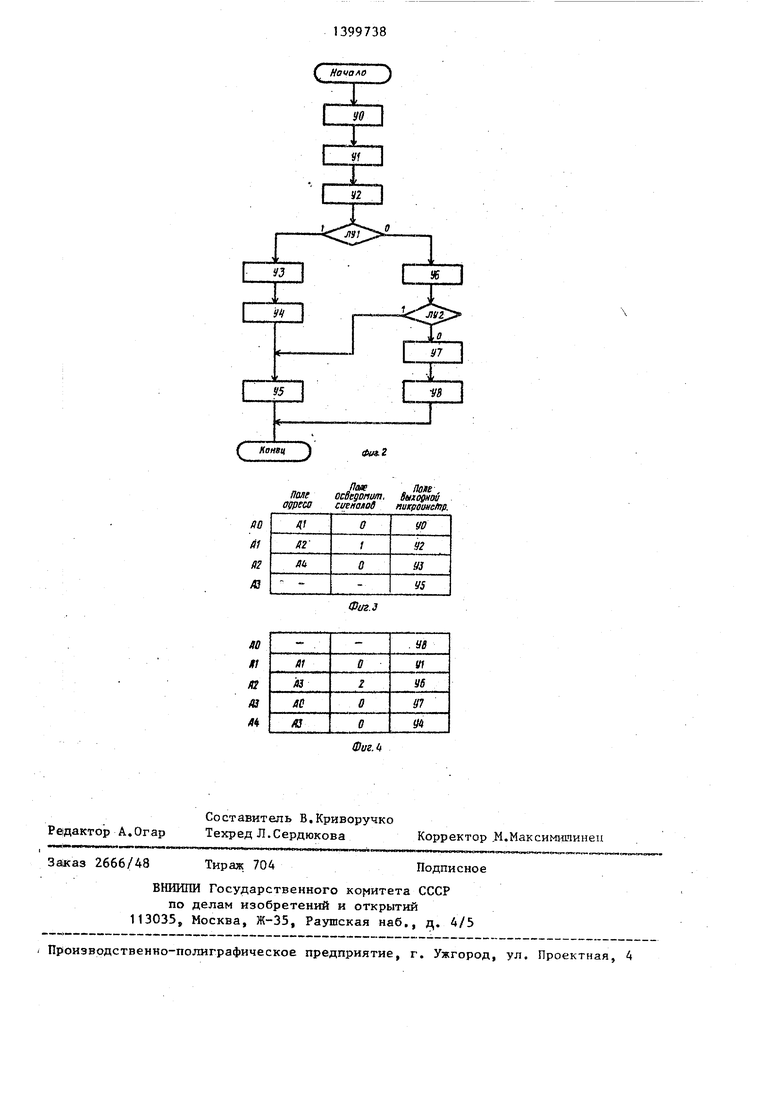

На фиг,1 приведена функциональрая схема устройства; на фиг„2 пример граф схе№1 программы; на фиг.З и 4 °- ;пример размещения микрокоманд этой |программы соответственно в первом и ;втором блоках памяти.

: Микропрограммное устройство уп равления содержит (фиг.1) блоки 1 и 2 |памяти, регистр 3 мультиплексор Aj :формирователь 5 детерминированной :поспедоватё.пьности, включающий триг |гер 6 и элемент ИЛИ 7, Устройство

имеет синхровход 8, вход 9 начальной установки, входы 10 логических уело™ вий и выход 1 1 микроопераций, Работа устройства начинается с установки в начальное состояние, R Начальном состоянии регистр 3 обнулен, триггер 6 установлен в единичное состояние сигналом с входа 9. Нулевой код постз пает на адресные, входы бло™ ков 1 и 2 памяти, на управляювдй вход мультиплексора 4, на (п.+ 1)-й информа 1ционный вход мультиплексора 4 посту- пает сигнал 1. На прямом выходе fsrльтиплeкcopa 4 находится сигнал 1 который открывает выходы блока 1 памя- ги.В результате в исходном состоянии яа входе регистра 3 находится микроко-™ манда из нулевой ячейки блока I памяти; рто. первая 1 1икрокоманда программы.

Рассмотрим такты работы устройст Ьа с безусловными переходами Поле Кода признаков микрокоманды кодируется нулевым кодом кодом пропуска информации с (п+1)-го входа элемента ИЛИ 7. В результате на выходе элемен™ Тй ИЛИ 7 находится О, В поле адре- ta микрокоманды записывается адрес Следующей микрокоманды; пусть он ра-- йен, например А1. Следовательно, Иолный код первой микрокоманды ра йен А1, О, YO; она хранится по адре- йу АО блока 1 памяти (фиГе2 4), Пер йым синхроимпульсом с входа 8 уст- poftctaa первая микрокоманда YO занО 0ИТСЯ в регистр 3. Одновременно триг jfep 6 устанавливается в состояние . В блоках 1 и 2 памяти начинается выборка информации по адресу А1; йигнал О с (п+1)-го входа мультит;

гшексора 4 поступает на его инверсный вЬ1ход Б виде 1 и открывает выходы -блока 2 памяти Таким образом, на входе регистра 3 к началу второго такта находится микрокоманда из блока 2 памяти из ячейки А1 (это вторая микрокоманда У1 программ :, фиг,2-4). С приходом второго синхроимпульса эта микрокоманда заносится в регистр 3, триггер 6 устанавливается в едини ное состояние; начинается такт. Переход от YI к Y2 также безусловный Пусть адрес третьей микрокоманды Y2 равен AI, Тогда полный код второй ми рокоманды равен А1, 0. YI; он хранится по адресу А1 в блоке 2 памяти (фиг.). Так как триггер 6 находится в состоянии 1, то в начале трет его такта в 3 записывается микрокоманда Y2 из блока I памяти. Отсюда сле,пует, что при реализации линейной части программы микрокоманды поочередно И 1бирается из первого и второго блоков памяти, что обеспе- чивает их равномерную загрузку.

Рассмотрим такт с условным перех дом (переход от Y2 к Y3 или Y6). В этом случае-в поле кода признаков записывается номер логического усло ВИЯ, по которому будет проводиться переход. Микрокоманды Y3 и Y6 раз мещаются по одному адресу в разных блоках памяти. Пусть, например, переход осуществляется по логическому условию номер один, микрокоманды Y3 и Y6 располагаются по адресу А2 в первом и втором блоках памяти соот- ветственно.. Тогда полный код микрокоманды Y2, содержащей команду условного перехода, равен А2, 1, Y2 (фиг.2-4). Код Этой микрокоманды заносится в регистр 3 в начале третьего такта. Код поля адреса микрокоманды (А2) поступает на адресные входы блоков 1 и 2 памяти, в которых начинается- выборка информации соответственно микрокоманд Y3 и Y6. Код поля признаков микрокоманды поступает на управляющий вход мультиплексора 4. В результате на прямом выход мультиплексора 4 появляется состояние, равное состоянию на первом вхо- .де 10 логических условий. Если на этом входе находится 1, то разрешающий сигнал 1 поступает на блок } памяти и на вход регистра 3 пода- ,ется 1 1икрокоманда Y3; если на первом входе 10 логических условий находится О, то разрешающий сигнал посту пает на блок 2 памяти и на вход регистра 3 подается микрокоманда Y6. Таким об- . разом, в зависимости от состоянияг

первого логического условия по четвертому синхроимпульсу в регистр 3 записывается либо микрокоманда Y3 (логическое условие 1), либо команда Y6 (логическое условие 0). Вход Ш формирователя 5 в это время принудительно устанавливается в состояние О элемент ИЛИ 7, имея на входе ненулевой код, формирует на выходе сигнал 1, который поступает на вход 15 установки в О триггера 6. Если следующий переход является условным, выход формирователя 5 и в следующем такте принудительно удерживается в

формационный вход которого (,,.., п, где п. - число логических условий) является i-M входом логических условий устройства, отличающее- с я тем, что, с целью уменьшения аппаратных затрат, в него введен формирователь детерминированной последовательности, причем выходы первого и второго блоков памяти соединены между со- бой и с входом регистра, третий выход которого соединен с информационным входом формирователя детерминированной последовательности, выход которого соединен с (п+1)-м информационным входом мультиплексора, прямой и инверсный выходы которого соединены с входами управления третьим состоянием выходов первого и второго

состоянии О. Если следующий переход 20 блоков памяти соответственно, синхровход устройства соединен с синхро- входами регистра и формирователя детерминированной последовательности, вход начальной установки устройства 25 соединен с входами начальной установки регистра и формирователя детерминированной последовательности.

2. Устройство по п,1, о т л и ч а- 30 ю щ е е с я тем, что формирователь детерминированной последовательности содержит элемент ИЛИ и триггер, причем синхровход формирователя соединен с синхровходом триггера, инверсный выход которого соединен с информационным входом триггера, разряды информационного входа формирователя соединены с входом элемента ИЛИ, выход которого соединен с входом установки 40 в О триггера, прямой выход которого является выходом формирователя, вход начальной установки которого соединен с входом установки в 1 триггера.

безусловный, то элемент ИЖ 7 форьт- рует на выходе О(на его вход с поля микрокоманды поступает нулевой код); этот сигнал не мешает триггеру 6 реагировать на сигналы с других входов, В результате, формирователь 5 имеет возможность менять состояние своего выхода на противоположное, при- чем начинает с детерминированного состояния О независимо от числа условных переходов.

Формула изобретения

. Микропрограммное устройство управления, содержашее два блока памяти, регистр, мультиплексор, первый выход регистра соединен с адресными входами первого и второго блоков памяти, второй выход регистра является выходом микроопераций устройства, третий выход регистра соединен с управляющим входом мультиплексора, i-й ин35

формационный вход которого (,,.., п, где п. - число логических условий) является i-M входом логических условий устройства, отличающее- с я тем, что, с целью уменьшения аппаратных затрат, в него введен формирователь детерминированной последовательности, причем выходы первого и второго блоков памяти соединены между со- бой и с входом регистра, третий выход которого соединен с информационным входом формирователя детерминированной последовательности, выход которого соединен с (п+1)-м информационным входом мультиплексора, прямой и инверсный выходы которого соединены с входами управления третьим состоянием выходов первого и второго

30 40

35

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Микропрограммное устройство управления | 1990 |

|

SU1705825A2 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Устройство для отладки программ | 1988 |

|

SU1661771A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1619347A1 |

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

Изобретение относится к вычислительной технике и автоматике и может использоваться при построении управляющих автоматов микропрограммных микропроцессоров. Цель изобретения - сокращение аппаратных затрат. В состав устройства входят блоки I и 2 памяти, регистр 3, мультиплексор 4, формирователь 5 детерминированной последовательности. Формирователь 5 обеспечивает поочередную выборку микрокоманд из блоков 1 и 2 памяти, что позволяет равномерно заполнять оба блока памяти. 1 з.п. ф-лы, 4 ил.

гш

Конец йбв.г

/дар;to«

Лиг освЕдопит.йыходнк

адреса сиенмовtiutcpomefnii.

ЯО Ш Ю ЛЗ Д«

Ре1дакто р А. Or ар

Составитель В.Криворучко

Техред Л.СердюковаКорректор М.Максимишинеп

Заказ 2666/48

Тираж 704

ВНИИПИ Государственного ко1читета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Подписное

| Балашов Е.П., Пузанков Д.В | |||

| Микропроцессоры и микропроцессорные систеьы | |||

| М.: Радио и связь, 1981, с | |||

| Устройство для вытяжки и скручивания ровницы | 1923 |

|

SU214A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Микропрограммное устройство управления | 1981 |

|

SU964640A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-05-30—Публикация

1986-12-15—Подача