Изобретение относится к вычислительной технике и может быть использовано при проектировании р егистров.

Цель изобретения - расширение функциональных возможностей регистра за счет выполнения поразрядных логических операций.

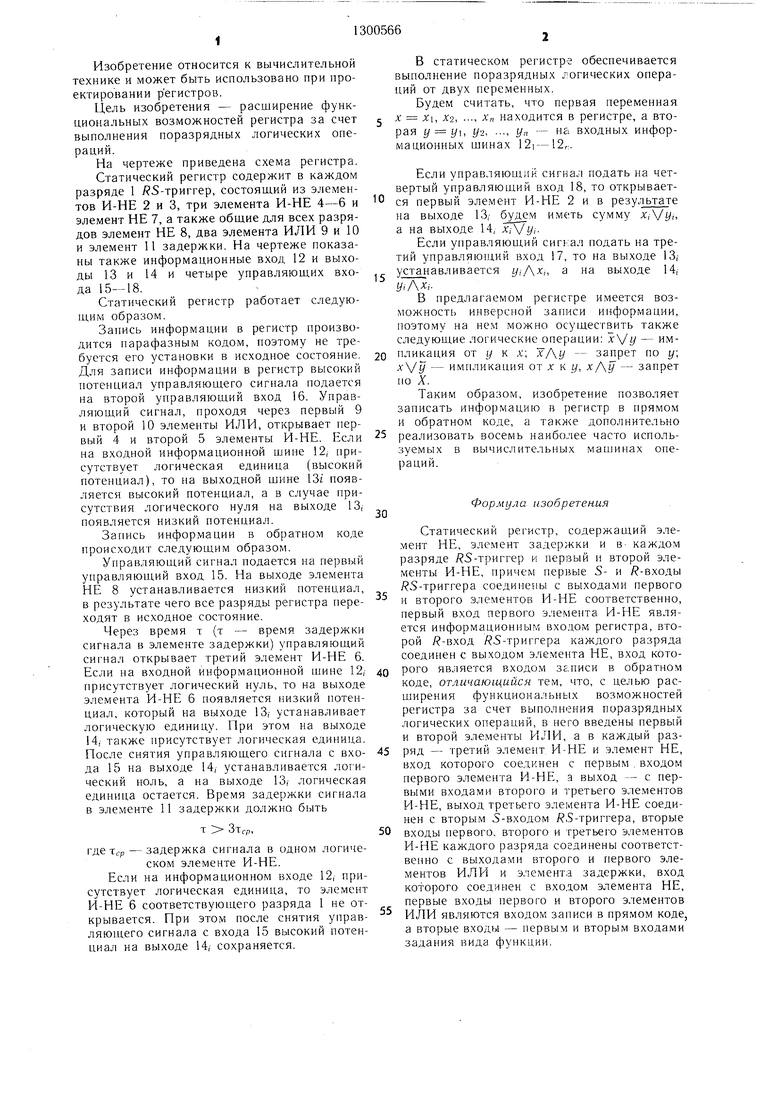

На чертеже приведена схема регистра.

Статический регистр содержит в каждом разряде 1 / 5-триггер, состоящий из элементов И-НЕ 2 и 3, три элемента И-НЕ 4-6 и элемент НЕ 7, а также общие для всех разрядов элемент НЕ 8, два элемента ИЛИ 9 и 10 и элемент 11 задержки. На чертеже показаны также информационные вход 12 и выходы 13 и 14 и четыре управляющих входа 15-18.

Статический регистр работает следующим образом.

Запись информации в регистр производится парафазным кодом, поэтому не требуется его установки в исходное состояние. Для записи информации в регистр высокий потенциал управляющего сигнала подается на второй управляющий вход 16. Управляющий сигнал, проходя через первый 9 и второй 10 элементы ИЛИ, открывает первый 4 и второй 5 элементы И-НЕ. Если на входной информационной шине 12, присутствует логическая единица (высокий потенциал), то на выходной шине 13i появляется высокий потенциал, а в случае присутствия логического нуля на выходе 13, появляется низкий потенциал.

Запись информации в обратном коде происходит следующим образом.

Управляюпхий сигнал подается на первый управляющий вход 15. На выходе элемента НЕ 8 устанавливается низкий потенциал, в результате чего все разряды регистра переходят в исходное состояние.

Через время т (т - время задержки сигнала в элементе задержки) управляющий сигнал открывает третий элемент И-НЕ 6. Если на входной информационной шине 12, присутствует логический нуль, то на выходе элемента И-НЕ 6 появляется низкий потенциал, который на выходе 13,- устанавливает логическую единицу. При этом на выходе 14, также присутствует логическая единица. После снятия управляющего сигнала с входа 15 на выходе 14, устанавливается логический ноль, а на выходе 13,- логическая единица остается. Время задержки сигнала в элементе 11 задержки должно быть

т ЗТгр,

где Тер - задержка сигнала в одном логическом элементе И-НЕ. Если на информационном входе 12, присутствует логическая единица, то элемент И-НЕ 6 соответствующего разряда 1 не открывается. При этом после снятия управляющего сигнала с входа 15 высокий потенциал на выходе 14, сохраняется.

В статическом регистре обеспечивается выполнение поразрядных .логических операций от двух переменных.

Будем считать, что первая переменная X Х, Х2, ..., Хп находится в регистре, а вторая у У, t/2, ..., у„ - н входных информационных щинах 12 -12,;.

Если упраЕ5ляющ; Й сигнал подать на четвертый управляющий вход 18, то открывается первый элемент И-НЕ 2 и в результате на выходе 13/ будем иметь сумму ,, а на выходе 14, x,-Vi/.Если управляюпгий сигнал подать на третий управляющий вход 17, то на выходе 13, 1а21авливается у.Дх,, а на выходе 14, y,.

В предлагаемом регистре имеется возможность инверсной записи информации, поэтому на нем можно осуществить также следующие логические операции: - импликация от у к х; ГДу - запрет по у; - импликация от х к у, - запрет по X.

Таким образом, изобретение позволяет записать информацию в регистр в прямом и обратном коде, а дополнительно

реализовать восемь наиболее часто используемых в вычислительных машинах операций.

30

Формула изобретения

Статический регистр, содержащий элемент НЕ, элемент задержки и в каждом разряде / 5-триггер и первый и второй элементы И-НЕ, причем первые S- и / -входы / 5-триггера соединены с выходами первого

и второго элементов И-НЕ: соответственпо, первый вход первого элемента И-НЕ является информационным входом регистра, второй / -вход / 5-триггера каждого разряда соединен с выходом элемента НЕ, вход которого является входом Зс.писи в обратном коде, отличающийся тем, что, с целью расширения функциональных возможностей регистра за счет выполнения поразрядных логических операций, в него введены первый и второй элементы ИЛИ, а в каждый разряд - третий элемент И-НЕ и элемент НЕ, вход которого соединен с первым . входом первого элемента И-НЕ, а выход - с первыми входами второго и третьего эле.ментов И-НЕ, выход третьего элемента И-НЕ соединен с вторым 5-входом /.5-триггера, вторые

входы lepBoro. второго и третьего элементов И-НЕ каждого разряда соединены соответственно с выходами второго и первого элементов ИЛИ и элемента задержки, вход которого соединен с входом элемента НЕ, первые входы первого и второго элементов

ИЛИ являются входом записи в прямом коде, а вторые входы - первым и вторым входами задания вида функции.

12.

л

18 16 Л Г5

Jn

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный регистр | 1986 |

|

SU1411828A1 |

| Статический регистр | 1986 |

|

SU1388952A1 |

| Логическое запоминающее устройство | 1972 |

|

SU442512A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Устройство для выделения максимального числа | 1982 |

|

SU1024902A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для анализа параметров графа | 1988 |

|

SU1681312A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1282122A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании регистров. Целью изобретения является расширение функциональных возможностей регистра за счет выполнения поразрядных логических операций. Для достижения этой цели в каждый разряд регистра введены элемент И-НЕ и элемент НЕ, а также общие для всех разрядов два элемента ИЛИ. Это позволило получать на выходах регистра функции x/Vi/;. , , , где X - состояние /-го разряда регистра, у - значение сигнала- на информационном входе i -ro разряда регистра. 1 ил. со о о сд СП 05

| Угрюмов Е | |||

| П | |||

| Элементы и узлы ЭЦВМ | |||

| М.: Высшая школа, 1976, с | |||

| ПЕЧНОЙ ЖЕЛЕЗНЫЙ РУКАВ (ТРУБА) | 1920 |

|

SU199A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Статический регистр | 1981 |

|

SU1069003A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-03-30—Публикация

1985-11-14—Подача