ее

00

оо со

ел

ьо

1

Изобретение относится к вычислительной технике и предназначено для реализации УЗЛОВ и устройств цифровых вычислительных машин методами интегральной технологии.

Целью изобретения является расширение функциональных возможностей регистра за счет выполнения поразрядных логических операций.

На чертеже представлена схема статического триггера.

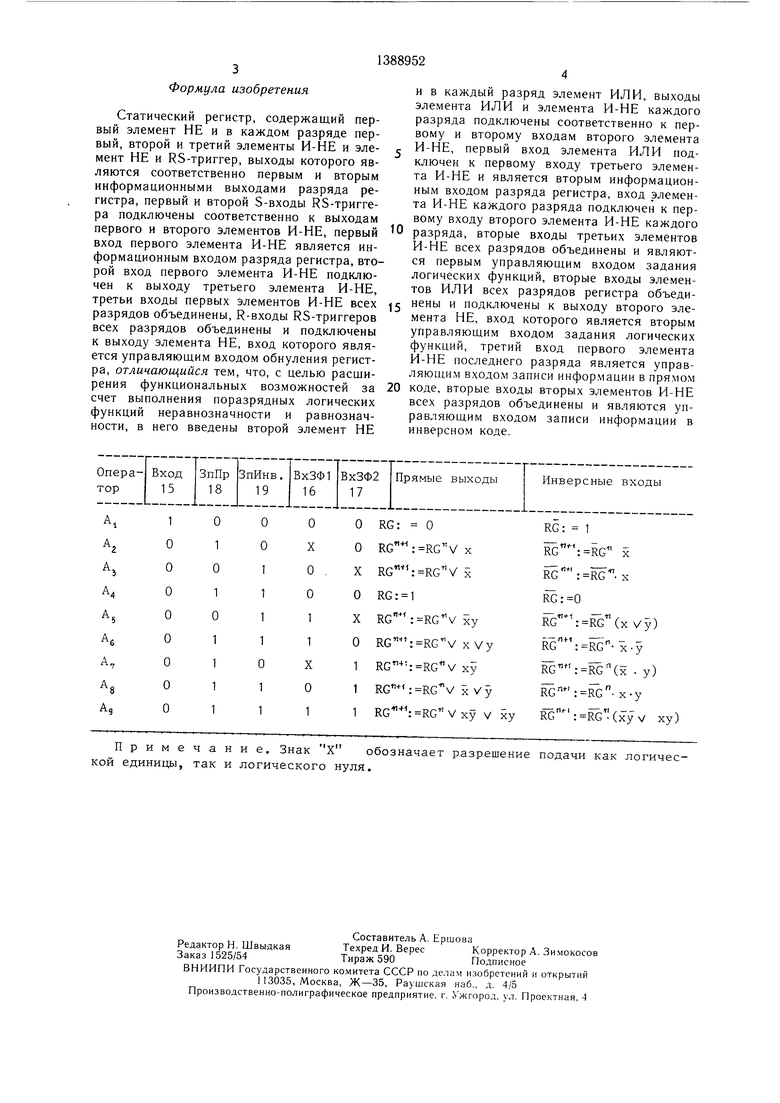

В таблице представлены микрооперации регистра.

Регистр содержит в каждом разряде 1 RS-триггер на элементах И-НЕ 2, 3 и пер- рый, второй, третий элементы И-НЕ 4, 5, 6, элемент НЕ 7, элемент ИЛИ 8, первый и второй информационные входы 9, 10 и выходы 11, 12. Кроме того, регистр содержит первый и второй элемент) НЕ 13, 14, управ- ляюш,ие входы 15-19, вход обнуления, первый и второй входы задания логических функций, входы записи информации в прямом и инверсном кодах.

Устройство работает следующим образом.

Все функции в статическом регистре выполняются на основе девяти микроопераций (операторов) AI-Ад.

Перед приемом информации оператором AI происходит установка регистра в исходное состояние, т. е. путем подачи логической единицы на вход 15. Соответственно низкий уровень напряжения устанавливается на выходе первого элемента НЕ 13. RS- триггеры устанавливаются в нулевое состояние. Высокий потенциал напряжения появляется на выходах 12i - 12h регистра.

Прием информации в прямом коде осуществляется оператором Аг, т. е. высокий потенциал напряжения подается на вход 18, открывается элемент И-НЕ 4, и входная информация подается на первый S-вход RS- триггера 2 (3). В результате выполняется функция : , где RG - содержимое регистра. Однако RG О, поэтому : Х.

Ввод информации в инверсном коде осуществляется оператором АЗ. После подачи логической единицы на вход 19 открывается элемент И-НЕ 5, на первый вход которого подается инверсная информация входного кода. В резул ьтате выполняется операция . При получаем .

Логические операции в основном выполняются в RS-триггерах 2, 3, характеристическое уравнение которого имеет вид SVRQ

Поразрядные логические операции от двух переменных выполняются следующим образом.

Первая переменная X находится в регистре, а вторая У присутствует на вхо- цах 9i-9„.

5

Если реализовать оператор А2, в результате выполняется операция дизъюнкции, г. е. RG - i RG -Vy. Однако , поэтому RG : XVy- Результат реализации операции дизъюнкции получается на выходах 11.1 - 11.П регистра. Одновременно на выходах 12. регистра получаем функцию .

Для осуществления поразрядной операции конъюнкции в первую очередь после усО тановки регистра в исходное состояние реализуется оператор Аз, с помощью которого происходит запись инверсного кода первого переменного X. Далее повторно реализуется оператор АЗ, но при этом на вход

- 9-п подается второй операнд У. В результате на выходе 12п регистра получаем функцию конъюнкции Х&У. Операция конъюнкции получается также при реализации оператора AS, притом результат операции появляется также на выходе 12.п регистра. Для

0 реализации оператора As следует логические единицы подавать на входы 17, 18, 19. При этом открываются элементы И-НЕ 4, 5, 6, на первый 5-вход RS-триггера подается функция Х-У, а на второй - функция X. В результате в получаем функцию на прямом выходе П.п, а на выходе RS-триггера - функцию Х- У. При такой реализации функции конъюнкции необходимо предварительно регистр обнулять оператором AI и операнды X и У одQ повременно подавать на входы 9 и 10.

При реализации операции дизъюнкции и конъюнкции реализуются операции Пирса XVy и Шеффера Х&У.

Операция сложения по mod2 двух операндов реализуется оператором Ад. С этой

5 целью на входы 19, 18, 16, 17 подаются логические единицы. Операнды X и У одновременно подаются на входы 9 и 10, одновременно открываются элементы И-НЕ 4, 5, 6, снимается высокий потенциал с второго входа элемента ИЛИ 8. В результате на

0 S-входах RS-тригге а появляются соответственно функции ХУ и ХУ и на выходе 11 регистра результат реализации функции ХУ Одновременно на выходе 12 регистра устанавливается результат

г реализации функции равнозначности. Заметим, что перед реализацией операции сло- жения по mod2 следует регистр предварительно установить в исходное состояние. С помощью операторов AI-Ад реализуются все логические операции одной и двух

0 переменных, которые легко можно получить при определенном сочетании функций, перечисленных в таблице.

Для осуществления логических операций от трех переменных предварительно реализуются логические операции от двух или од5 ной переменной, а в следующем такте дополнительно осуществляется один из операторов А|-Ад. Аналогично реализуются логические операции от четырех переменных.

Формула изобретения

Статический регистр, содержащий первый элемент НЕ и в каждом разряде первый, второй и третий элементы И-НЕ и элемент НЕ и RS-триггер, выходы которого являются соответственно первым и вторым информационными выходами разряда регистра, первый и второй S-входы RS-триггеи в каждый разряд элемент ИЛИ, выходы элемента ИЛИ и элемента И-НЕ каждого разряда подключены соответственно к первому и второму входам второго элемента И-НЕ, первый вход элемента ИЛИ подключен к первому входу третьего элемента И-НЕ и является вторым информационным входом разряда регистра, вход элемента И-НЕ каждого разряда подключен к первому входу второго элемента И-НЕ каждого

ра подключены соответственно к выходам. . ,

первого и второго элементов И-НЕ, первый разряда, вторые входы третьих элементов

вход первого элемента И-НЕ является ин-И-НЕ всех разрядов объединены и являютформационным входом разряда регистра, вто-ся первым управляющим входом задания

рой вход первого элемента И-НЕ подклю-логических функций, вторые входы элеменчен к выходу третьего элемента И-НЕ,тов ИЛИ всех разрядов регистра объедитретьи входы первых элементов И-НЕ всех 5 подключены к выходу второго элеразрядов объединены, R-входы RS-триггеровмента НЕ, вход которого является вторым

всех разрядов объединены и подключены к выходу элемента НЕ, вход которого является управляющим входом обнуления регистра, отличающийся тем, что, с целью расщиуправляющим входом задания логических функций, третий вход первого элемента И-НЕ последнего разряда является управляющим входом записи информации в прямом

рения функциональных возможностей за20 коде, вторые входы вторых элементов И-НЕ

счет выполнения поразрядных логическихвсех разрядов объединены и являются упфункций неравнозначности и равнознач-равляющим входом записи информации в

ности, в него введены второй элемент НЕинверсном коде.

и в каждый разряд элемент ИЛИ, выходы элемента ИЛИ и элемента И-НЕ каждого разряда подключены соответственно к первому и второму входам второго элемента И-НЕ, первый вход элемента ИЛИ подключен к первому входу третьего элемента И-НЕ и является вторым информационным входом разряда регистра, вход элемента И-НЕ каждого разряда подключен к первому входу второго элемента И-НЕ каждого

. . ,

разряда, вторые входы третьих элементов

управляющим входом задания логических функций, третий вход первого элемента И-НЕ последнего разряда является управляющим входом записи информации в прямом

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый логический модуль | 1985 |

|

SU1273916A1 |

| Управляемый арифметический модуль | 1979 |

|

SU832553A1 |

| Микропроцессор | 1977 |

|

SU717772A1 |

| Многофункциональный регистр | 1986 |

|

SU1411828A1 |

| Управляемый арифметический модуль | 1982 |

|

SU1062688A1 |

| Управляемый арифметический модуль | 1989 |

|

SU1695292A1 |

| Управляемый арифметический модуль | 1988 |

|

SU1585792A2 |

| Управляемый логический модуль | 1984 |

|

SU1196851A1 |

| Устройство для вычисления булевых функций | 1980 |

|

SU955027A1 |

| Микропроцессор с контролем | 1981 |

|

SU1016788A1 |

Изобретение относится к вычислительной технике и предназначено для реализации узлов и устройств цифровых вычислительных машин методами интегральной технологии. Цель изобретения - расширение функциональных возможностей регистра за счет выполнения поразрядных логических операций неравнозначности и равнозначности. Все функции в статическом регистре выполняются на основе девяти микроопераций (операторов А1-А9). Для осуществления логических операций от трех переменных предварительно реализуются логические операции от двух или одной переменной, а в следующем такте дополнительно осуществляется один из операторов (А1-А9). Аналогично реализуются логические операции от четырех переменных. Регистр содержит элементы НЕ 13, 14 п-раз- рядов, каждый из которых состоит из RS-триг- гера 1, элементов И-НЕ 4, 5, 6, 7, элемента ИЛИ. 1 ил., 1 табл.

Примечание, Знак X обозначает разрешение подачи как логической единицы, так и логического нуля.

| Статический регистр | 1981 |

|

SU1069003A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Статический регистр | 1985 |

|

SU1300566A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-04-15—Публикация

1986-10-16—Подача