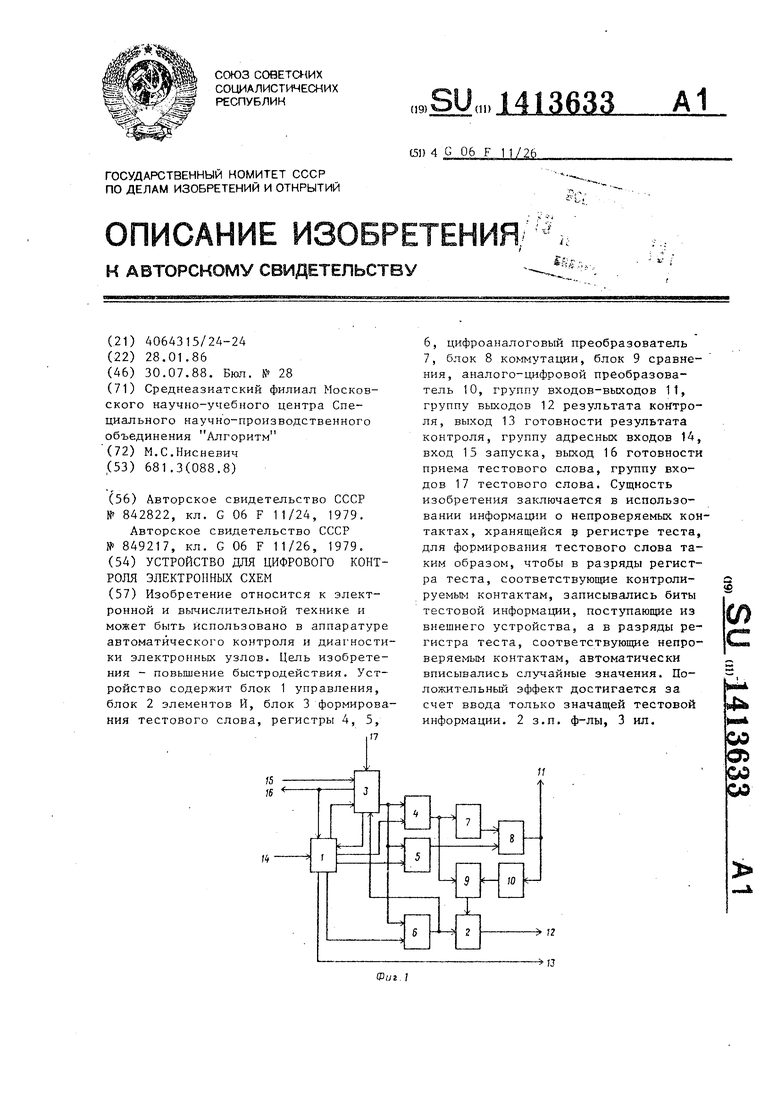

Изобретение относится к электронной и вычислительной технике и может быть использовано в аппаратуре автоматического контроля и диагностики электронных узлов.

Цель изобретения - повышение быстродействия .

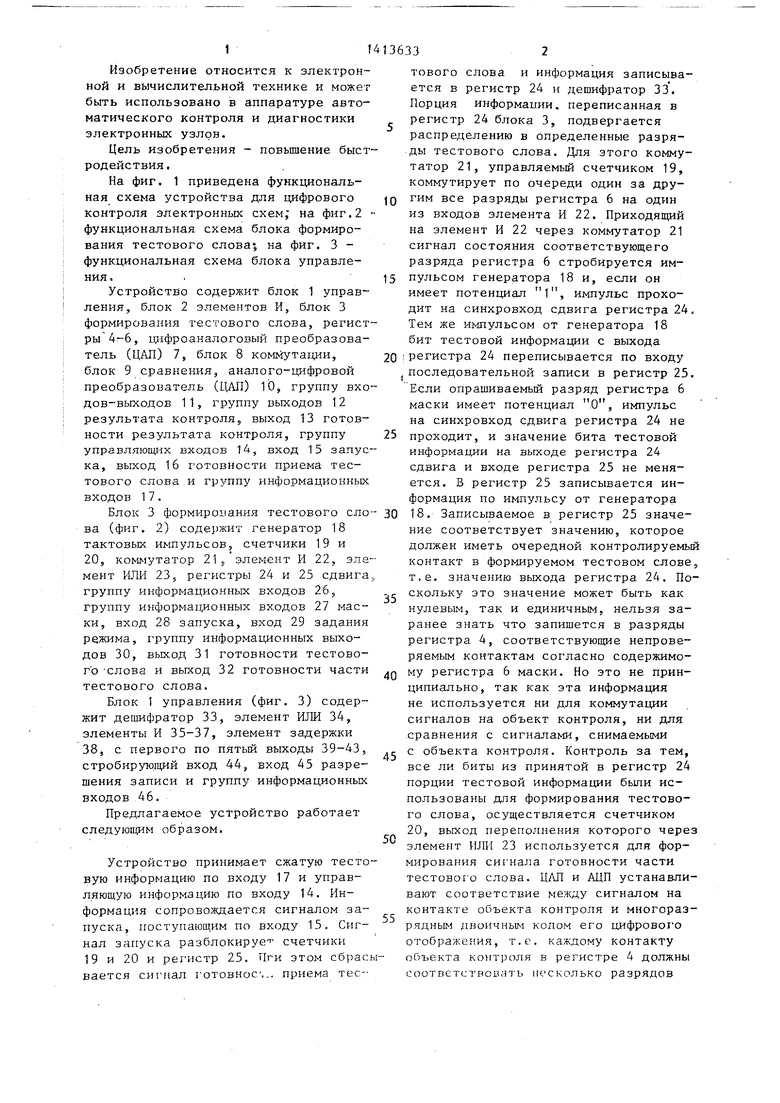

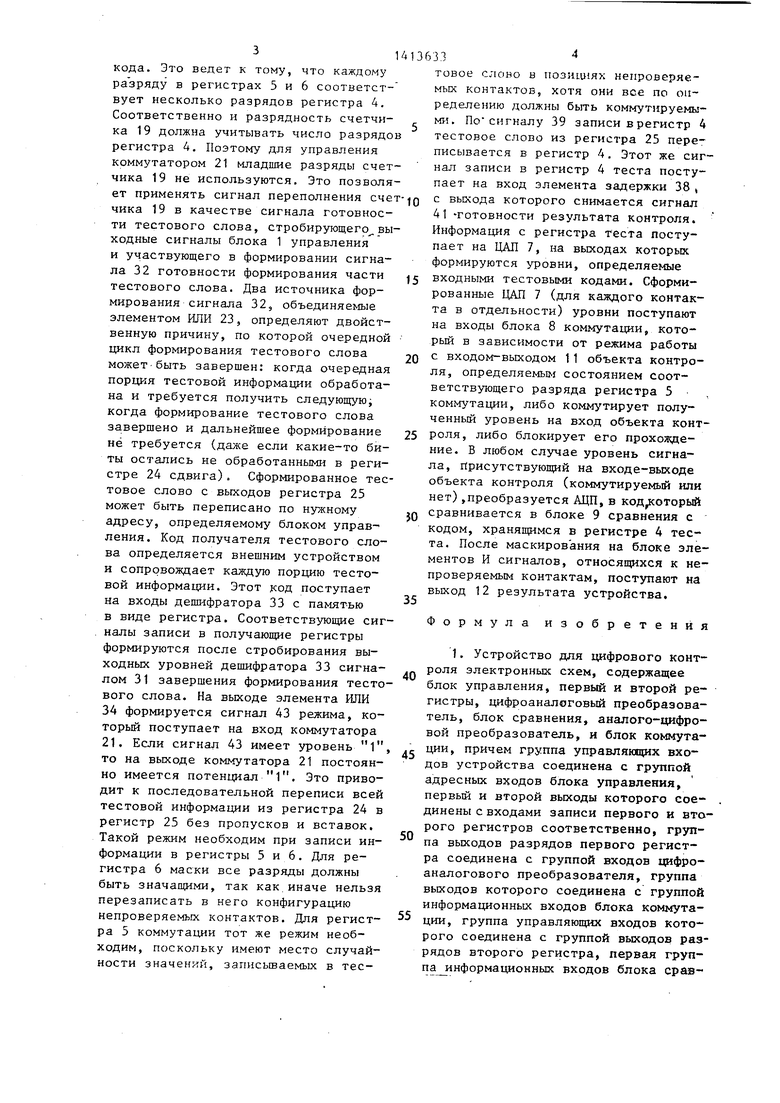

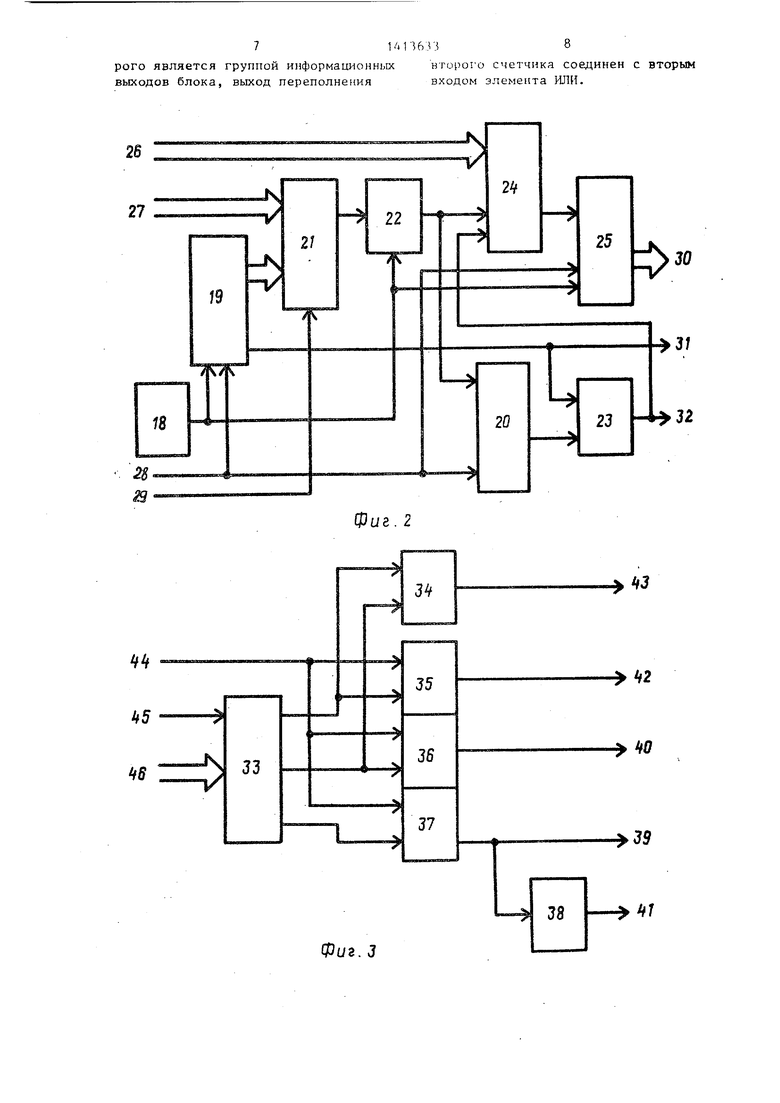

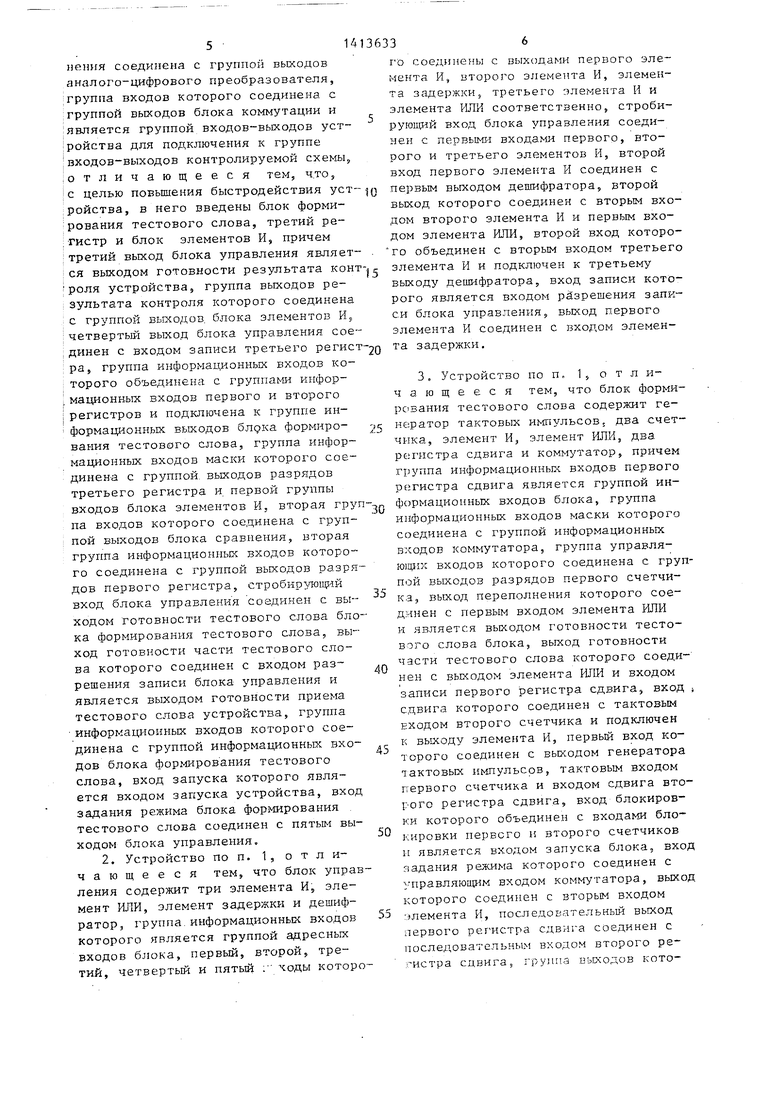

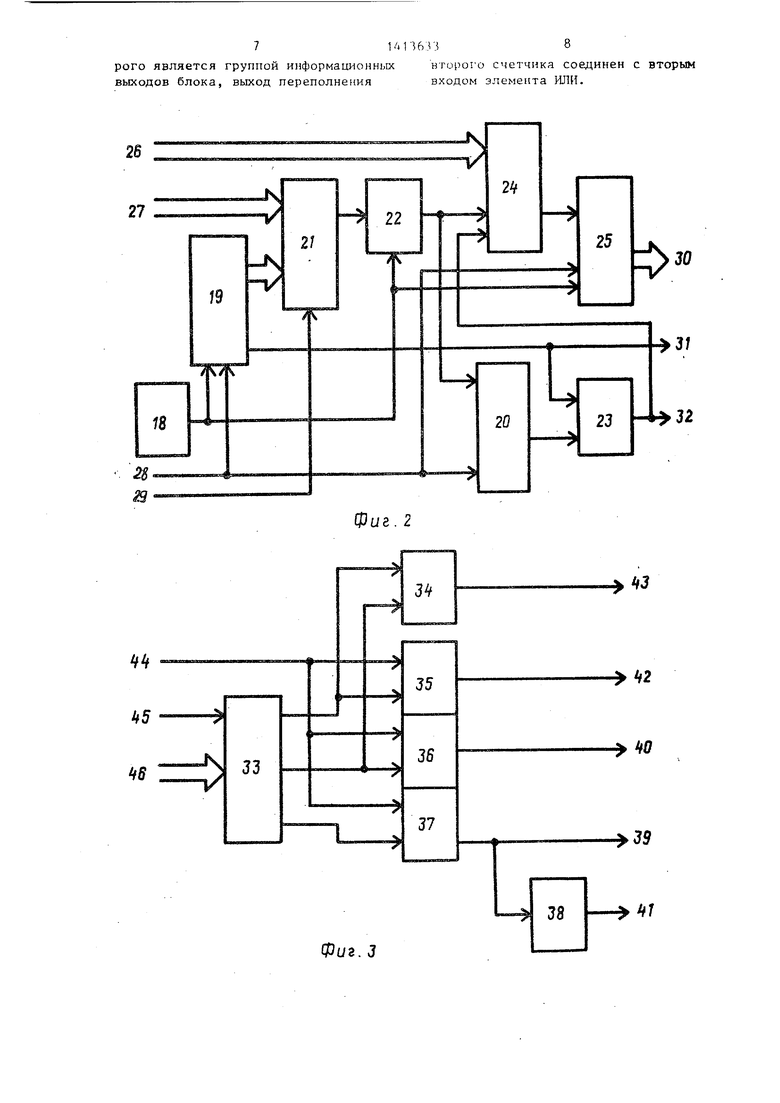

На фиг, 1 приведена функциональная схема устройства для цифрового контроля электронных схем; на фиг.2 функциональная схема блока формирования тестового словам на фиг. 3 - функциональная схема блока управления ,

Устройстйо содержит блок 1 управления, блок 2 элементов И, блок 3 формирования тестового слова, регистры 4-6, гщфроаналоговый преобразователь (ЦАП) 7, блок 8 коммутах-щи, блок 9 сравнения, аналого-цифровой преобразователь (ЬУШ) 10, группу входов-выходов 11, группу выходов 12 реэультата контроля, выход 13 готовности результата контроля, группу управляющих входов 14, вход 15 запуска, выход 16 готовности приема тестового слова и группу информационных входов 17.

Блок 3 формиро1 ания тестового слова (фиг. 2) содержит генератор 18 тактовых импульсов, счетчики 19 и 20, коммутатор 21, элемент И 22, элемент ИЛИ 23, регистры 24 и 25 сдвига группу информационных входов 26, группу информапдонных входов 27 маски, вход 28 запуска, вход 29 задания режима, группу информационных выходов 30, выход 31 готовности тестового -слова и выход 32 готовности части тестового слова.

Блок 1 управления (фиг. 3) содержит деишфратор 33, элемент ИЛИ 34, элементы И 35-37, элемент задержки 38, с первого по пятьй выходы 39-43, стробируюгций вход 44, вход 45 разрешения записи и группу информационных входов 46.

Предлагаемое устройство работает следуюпщм образом.

Устройство принимает сжатую тестовую информацию по входу 17 и управляющую информацию по входу 14. Информация сопровождается сигналом запуска, поступающим по входу 15. Сигнал запуска разблокируе счетчики 19 и 20 и регистр 25. Пги этом сбрасвается готовнос ,. приема тестового слова и информация записывается в регистр 24 и дешифратор ЗЗ . Порция информации, переписанная в регистр 24 блока 3, подвергается распределению в определенные разряды тестового слова. Для этого коммутатор 21, управляемый счетчиком 19, коммутирует по очереди один за дру0 гим все разряды регистра 6 на один из входов элемента И 22. Приходящий на элемент И 22 через коммутатор 21 сигнал состояния соответствующего разряда регистра 6 стробируется им5 пульсом генератора 18 и, если он имеет потенциал 1, импульс проходит на синхровход сдвига регистра 24. Тем же импульсом от генератора 18 бит тестовой информации с выхода

0 I регистра 24 переписывается по входу Jпоследовательной записи в регистр 23. Если опрашиваемый разряд регистра 6 маски имеет потенциал .О, импульс на синхровход сдвига регистра 24 не

5 проходит, и значение бита тестовой информации на выходе регистра 24 сдвига и входе регистра 25 не меняется. В регистр 25 записывается информация по импульсу от генератора

0 18. Записываемое в регистр 25 значение соответствует значению, которое должен иметь очередной контролируемый контакт в формируемом тестовом слове, . значению выхода регистра 24. Пос скольку это значение может быть как нулевым, так и единичным, нельзя заранее знать что запишется в разряды регистра 4, соответствующие непрове- ряемьм контактам согласно содержимо0 му регистра 6 маски. Но это не принципиально, так как эта информация не используется ни для коммутации сигналов на объект контроля, ни для .сравнения с сигналами, снимаемыми

г с объекта контроля. Контроль за тем, все ли биты из принятой в регистр 24 порции тестовой информации были использованы для формирования тестового слова, осуществляется счетчиком 20, выход переполнения которого через элемент ИЛИ 23 используется для формирования сигнала готовности части тестового слова. ЦЛЛ и АЦП устанавливают соответствие между сигналом на контакте объекта контроля и многоразрядным двоичным кодом его цифровох о отображения, т.е. каждому контакту объекта контроля в регистре 4 должны соответствовать несколько разрядов

0

5

31

кода. Это ведет к тому, что каждому ра зряду в регистрах 5 и 6 соответст- вует несколько разрядов регистра 4. Соответственно и разрядность счетчика 19 должна учитывать число разрядов регистра 4, Поэтому для управления коммутатором 21 младшие разряды счетчика 19 не используются. Это позволяет применять сигнал переполнения счетчика 19 в качестве сигнала готовности тестового слова, стробирующегр выходные сигналы блока 1 управления и участвующего в формировании сигнала 32 готовности формирования части тестового слова. Два источника формирования сигнала 32, объединяемые элементом ИЛИ 23, определяют двойственную причину, по которой очередной цикл формирования тестового слова может-быть завершен: когда очередная порция тестовой информации обработана и требуется получить следующую когда формирование тестового слова за вершено и дальнейшее формирование не требуется (даже если какие-то биты остались не обработанными в регистре 24 сдвига) Сформированное тестовое слово с выходов регистра 25 может быть переписано по нужному адресу, определяемому блоком управления. Код получателя тестового слова определяется внешним устройством и сопровождает каждую порцию тестовой информации. Этот код поступает на входы дешифратора 33 с памятью в виде регистра. Соответствующие сигналы записи в получающие регистры формируются после стробирования выходных уровней дешифратора 33 сигналом 31 завершения формирования тестового слова. На выходе элемента ИЛИ 34 формируется сигнал 43 режима, который поступает на вход коммутатора 21. Если сигнал 43 имеет уровень 1 то на выходе коммутатора 21 постоянно имеется потенциал 1. Это приводит к последовательной переписи всей тестовой информации из регистра 24 в регистр 25 без пропусков и вставок. Такой режим необходим при записи информации в регистры 5 и 6. Для регистра 6 маски все разряды должны быть значащими, так как иначе нельзя перезаписать в него конфигурацию непроверяемых контактов. Для регистра 5 коммутации тот же режим необходим, поскольку имеют место случайности значении, записьшаемых в тес3633

товое слово в познщшх непроверяемых контактов, хотя они все по определению должны быть коммутируемыми. По сигналу 39 записи в регистр 4 тестовое слово из регистра 25 переписывается в регистр 4, Этот же сигнал записи в регистр 4 теста поступает на вход элемента задержки 38 ,

с выхода которого снимается сигнал 41 ГОТОВНОСТИ результата контроля. Информация с регистра теста поступает на ЦАП 7, на выходах которых формируются уровни, определяемые

5 входными тестовыми кодами. Сформированные ЦАП 7 (для каждого контакта в отдельности) уровни поступают на входы блока 8 коммутации, который в зависимости от режима работы

0 с входом-выходом 11 объекта контроля, определяемым состоянием соответствующего разряда регистра 5 коммутации, либо коммутирует полученный уровень на вход объекта конт5 роля, либо блокирует его прохождение. В любом случае уровень сигнала, присутствующий на входе-выходе объекта контроля (коммутируемый или нет),преобразуется АЦП, в код оторый

Q сравнивается в блоке 9 сравнения с кодом, хранящимся в регистре 4 теста. После маскирования на блоке элементов И сигналов, относящихся к не- проверяемьм контактам, поступают на выход 12 результата устройства.

Формула изобретения

1. Устройство для цифрового контроля электронных схем, содержащее блок управления, первый и второй регистры, цифроаналоговьй преобразователь, блок сравнения, аналого-цифровой преобразователь, и блок коммута.- ции, причем группа управлямщих входов устройства соединена с группой адресных входов блока управления, первый и второй выходы которого соединены с входами записи первого и второго регистров соответственно, группа выходов разрядов первого регистра соединена с группой входов цифро- аналогового преобразователя, группа выходов которого соединена с группой информационных входов блока коммута ции, группа управляющих входов которого соединена с группой выходов разрядов второго регистра, первая группа информационных входов блока срав0

0

нения соединена с группой выходов аналого-цифрового преобразователя, ;группа входов которого соединена с группой выходов блока коммутации и является группой входов-выходов уст- ipoftcTBa для подключения к группе входов-выходов контролируемой схемы, отличающееся тем, что, с целью повышения быстродействия уст :ройства, в него введены блок форми- ;рования тестового слова, третий ре- :гистр и блок элементов И, причем третий выход блока управления являет :ся выходом ГОТОВНОСТИ результата кон роля устройства, группа выходов результата контроля которого соединена с группой выходов, блока элементов И четвертый выход блока управления соединен с входом записи третьего регисра , группа информационных входов которого объединена с группаъш инфор- : мационных входов первого и второго : регистров и подключена к группе ин- формационньгх выходов блрка формирования тестового слова, группа информационных входов маски которого соединена с группой, выходов разрядов третьего регистра и, первой группы входов блока элементов И. вторая група входов которого соединена с группой выходов блока сравнения, вторая группа информационных входов которого соединена с группой выходов разрядов первого регистра, стробнр то11рй вход блока управления соединен с выходом готовности тестового слова блока формирования тестового слова, выход готовности части тестового слова которого соединен с входом разрешения записи блока управления и является выходом готовности приема тестового слова устройства, группа информационных входов которого соединена с группой информационных входов блока формирования тестового слова, вход запуска которого является входом запуска устройства, вход задания режима блока формирования , тестового слова соединен с пятым выходом блока управления.

2. Устройство по п. 1, отличающееся тем, что блок управления содержит три элемента И, элемент ИЛИ, элеме.нт задержки и дешифратор, группа.информационных входов которого является группой адресных входов блока, первый, второй, третий, четвертый и пятый / ходы которого соединены с выходами первого элемента И, второго элемента И, элемента задержки, третьего элемента И и элемента ИЛИ соответственно, строби- рующий вход блока управления соеди- HEi с первыми входами первого, второго и третьего элементов И, второй вход первого элемента И соединен с

Q первым выходом дешифратора, второй выход которого соединен с вторым входом второго элемента И и первым входом элемента ИЛИ, второй вход которо- . То объединен с вторьм входом третьего

элемента И и подключен к третьему

выходу дешифратора, вход записи которого является входом разрешения записи блока управления,, выход первого элемента И соединен с входом элемен0 та задержки,

3. Устройство по п. 1, о т л и- чающееся тем, что блок форми- рс вания тестового слова содержит геi; нефатор тактовых импульсов, два счетчика, элемент И, элемент ИЛ.И5 два регистра сдвига и коммутатор, причем группа информационньк входов первого регистра сдвига является группой инр формационньгх входов блока, группа информационных входов маски которого соединена с группой информационных входов коммутатора, группа управляющих входов которого соединена с группой выходов разрядов первого счетчи- ка, выход переполнения которого соединен с первым входом элемента ИЛИ и является выходом готовности тестового слова блока, выход готовности части тестового слова которого соединен с выходом элемента ИЛИ и входом записи первого регистра сдвига, вход , сдвига которого соединен с тактовым входом второго счетчика и подключен к элемента И, первый вход которого соединен с выходом генератора тактовых импульсов, тактовым входом первого счетчика и входом сдвига второго регистра сдвига, вход блокировки которого объединен с входами блокировки первого и второго счетчиков II является входом запуска блока, вход задания режима которого соединен с управляющим входом коммутатора, выход которого соединен с вторым входом

5 : пемента И, последовательный выход первого рег истра сдвига соединен с последовательным входом второго регистра сдвига, группа БЫХОДОВ кото0

5

0

714116 УЗ8

рого является группой информационных второго счетчика соединен с вторым выходов блока, выход переполнения входом элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1386999A1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Микропрограммное устройство формирования тестовой последовательности | 1984 |

|

SU1267425A1 |

| Устройство для сопряжения микроЭВМ с внешним устройством | 1985 |

|

SU1283780A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1013960A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для сопряжения | 1980 |

|

SU926645A2 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1667073A1 |

Изобретение относится к электронной и вычислительной технике и может быть использовано в аппаратуре автоматического контроля и диагности ки электронных узлов. Цель изобретения - повышение быстродействия. Устройство содержит блок 1 управления, блок 2 элементов И, блок 3 формирова ния тестового слова, регистры 4, 5, | 7 6,цифроаналоговый преобразователь 7,блок 8 коммутации, блок 9 сравнения, аналого-цифровой преобразователь 10, группу входов-выходов 11, группу выходов 12 результата контроля, выход 13 готовности результата контроля, группу адресных входов 14, вход 15 запуска, выход 16 готовности приема тестового слова, входов 17 тестового слова. Сущность изобретения заключается в использовании информации о непроверяемых контактах, хранящейся в регистре теста, для формирования тестового слова таким образом, чтобы в разряды регистра теста, соответствующие контролируемым контактам, записывались биты тестовой информации, поступающие из внешнего устройства, а в разряды регистра теста, соответствующие непроверяемым контактам, автоматически вписывались случайные значения. Положительный эффект достигается за счет ввода только значащей тестовой информации. 2 з.п. ф-лы, 3 ил. « 00 а Од &э

| Устройство для контроля цифровыхузлОВ | 1979 |

|

SU842822A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровыхСХЕМ | 1979 |

|

SU849217A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-30—Публикация

1986-01-28—Подача