11

Изобретение относится к автоматике к вычислительной технике и может быть использовано для формирования сигналов, представленных в цифровой форме, предназначенных для отладки, контроля и исследования характеристик автоматизированных информационно-измерительных систем, систем обработки информации и автоматизированных систем контроля.

Целью изобретения является расширение функциональных возможностей за счет формирования импульсов с программируемой длительностью и периодом.

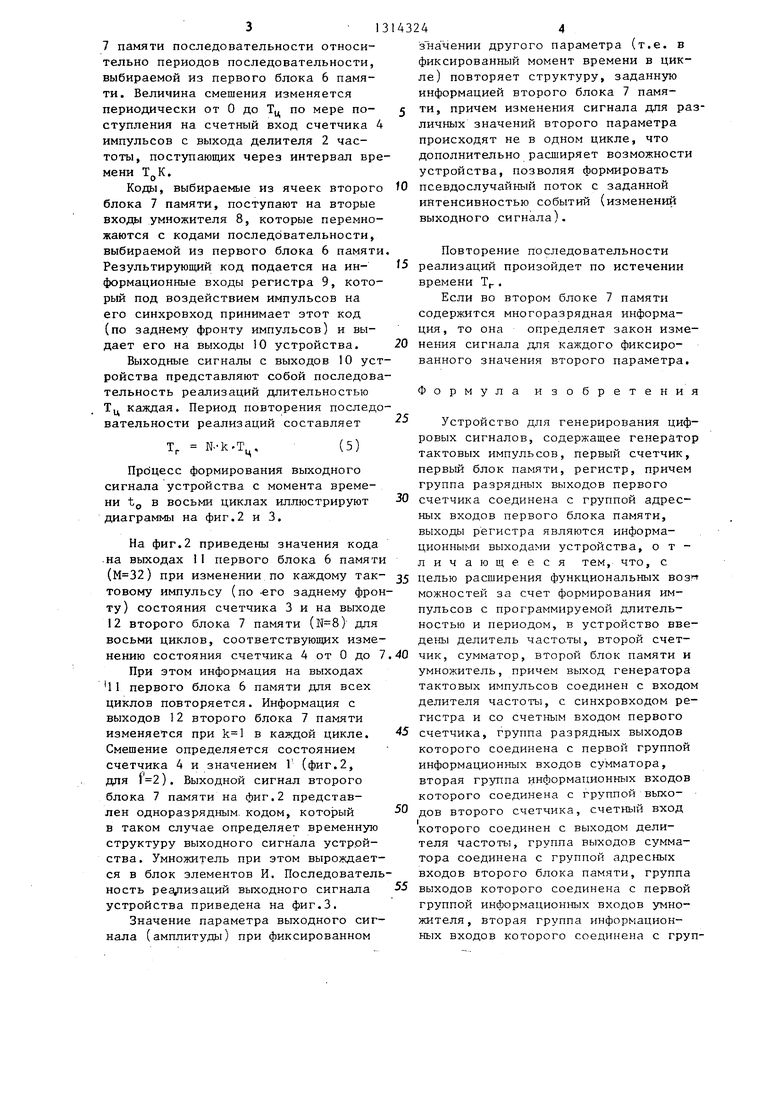

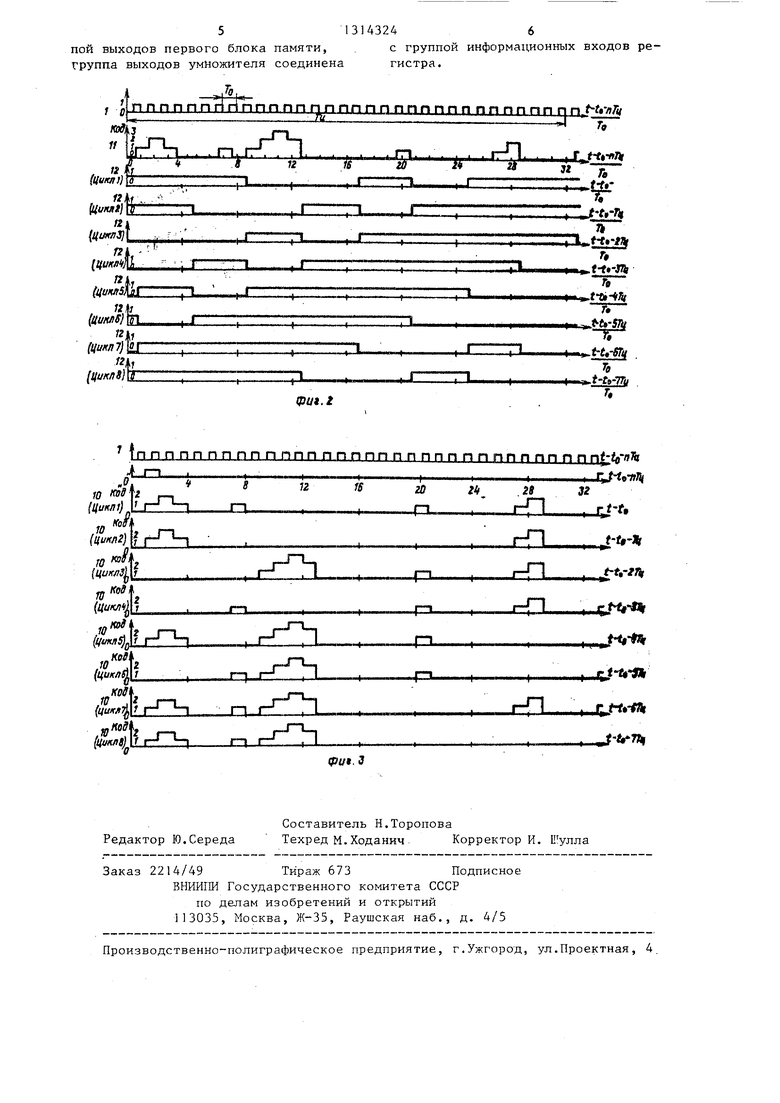

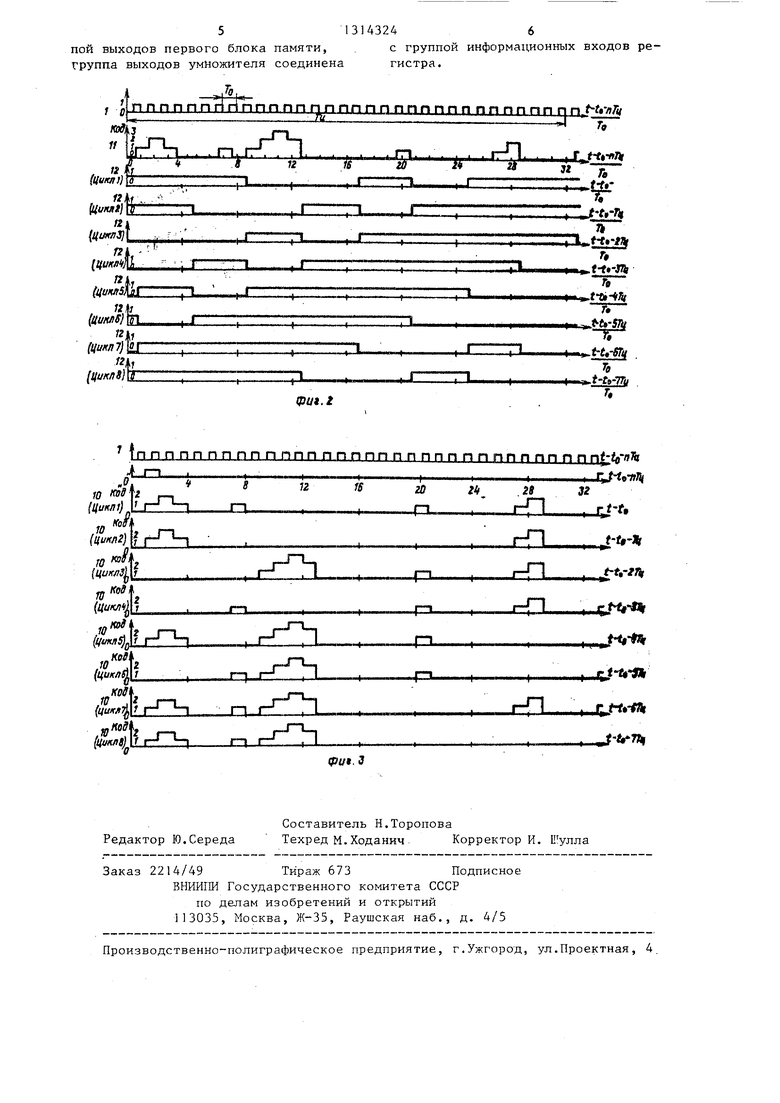

На фиг.1 изображена структурная схема предлагаемого устройства; на фиг.2 - временная диаграмма выходных сигналов первого и второго блоко памяти в последовательных циклах; на фиг.З - то же, устройства для информации в блоках памяти.

Устройство содержит генератор 1 тактовых импульсов, делитель 2 частоты, счетчики 3 и 4, сумматор 5, блоки 6 и- 7 памяти, умножитель 8, регистр 9, информационные выходы 10 устройства, выходы И первого блока 6 памяти, выходы 12 второго блока 7 памяти.

Устройство работает следующим образом.

В первом блоке 6 памяти, имеющем М ячеек, и во втором блоке 7 памяти, имеющем N ячеек, записаны последовательности цифровых кодов (характеризующие, например, значения амплитуд сигнала в дискретные моменты времени), которые считываются в процессе работы устройства и используются для формирования реализаций выходного сигнала. Выходной сигнал устройства представлен в цифровой форме, причем каждое из его значений получается перемножением кода последовательности, выбираемой из первого блока 6 -памяти и кода последовательности, выбираемой из второго блока 7 памяти.

Выбор последовательности из первого блока 6 памяти осуществляет счетчик 3, имеющий модуль пересчета М. По мере поступления на его . счетный вход периодической последовательности импульсов, вырабатываемой генератором 1 тактовых импульсов, счетчик 3 формирует адреса ячеек первого блока 6 памяти, содержимое

43242

которых при этом поступает в виде периодической последовательности цифровых кодов на входы умножителя 8, Период Тц, последовательности

5 (цикл формирования одной реализации) равен длительности цикла опроса М ячеек первого блока 6 памяти

Т МТ

)

1)

Ш

где Т - период следования импульсов.

Одновременно с выбором последовательности кодов из первого блока 6 памяти осуществляется также выбор данных из второго блока 7 памяти, длительность Т цикла опроса N ячеек которого равна Т.

41

т - Ц7

Тц, Т. (2)

25

Адреса ячеек второго блока 7 памяти формируются сумматором 5, осуществляющим сложение по модулю N кода, поступающего на его первые входы с выходов счетчика 3, с значением поступающим на его вторые входы с вЕ)1ходов счетчика 4, имеющего модуль пересчета N. .

Импульсы, н арапки в ающие счетчик 4,

поступают на его счетный вход от геал.

- нератора 1 тактовых импульсов через делитель 2 частоты, коэффициент деления К которого удовлетворяет условию

35 К k М,(3)

где k 1, 2, 3...; т.е. период поступления импульсов на счетный вход счетчика 4 относится к Тц как 1, 3

у

0 При выполнении условия (3) длителность цикла опроса Ы ячеек второго блока 7 памяти определяется только периодом смены кодов на первых входах сумматора 5, который может быть

увеличен с целью выполнения условия (2) отключением одного или нескольки выходов, соответствующих младшим разрядам счетчика 3, от входов сумматора 5. Это дает соотношение для выбо50 ра величин М и N

М е

(4)

где 0, 1,2, 3...- количество отключенных от входов сумматора 5 55 выходов счетчика 3.

Значение кода на вторых входах сумматора 5 определяет временное смешение выбираемой из второго блока

313

7 памяти последовательности относительно периодов последовательности, выбираемой из первого блока 6 памяти. Величина смешения изменяется периодически от О до Т по мере поступления на счетный вход счетчика 4 импульсов с выхода делителя 2 частоты, поступающих через интервал времени TjjK.

Коды, выбираемые из ячеек второго блока 7 памяти, поступают на вторые входы умножителя 8, которые перемножаются с кодами последовательности, выбираемой из первого блока 6 памяти Результирующий код подается на информационные входы регистра 9, который под воздействием импульсов на его синхровход принимает этот код (по заднему фронту импульсов) и выдает его на выходы 10 устройства.

Выходные сигналы с выходов 10 устройства представляют собой последовательность реализаций длительностью Тц каждая. Период повторения последовательности реализаций составляет

Т, K.-k T, (5)

Процесс формирования выходного сигнала устройства с момента времени tj, в восьми циклах иллюстрируют диаграммы на фиг.2 и 3.

На фиг.2 приведены значения кода на выходах 11 первого блока 6 памяти () при изменении по каждому тактовому импульсу (по -его заднему фронту) состояния счетчика 3 и на выходе 12 второго блока 7 памяти () для восьми циклов, соответствующих изменению состояния счетчика 4 от О до 7

При этом информация на выходах П первого блока 6 памяти для всех циклов повторяется. Информация с выходов 12 второго блока 7 памяти изменяется при в каждой цикле. Смешение определяется состоянием счетчика 4 и значением Г (фиг.2, для ). Выходной сигнал второго блока 7 памяти на фиг.2 представлен одноразрядным, кодом, который в таком случае определяет временную структуру выходного сигнала устройства. Умножитель при этом вырождается в блок элементов И. Последовательность ре(1изаций выходного сигнала устройства приведена на фиг.З,

Значение параметра выходного сигнала (амплитуды) при фиксированном

44

з на чении другого параметра (т.е. в фиксированный момент времени в цикле) повторяет структуру, заданную информацией второго блока 7 памя- ти, причем изменения сигнала для различных значений второго параметра происходят не в одном цикле, что дополнительно расширяет возможности устройства, позволяя формировать

псевдослучайный поток с заданной интенсивностью событий (изменений выходного сигнала).

Повторение последовательности реализаций произойдет по истечении времени Т.

Если во втором блоке 7 памяти содержится многоразрядная информация, то она определяет закон изме- нения сигнала для каждого фиксированного значения второго параметра.

Формула изобретения

Устройство для генерирования цифровых сигналов, содержащее генератор тактовых импульсов, первый счетчик, первый блок памяти, регистр, причем группа разрядных выходов первого

счетчика соединена с группой адресных входов первого блока памяти, выходы регистра являются информационными выходами устройства, отличающееся тем, что, с

целью расширения функциональных воз« можностей за счет формирования импульсов с программируемой длительностью и периодом, в устройство введены делитель часто.ты, второй счетчик, сумматор, второй блок памяти и умножитель, причем выход генератора тактовых импульсов соединен с входом делителя частоты, с синхровходом регистра и со счетным входом первого

счетчика, группа разрядных выходов которого соединена с первой группой информационных входов сумматора, вторая группа информационных входов которого соединена с группой выходов второго счетчика, счетный вход которого соединен с выходом делителя частоты, группа выходов сумматора соединена с группой адресных входов второго блока памяти, группа

выходов которого соединена с первой группой информационных входов умножителя, вторая группа информационных входов которого соединена с груп513143246

пой выходов первого блока памяти, . с группой информационных входов ре- группа выходов умножителя соединена гистра.

Редактор Ю.Середа

Составитель Н.Торопова

Техред М.Ходанич . Корректор И, П улла

Заказ 2214/49 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4,

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| Умножитель частоты | 1988 |

|

SU1562908A1 |

| Корреляционный измеритель времени запаздывания | 1983 |

|

SU1160433A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| Генератор псевдослучайных чисел | 1984 |

|

SU1239844A1 |

| Частотный анализатор | 1990 |

|

SU1798630A1 |

| Генератор сигналов сложной формы | 1980 |

|

SU983692A1 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

| Оптическое устройство для вычисления корреляционной функции | 1988 |

|

SU1520541A1 |

| Устройство для формирования монотонных функций двух переменных | 1977 |

|

SU763879A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 4404644, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-30—Публикация

1985-10-14—Подача