113

Изобретение относится к вычислительной технике, в частности к устройствам для контроля блоков памяти. Цель изобретения - повышение достоверности контроля.

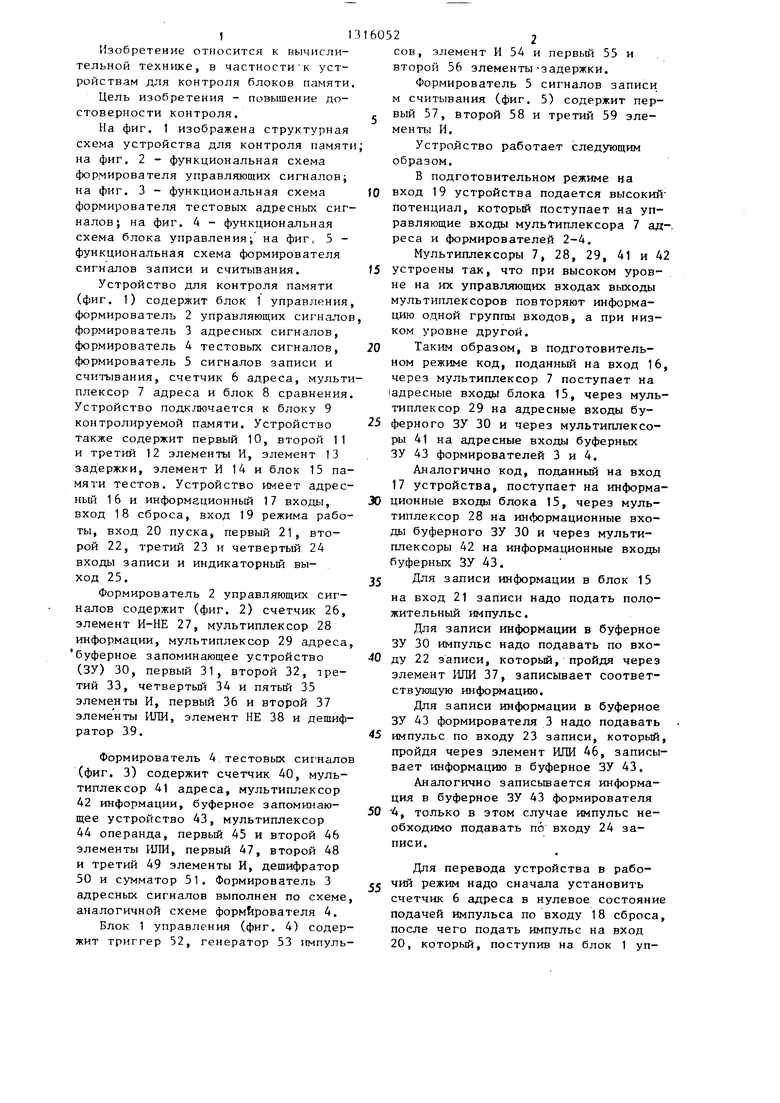

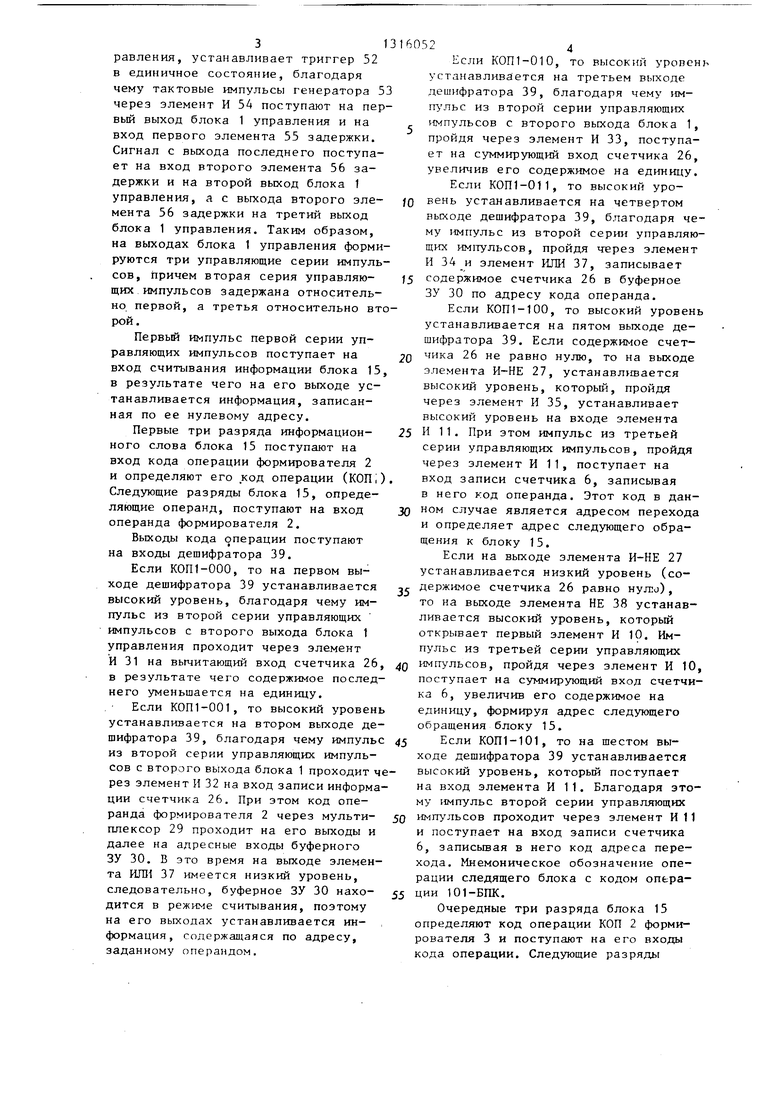

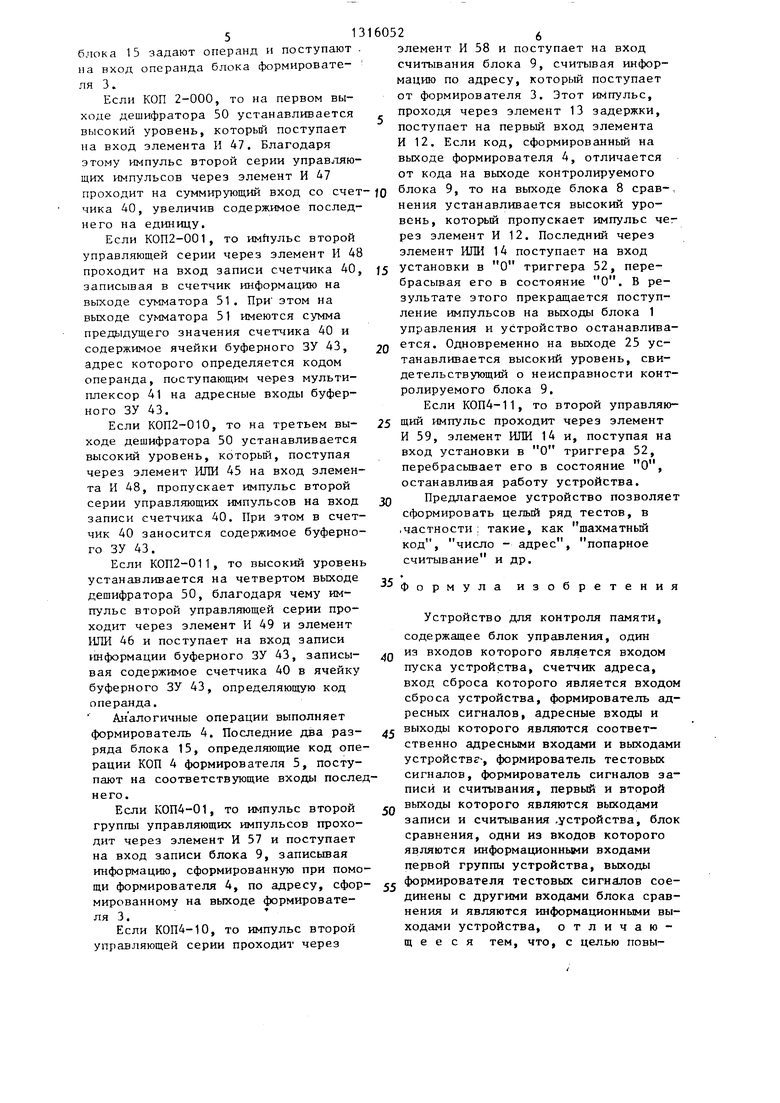

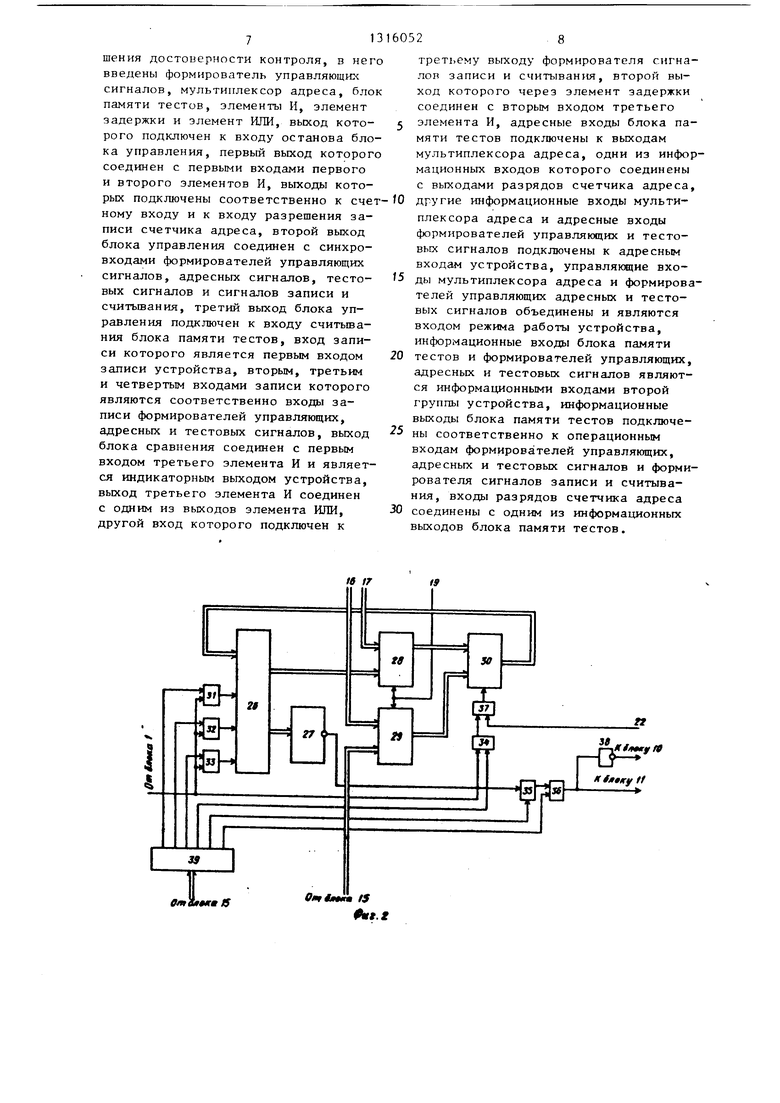

На фиг. 1 изображена структурная схема устройства для контроля памяти на фиг. 2 - функциональная схема формирователя управляющих сигналов; на фиг. 3 - функциональная схема формирователя тестовых адресных сигналов; на фиг. А - функциональная схема блока управления; на фиг с 5 - функциональная схема формирователя сигналов записи и считывания.

Устройство для контроля памяти (фиг. 1) содержит блок 1 управления, формирователь 2 управляющих сигналов формирователь 3 адресных сигналов, формирователь 4 тестовых сигналов, формирователь 5 сигналов записи и считывания, счетчик 6 адреса, мультиплексор 7 адреса и блок 8 сравнения. Устройство подключается к блоку 9 контролируемой памяти. Устройство также содержит первый 10, второй 11 и третий 12 элементы И, элемент 13 задержки, элемент И 14 и блок 15 памяти тестов. Устройство имеет адресный 16 и информационный 17 входы, вход 18 сброса, вход 19 режима работы, вход 20 пуска, первый 21, второй 22, третий 23 и четвертый 24 входы записи и индикаторный выход 25.

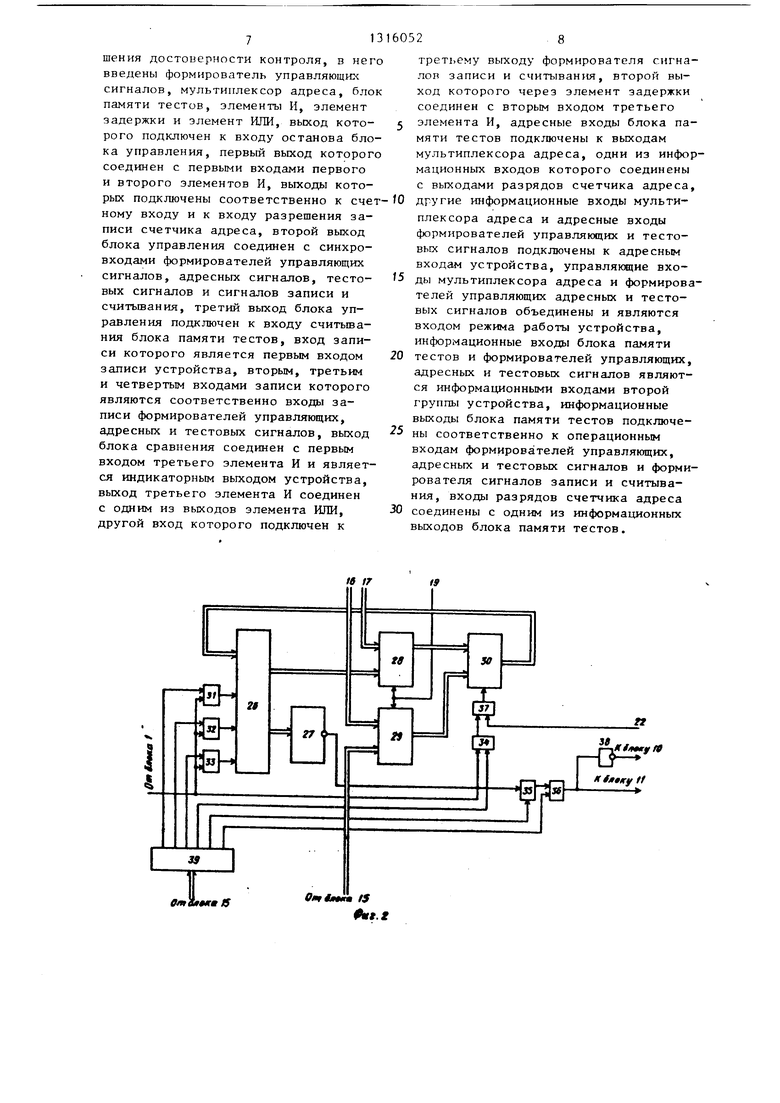

Формирователь 2 управляющих сигналов содержит (фиг. 2) счетчик 26, элемент И-НЕ 27, мультиплексор 28 информации, мультиплексор 29 адреса, буферное запоминающее устройство (ЗУ) 30, первый 31, второй 32, третий 33, четвертый 34 и пятый 35 элементы И, первый 36 и второй 37 элементы ИЛИ, элемент НЕ 38 и дешифратор 39.

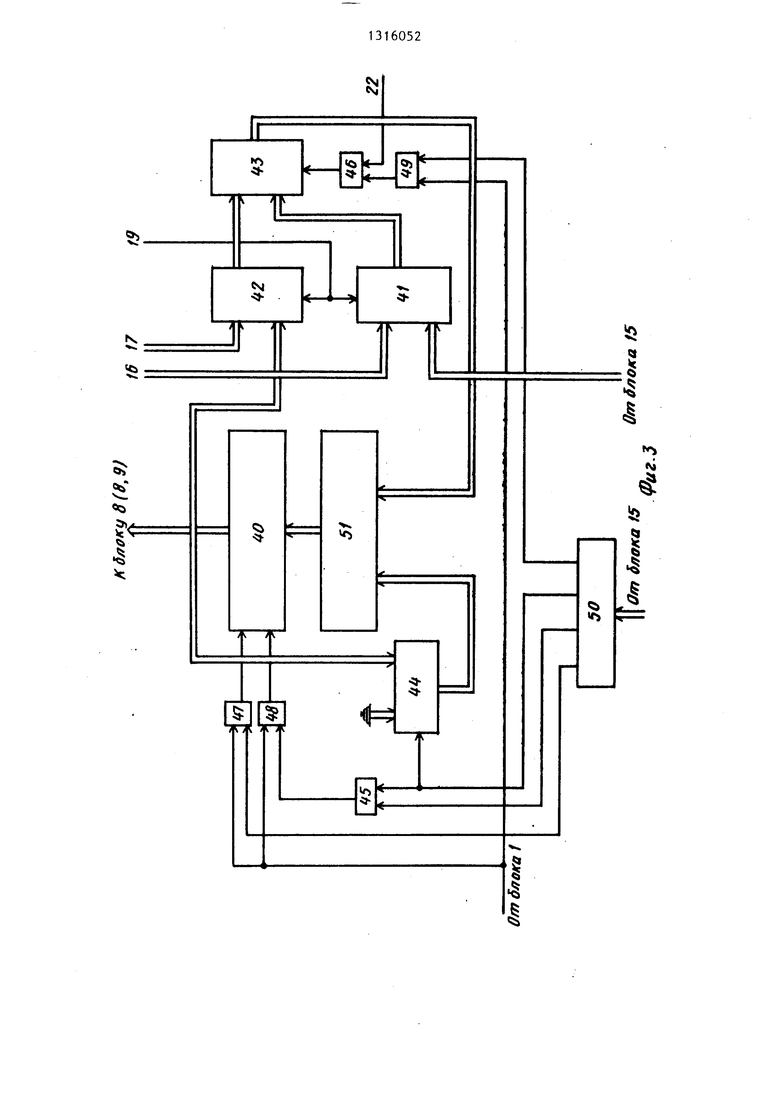

Формирователь 4 тестовых сиг налов (фиг. 3) содержит счетчик 40, мультиплексор 41 адреса, мультиплексор 42 информации, буферное запоминающее устройство 43, мультиплексор 44 операнда, первый 45 и второй 46 элементы ИЛИ, первый 47, второй 48 и третий 49 элементы И, дешифратор 50 и сумматор 51. Формирователь 3 адресных сигналов выполнен по схеме, аналогичной схеме формирователя 4.

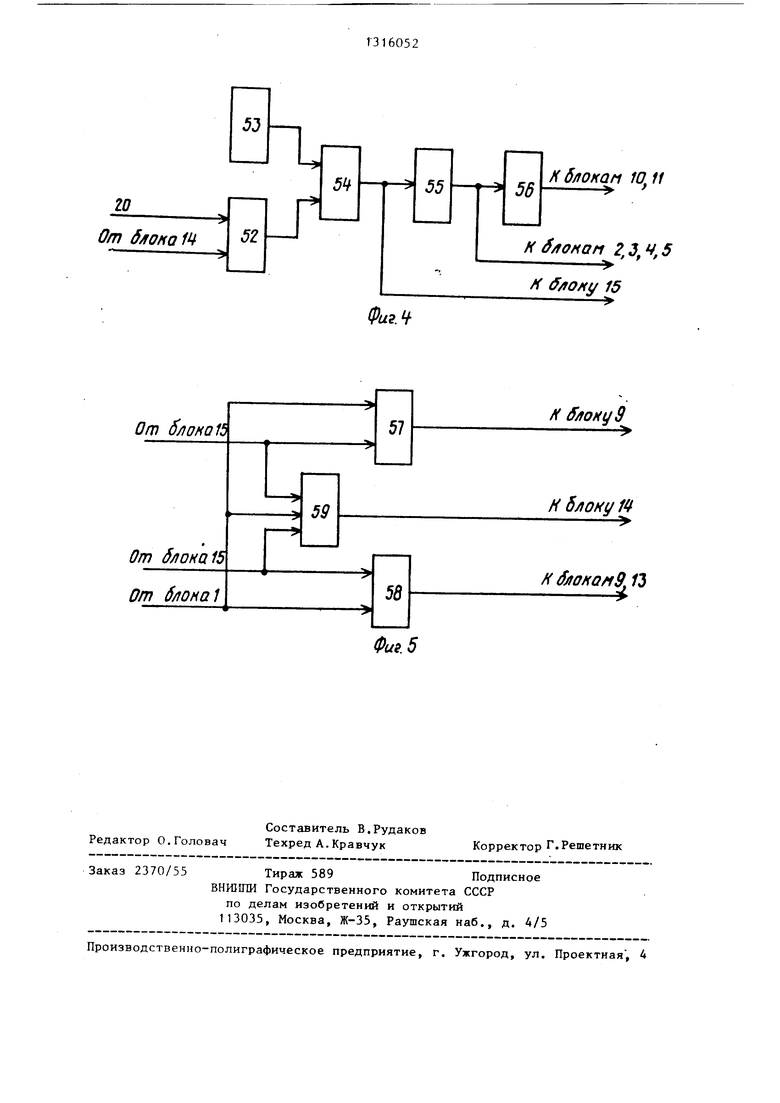

Блок 1 управления (фиг. 4) содержит триггер 52, генератор 53 имиуль22

сов, элемент И 54 и первый 55 и второй 56 элементы -задержки.

Формирователь 5 сигналов записи м считывания (фиг. 5) содержит первый 57, второй 58 и третий 59 элементы И.

Устройство работает следующим образом.

В подготовительном режиме на

вход 19 устройства подается высокий потенциал, который поступает на управляющие входы мультиплексора 7 ад-, реса и формирователей 2-4.

Мультиплексоры 7, 28, 29, 41 и 42

устроены так, что при высоком уровне на их управляющих входах выходы мультиплексоров повторяют информацию одной группы входов, а при низком уровне другой.

Таким образом, в подготовительном режиме код, поданный на вход 16, через мультиплексор 7 поступает на 1адресные входы блока 15, через мультиплексор 29 на адресные входы буферного ЗУ 30 и через мультиплексоры 41 на адресные входы буферных ЗУ 43 формирователей 3 и 4.

Аналогично код, поданный на вход 17 устройства, поступает на информационные входы блока 15, через мультиплексор 28 на информационные входы буферного ЗУ 30 и через мультиплексоры 42 на информационные входы буферных ЗУ 43.

Для записи информации в блок 15 на вход 21 записи надо подать положительный импульс.

Для записи информации в буферное ЗУ 30 импульс надо подавать по входу 22 записи, который, пройдя через элемент 1ШИ 37, записьшает соответствующую информацию.

Для записи информации в буферное ЗУ 43 формирователя 3 надо подавать импульс по входу 23 записи, который, пройдя через элемент ИЛИ 46, записывает информацию в буферное ЗУ 43.

Аналогично записьшается информация в буферное ЗУ 43 формирователя 4, только в этом случае импульс необходимо подавать по входу 24 записи.

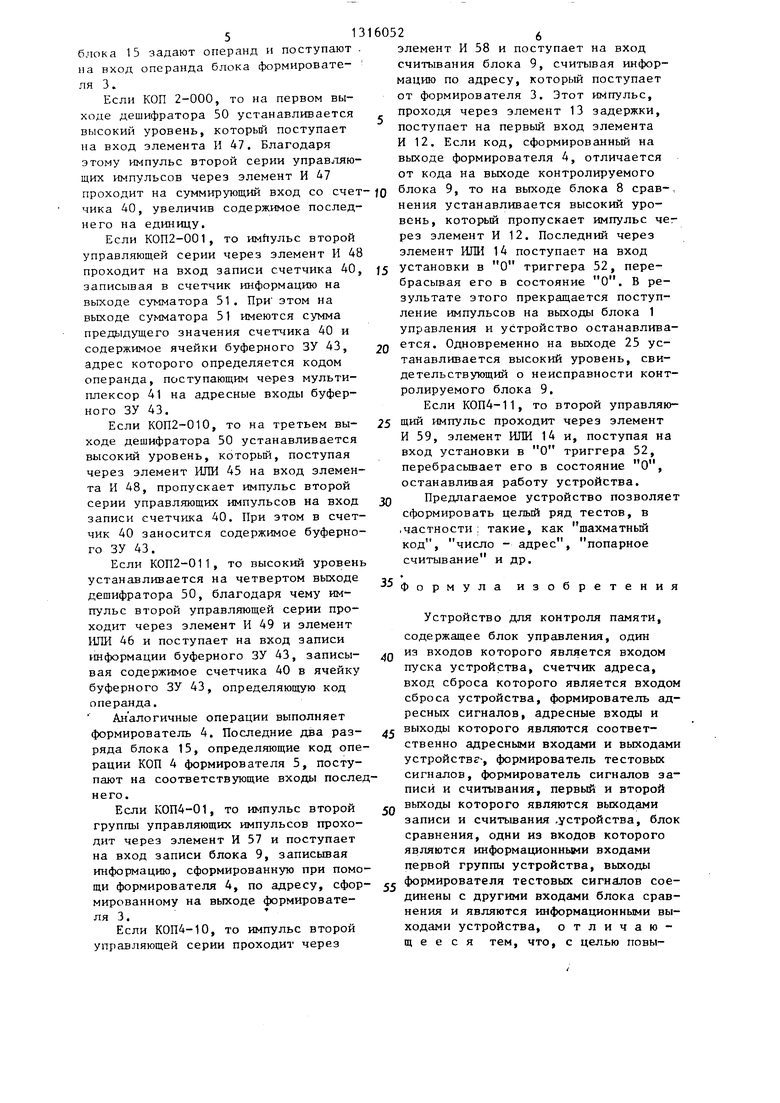

Для перевода устройства в рабо- чий режим надо сначала установить счетчик 6 гщреса в нулевое состояние подачей импульса по входу 18 сброса, после чего подать импульс на вход 20, который, поступив на блок 1 уп31

равления, устанавливает триггер 52 в единичное состояние, благодаря чему тактовые импульсы генератора 53 через элемент И 54 поступают на первый выход блока 1 управления и на вход первого элемента 55 задержки. Сигнал с выхода последнего поступает на вход второго элемента 56 задержки и на второй выход блока 1 управления, а с выхода второго элемента 56 задержки на третий выход блока 1 управления. Таким образом, на выходах блока 1 управления формируются три управляющие серии импульсов, причем вторая серия управляющих импульсов задержана относительно первой, а третья относительно второй.

Первый импульс первой серии управляющих импульсов поступает на вход считывания информации блока 15, в результате чего на его выходе устанавливается информация, записанная по ее нулевому адресу.

Первые три разряда информационного слова блока 15 поступают на вход кода операции формирователя 2 и определяют его код операции (KOni) Следующие разряды блока 15, определяющие операнд, поступают на вход операнда формирователя 2.

Выходы кода операции поступают на входы дешифратора 39.

Если КОП 1-000, то на первом выходе дешифратора 39 устанавливается высокий уровень, благодаря чему импульс из второй серии управляющих импульсов с второго выхода блока 1 управления проходит через элемент И 31 на вычитающий вход счетчика 26, в результате чего содержимое последнего уменьшается на единицу.

Если КОП1-001, то высокий уровень устанавливается на втором выходе дешифратора 39, благодаря чему импульс из второй серии управляющих импульсов с второго выхода блока 1 проходит чрез элемент И 32 на вход записи информации счетчика 26. При этом код операнда формирователя 2 через мультиплексор 29 проходит на его выходы и далее на адресные входы буферного ЗУ 30. В это время на выходе элемента ИЛИ 37 имеется низкий уровень, следовательно, буферное ЗУ 30 находится в режиме считывания, поэтому на его вьгходах устанавливается информация, содержащаяся по адресу, заданному операндом.

524

Если КОП1-010, то высокий уровень устанавливается на третьем выходе дешифратора 39, благодаря чему им- гп, льс из второй серии управляющих импульсов с второго выхода блока 1, пройдя через элемент И 33, поступает на суммирующий вход счетчика 26, увеличив его содержимое на единицу. Если КОП1-011, то высокий уровень устанавливается на четвертом вьсходе дешифратора 39, благодаря чему импульс из второй серии управляющих им1тульсов, пройдя через элемент И 34 и элемент ИЛИ 37, записывает

содержимое счетчика 26 в буферное ЗУ 30 по адресу кода операнда.

Если КОП1-100, то высокий уровень устанавливается на пятом выходе дешифратора 39. Если содержимое счетчика 26 не равно нулю, то на выходе элемента И-НЕ 27, устанавл шается высокий уровень, который, пройдя через элемент И 35, устанавливает высокий уровень на входе элемента

И 11. При этом импульс из третьей серии управляющих импульсов, пройдя через элемент И 11, поступает на вход записи счетчика 6, записывая в него код операнда. Этот код в данном случае является адресом перехода и определяет адрес следующего обращения к блоку 15.

Если на выходе элемента И-НЕ 27 устанавливается низкий уровень (содержимое счетчика 26 равно нул1о), то на выходе элемента НЕ 38 устанавливается высокий уровень, который открывает первый элемент И 10. Импульс из третьей серии управляющих

имгт льсов, пройдя через элемент И 10, поступает на суммирующий вход счетчика 6, увеличив его содержимое на единицу, формируя адрес следующего обращения блоку 15.

Если КОП1-101, то на шестом выходе дешифратора 39 устанавливается высокий уровень, который поступает на вход элемента И 11. Благодаря этому импульс второй серии управляющих

импульсов проходит через элемент И 11 и поступает на вход записи счетчика 6, записьшая в него код адреса перехода. Мнемоническое обозначение операции следящего блока с кодом операции 101-БПК.

Очередные три разряда блока 15 определяют код операции КОП 2 формирователя 3 и поступают на его входы кода операции. Следующие разряды

51

блока 15 задают операнд и поступают па вход операнда блока формирователя 3 .

Если КОП 2-000, то на первом выходе дешифратора 50 устанавливается высокий уровень, которьш поступает на вход элемента И 47. Благодаря этому импульс второй серии управляющих импульсов через элемент И 47 проходит на суммирующий вход со счетчика 40, увеличив содержимое последнего на единицу.

Если КОП2-001, то имйульс второй управляющей серии через элемент И 48 проходит на вход записи счетчика 40, записывая в счетчик информацию на выходе сумматора 51. При этом на выходе сумматора 51 имеются сумма предыдущего значения счетчика 40 и содержимое ячейки буферного ЗУ 43, адрес которого определяется кодом операнда, поступающим через мультиплексор 41 на адресные входы буферного ЗУ 43.

Если КОП2-010, то на третьем выходе дешифратора 50 устанавливается высокий уровень, который, поступая через элемент ИЛИ 45 на вход элемента И 48, пропускает импульс второй серии управляющих импульсов на вход записи счетчика 40. При этом в счетчик 40 заносится содержимое буферного ЗУ 43.

Если КОП2-011, то высокий уровень устанавливается на четвертом выходе дешифратора 50, благодаря чему импульс второй управляющей серии проходит через элемент И 49 и элемент ИЛИ 46 и поступает на вход записи fflфopмaции буферного ЗУ 43, записывая содержимое счетчика 40 в ячейку буферного ЗУ 43, определяющую код операнда.

Аналогичные операции выполняет формирователь 4. Последние два разряда блока 15, определяющие код операции КОП 4 формирователя 5, поступают на соответствующие входы после него.

Если КОП4-01, то импульс второй группы управляющих импульсов проходит через элемент И 57 и поступает на вход записи блока 9, записывая информацию, сформированную при помощи формирователя 4, по адресу, сформированному на выходе формирователя 3.

Если КОП4-10, то импульс второй управляющей серии проходит через

60526

элемент И 58 и поступает на вход считывания блока 9, считывая информацию по адресу, который поступает от формирователя 3. Этот импульс, проходя через элемент 13 задержки, поступает на первый вход элемента И 12. Если код, сформированный на выходе формирователя 4, отличается от кода на выходе контролируемого JQ блока 9, то на выходе блока 8 срав-, нения устанавливается высокий уровень, который пропускает импульс чег рез элемент И 12. Последний через элемент ИЛИ 14 поступает на вход

J5 установки в О триггера 52, перебрасывая его в состояние О. В результате этого прекращается поступление импульсов на выходы блока 1 управления и устройство останавлива2Q ется. Одновременно на выходе 25 устанавливается высокий уровень, свидетельствующий о неисправности контролируемого блока 9.

Если КОП4-11, то второй управляю25 Щий импульс проходит через элемент И 59, элемент ИЛИ 14 и, поступая на вход установки в О триггера 52, перебрасьшает его в состояние О, останавливая работу устройства.

jQ Предлагаемое устройство позволяет сформировать целый ряд тестов, в .частности : такие, как шахматный

код, число - адрес, попарное считывание и др.

35

Формула изобретения

Устройство для контроля памяти, содержащее блок управления, один

из входов которого является входом пуска устройства, счетчик адреса, вход сброса которого является входом сброса устройства, формирователь адресных сигналов, адресные входы и

выходы которого являются соответственно адресными входами и выходами устройстве-, формирователь тестовых сигналов, формирователь сигналов записи и считывания, первый и второй

выходы которого являются выходами записи и считьшания .устройства, блок сравнения, одни из входов которого являются информационными входами первой группы устройства, выходы

формирователя тестовых сигналов соединены с другими входами блока сравнения и являются информационными выходами устройства, отличающееся тем, что, с целью повы713

шения достоверности контроля, в него введены формирователь управляющих сигналов, мультиплексор адреса, блок памяти тестов, элементы И, элемент задержки и элемент ИЛИ, выход которого подключен к входу останова блока управления, первый выход которого соединен с первыми входами первого и второго элементов И, выходы которых подключены соответственно к счет ному входу и к входу разрешения записи счетчика адреса, второй выход блока управления соединен с синхро- входами формирователей управляющих сигналов, адресных сигналов, тестовых сигналов и сигналов записи и считьшания, третий выход блока управления подключен к входу считьшания блока памяти тестов, вход записи которого является первым входом записи устройства, вторым, третьим и четвертым входами записи которого являются соответственно входы записи формирователей управляющих, адресных и тестовых сигналов, выход блока сравнения соединен с первым входом третьего элемента И и является индикаторным выходом устройства, выход третьего элемента И соединен с одним из выходов элемента ИЛИ, другой вход которого подключен к

60528

третьему выходу формирователя сигналов записи и считывания, второй выход которого через элемент задержки соединен с вторым входом третьего

5 элемента И, адресные входы блока памяти тестов подключены к выходам мультиплексора адреса, одни из информационных входов которого соединены с выходами разрядов счетчика адреса, fO другие информационные входы мультиплексора адреса и адресные входы формирователей управляющих и тестовых сигналов подключены к адресным входам устройства, управляющие вхо 5 ды мультиплексора адреса и формирователей управляющих адресных и тестовых сигналов объединены и являются входом режима работы устройства, информационные входы блока памяти тестов и формирователей управляющих, адресных и тестовых сигналов являются информационными входами второй группы устройства, информационные вьгходы блока памяти тестов подключены соответственно к операционным входам формирователей управляющих, адресных и тестовых сигналов и формирователя сигналов записи и считывания, входы разрядов счетчика адреса

30 соединены с одним из информационных выходов блока памяти тестов.

20

25

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый контроллер | 1981 |

|

SU1001012A1 |

| Программируемый контроллер | 1987 |

|

SU1448338A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2012924C1 |

| Устройство для вычисления скользящего спектра | 1983 |

|

SU1095188A1 |

| Устройство управления конвейерным вычислительным устройством | 1991 |

|

SU1751757A1 |

| Устройство для тестового контроля блоков памяти | 1988 |

|

SU1541678A1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

Изобретение относится к вычислительной технике, в частности к устройствам для контроля блоков памяти. Цель изобретения - повышение достоверности контроля. Устройство содержит блок 1 управления, формирователь 2 управляющих сигналов, формирователь 3 адресных сигналов, формирователь 4 тестовых сигналов, формирователь 5 сигналов записи и счи- тьшания, счетчик 6 адреса, мультиплексор 7 адреса, блок 8 сравнения, элементы И 10-12, элемент 13 задержки, элемент И 14 и блок 15 памяти тестов. В устройстве реализована аппаратно-программная организация тестов. 5 ил. 18 i (Л со О5 о ел ГС

I I

Jf//reffff

ffMt,

rf/reff

fS

Alt. г

5

От 6/1 о f a ff

52

Редактор О.Головач

Составитель В.Рудаков Техред А.Кравчук

Заказ 2370/55 Тираж 589Подписное

ВНЮШИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная , 4

55

56

К 6/1окам W, 11 f

КS/fOf afi 2,3,5

/Г /гому 15

Фиг.ЧФи.б

Корректор Г.Решетник

| Электронная промьшшенность, 1975, № 8, с | |||

| Парный автоматический сцепной прибор для железнодорожных вагонов | 0 |

|

SU78A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

Авторы

Даты

1987-06-07—Публикация

1985-10-10—Подача