Изобретение относится к радиотехнике и связи и может быть использовано для измерения фазовых характерйстик сигналов.

Цель изобретения - повьшение точности умножения частоты.

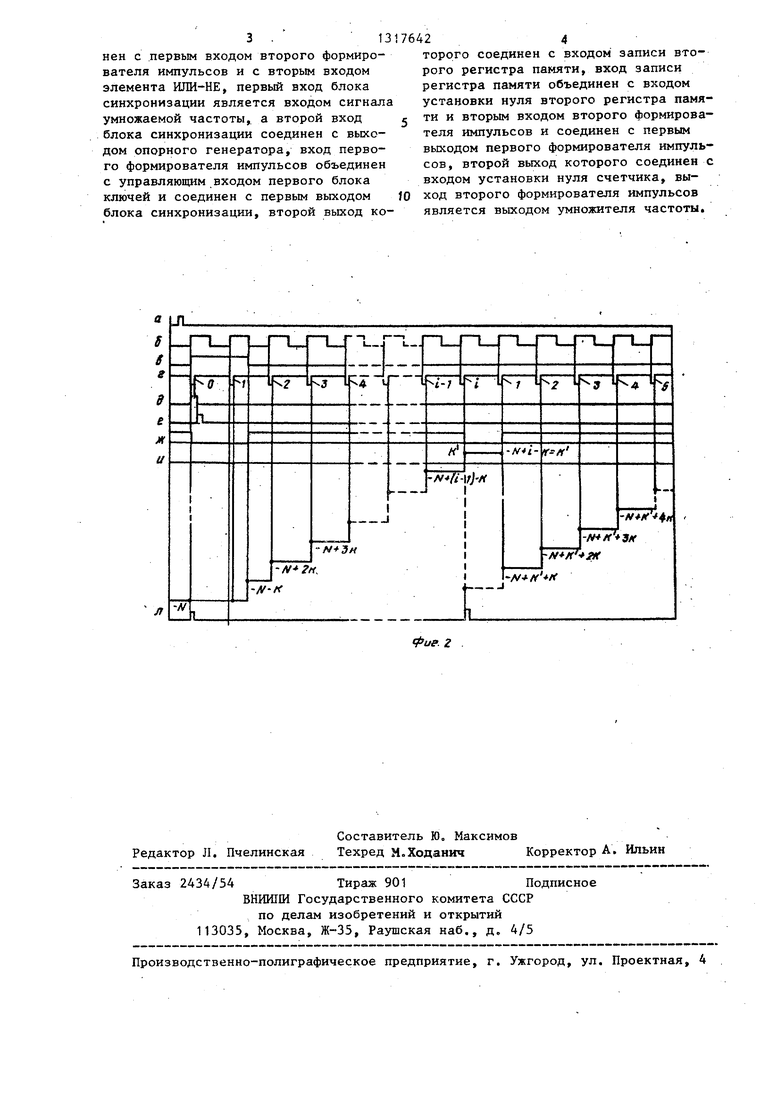

На фиг. Т представлена функциональная схема умножителя частоты, а на фиг. 2 - временные диаграммы, поясняющие его работу,

Умножитель частоты содержит блок 1 синхронизации, первый формирователь 2 импульсов, опорный генератор 3, счетчик 4, первый 5 и второй 6 регистры памяти, первый 7 и второй 8 блоки ключей, первый 9 и второй 10 сумматоры, блок 11 набора коэффициентов умножения, элемент ИЛИ-НЕ 12 и второй формирователь 13 импульсов,

Умножитель частоты работает следующим образом.

На первый вход блока 1 синхронизации поступает входной сигнал в виде периодической последовательности импульсов (фиг. 2а). При поступлении очередного импульса входного сигнала (на первом выходе блока синхронизации формируется управляющий импульс (фиг. 2в), длительность которого равна 1,5 периода следования импульсов с выхода опорного генератора 3 (фиг. 26). На втором выходе блока 1 синхронизации формируется последовательность коротких импульсов (фиг. 2г) Первый формирователь 2 по фронту управляющего импульса (фиг. 2в) формирует (на первом входе) первый импульс (фиг. 2д) и с некоторой задержкой (на втором выходе) второй импульс (фиг, 2е), который устанавливает счетчик 4 в ноль. Результат измерения предыдущего периода входного сигнала в виде двоичного кода числа - N (с выхода счетчика 4) по первому импульсу (с выхода первого формирователя 2) переписывается в первьй регистр 5. Одновременно второй регистр 6 устанавливается в ноль и на выходе второго формирователя 13 появляется импульс (фиг. 2л) выходного сигнала. Управляющий импульс (фиг. 2в) закрывает первый блок ключей 7 и поступает на первый вход элемента ШШ-НЕ 12, с выхода которого инвертированный управляющий импульс (фиг. 2ж) открьшает второй блок 8 ключей. Двоичный код числа - N через второй блок 8 ключей и второй сумматор 10 поступает на информационньй вход второго регистра 6 и записывается в него с приходом очередного импульса на вход записи (фиг. 2г). На выходе первого сумматора 9 устанавливается двоичный код числа - N (фиг. 2и). По срезу управляющего импульса первый блок 7 ключей открывается, а второй блок 8 ключей закрывается. Двоичный код числа К (где К - коэффициент умножения умножителя частоты) с выхода блока 11 поступает на первьй вход первого сумматора 9, на выходе которого устанавливается двоичный код числа - N+K. Совместно блоки 6,9 и

10 работают как накапливающий сумматор до появления на выходе переноса первого сумматора 9 сигнала 1, который поступает на второй вход элемента ИЛИ-НЕ 12 и второй.вход второго формирователя 13. На выходе второго формирователя 13 появляется очередной импульс выходного сигнала (фиг. 2я), второй блок ключей 5 открывается и двоичный код числа - К

поступает на второй вход второго сумматора 10. После записи суммы - N+K во второй регистр 6 на выходе переноса первого сумматора 9 устанавливается О и второй блок 8 ключей закрывается. Снова блоки 6,9 и 10 работают в режиме накапливающего сумматора, но начальное значение суммы изменяется на величину остатка от предьщуще- го накопления, что необходимо для точного формирования выходного сигнала. Одновременно производится измерение текущего периода входного сигнала с помощью опорного генератора 3 и счетчика 4.

Формула изобретения

Умножитель частоты, содержащий последовательно соединенные опорный генератор и счетчик, первый и второй

регистры памяти, первый и второй фор- мИров атели импульсов, о т л и ч а ю- щ и и с я тем, что, с целью повыше ния точности умножения частоты, введены последовательно соединенные блок

набора коэффидаентов умножения, первый блок ключей, первый сумматор и второй сумматор, последовательно соединенные блок синхронизации, элемент ИЛИ-НЕ и второй блок ключей, информационный вход которого соединен с выходом первого регистра памяти, а выход второго блока ключей соединен с вторым входом второго сумматора, выход переноса первого сумматора соеди3 . 13

нен с .первым входом второго формирователя импульсов и с вторым входом элемента ИЛИ-НЕ, первый вход блока синхронизации является входом сигнала умножаемой частоты, а второй вход блока синхронизации соединен с выходом опорного генератора, вход первого формирователя импульсов объединен с управляющим входом первого блока ключей и соединен с первым выходом блока синхронизации, второй выход коРедактор Л. Пчелинская

Составитель Ю. Максимов

Техред М.Ходанич Корректор А. Ильин

Заказ 2434/54Тираж 901Подписное

ВНИИ1Ш Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

176424

торрго соединен с входом записи второго регистра памяти, вход записи регистра памяти объединен с входом установки нуля второго регистра памяс ти и вторым входом второго формирователя импульсов и соединен с первым выходом первого формирователя импульсов, второй выход которого соединен с входом установки нуля счетчика, вы}0 ход второго формирователя импульсов является выходом умножителя частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Цифровой коррелятор | 1982 |

|

SU1073776A1 |

| Дискретный умножитель частоты | 1985 |

|

SU1337988A1 |

| Преобразователь активной мощности в цифровой код | 1986 |

|

SU1366960A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| Умножитель частоты | 1988 |

|

SU1608779A1 |

| Режекторный фильтр | 1987 |

|

SU1429293A2 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Умножитель частоты | 1979 |

|

SU807322A1 |

| Преобразователь частоты следования импульсов в код | 1991 |

|

SU1780037A1 |

Изобретение относится к радиотехнике и связи. Цель изобретения - повышение точности умножения частоты. Bx.f Умножитель частоты содержит блок синхронизации 1, формирователи 2 и 13 импульсов, опорный г-р 3, счетчик 4, регистры 5 и 6 памяти, блоки ключей 7 и 8, сумматоры 9 и 10, блок набора 11 коэф. умножения и .эл-т ИЛИ-НЕ 12, В результате работы регистра 6 и сумматоров 9 и 10 в режиме накапливающего сумматора в данном устройстве осуществляется изменение начального значения суммы чисел на величину остатка от предьщущего накопления, что необходимо для более точного формирования выходного сигнала. Цель достигается введением блока синхронизации 1, блоков ключей 7 и 8, сумматоров 9 и 10, блока набора 11 и зл-та 12. 2 Ш1. 0U2.f

| Умножитель частоты следования импульсов | 1981 |

|

SU966848A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Умножитель частоты следования импульсов | 1982 |

|

SU1018190A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-06-15—Публикация

1985-12-12—Подача