1

Изобретение относится к автоматическому управлению и регулированию и может быть использовано для управления электрическим напряжением, током, температурой, скоростью враще- ния электродвигателя и другими физическими и технологическими параметрами при решении различных технических задач.

Цель изобретения - повышение точ- ности и быстродействия,

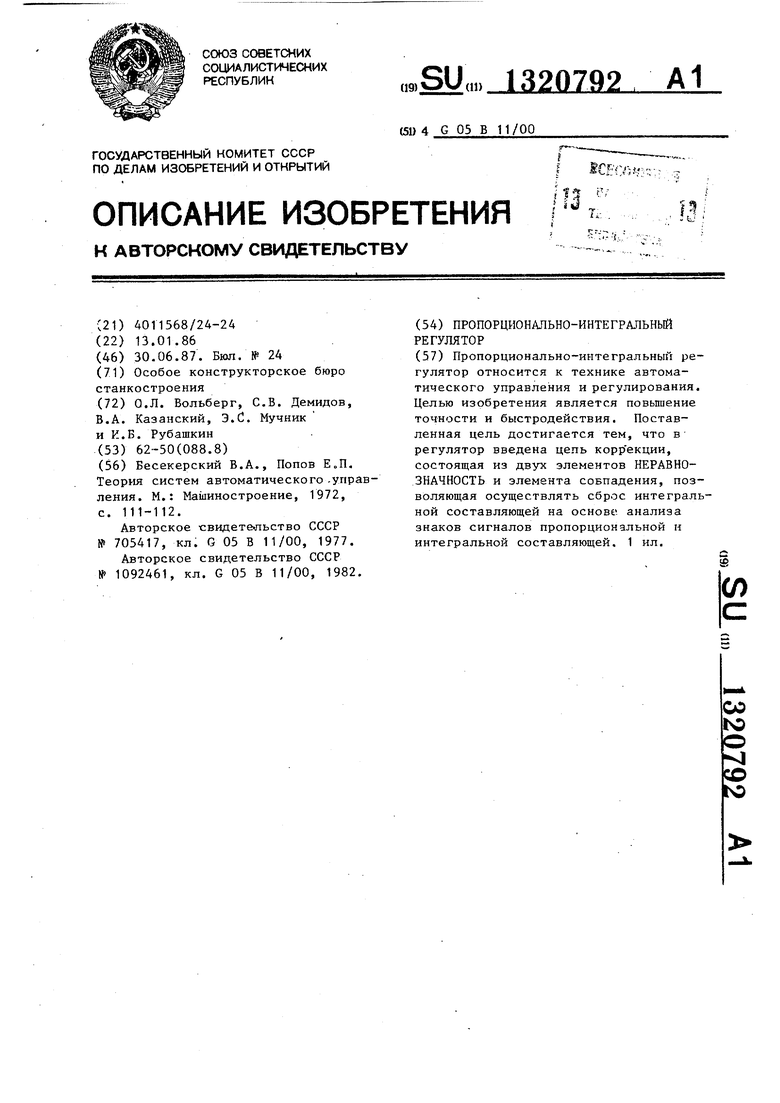

На чертеже изображена блок-схема предлагаемого регулятора.

Пропорционально-интегральный регулятор 1 содержит блок 2 вычитания, интегратор 3, имеющий вход 4 Установка, сумматор 5, выходные шины знака 6 и модуля 7 блока вычитания, первьш 8 и второй 9 элементы НЕРАВНОЗНАЧНОСТЬ, элемент 10 совпадения, выходные шины знака 11 и модуля 12 интегратора, входные шины знака 13 и модуля 14 первого входа пропор- ционально-интегр ального регулятора, выходные шины знака 15 и модуля 16 пропордионально-интегрального регулятора, объект 17 регулирования, входные шины знака 18 и модуля 19 второго входа пропорционально-интегрального регулятора, блок 20 управления, состоящий, например, из генератора 2 тактовых импульсов и распределителя импульсов 22, имеющего выходы 23-25

Интегратор 3 может быть реализован в виде любого известного цифрового параллельного сумматора-накопителя с цифровыми входами (шины 6 и 7) и цифровым выходом (шины 11 и 12) на интегральных схемах, например, серии К555, К531, К155.

Блок 2 может быть реализован в виде любого известного цифрового параллельного реверсивного сумматора с двумя цифровыми входами (шины 13, 14 и 18, 19) на интегральных схемах, например К155 ИМЗ.

Сумматор 5 может быть реализован Б виде Известного цифрового параллельного сумматора с двумя цифровыми входами (шины 6, 7 и 11,12) и цифровым выходом (шины 15 и 16) на интегральных схемах К155 ИМЗ.

Элементы 8 и 9 реализованы на микросхеме К155 ЛП5. Элемент 10 может

быть реализован на микросхеме К155 ЛИ1. Устройство работает следующим образом,

Предположим, что на выход регулятора 1 в момент дискретного времени t; подается входной сигнал V(t;), который по шинам 13 и 14 поступает на первый вход (уменьшаемого) блока 2, На второй вход вычитаемого блока 2 по шинам 18 и 19 поступает сигнал Y(t;;) обратной связи. Этого сигнал блока 2 вычитается из- входных сигналов задания, в результате чего на его выходе на шинах 6 и 7 образуется разностный сигнал рассогласования

uY(t.) V(t; )-Y(t;),

Этот сигнал по шинам 6 и 7 подается на вход цифрового параллельного сумматора-накопителя (интегратора) 3 и на вход цифрового параллельного сумматора 5.

Генератор 21 импульсов вырабатывает импульсы с частотой F, которые поступают на вход распределителя 22 импульсов. Последний циклически на своих выходах 23-25 вырабатывает последовательно по выходам тактовые импульсы стробирования. При этом первьй импульс с выхода 23 стробиру- ет цифровой параллельный сумматорнакопитель (интегратор 3), второй импульс с выхода 24 стробирует элемент 10, третий импульс с выхода 25 стробирует сумматор 5, формируя в момент строба на его выходе суммарный

сигнал управления S(t}), При подаче каждого стробирующего импульса п-раз- рядное число fiy(t;) на входе 6 и 7 ... цифрового параллельного сумматора- накопителя суммируется с его содержимым, В результате при непрерывном поступлении стробирующих импульсов в цифровом сумматоре-накопителе 3 образуется сумма числовьгх значений входного сигнала

Z:K AY(t.) + с, t;-0

где С - начальное число в блоке 3;

К - коэффициент,

в данном случае определяемый частотой стробирования, ртносительным сдвигом разрядов параллельных чисел, формируемых на параллельных шинах 7 модуля сигнала uY(t;) при подключении к параллельному входу сумматора- накопителя.

Если С О, то сумма будет иметь вид:

Z:K &Y(t.).

i-,-0

Эта сумма является дискретной реализацией интеграла- входного сигнала t

J KuY(t)J

t-.

При динамических изменениях, например, связанных с уменьшением нагрузпропорциональгде с. - время в непрерывном отсчете.

По шинам 11 и 12 с выхода цифрово-jg го параллельного сумматора-накопителя (блок 3) сигналы поступают на входы первого слагаемого цифрового сумматора 5, на входы второго слагаемого которого по шинам 6 и 7 подаются сигна- (5 водит к изменению знака и интегральной лы с выхода цифрового блока 2

ки или с торможением, ная составляющая n(t;) изменяет знак на обратный на более длительный период. При более глубоком торможении длительное изменение знака n(t,-) привычитания сигналов обратной связи. Сумматор 5 алгебраически (с учетом знака слагаемых) суммирует результат интегрирования с результатом вычитания и на шинах 15 и 16 его выхода образуется пропорционально-интегральный сигнал управления

t S(t) K.uYCt; ) + К, Ц KAY(t,).

Ч;-0

При этом пропорциональная составляющая сигнала управления

составляющей сигнала управления, U(t.) . В результате торможение приобретает интенсивный характер.

В один из моментов времени t регу20 лируемый параметр частоты вращения электродвигателя достигает заданной величины, что немедленно фиксирует сигнал пропорциональной составляющей, изменяя свой знак на знак, соответ25 ствующий знаку сигнала задания. В этот момент времени получается (естественным .образом) совершенно неправильная ситуация работы регулятора. Параметр в норме, пропорциональная

.n(t;) К, U Y(t.).

Интегральная составляющая сигнала управления

U(t;) Kj i: KAY(t;).

Коэффициенты К, К , К определяются и задаются конкретной техической реализацией устройства.

Сигнал управления S(t) по шинам 15 и 16 подается на вход объекта 17 управления.

При работе в статическом режиме, например по поддержанию скорости вращения электродвигателя, интегральная 5 тегрирования со знаком сигнала резуль- составляющая U(t.) имеет знак, соответствующий знаку сигнала задания. Например, при знаке сигнала задания + (сигнал О на шине 13) U(i:.) имеет + (сигнал О на шине 11), а при знаке сигнала задания - (сиг- 1 на шине 13) имеет - (сигна шине 11). При этом по аб50

нал

нал 1

солютному значению сигнал результата интегрирования имеет относительные изменения достаточно плавного характера.

Пропорциональная составляющая n(t , ) при перерегулировании изменяет

55

тата вычитания.

Сигналы с выхода шин 13 знаков сигнала задания и шин 11 знаков интегральной составляющей поступают на входы элемента 9, который на своем в ыходе образует логическую функцию 13-1IV 13-11, фиксируя несоответствие знака сигнала результата интегрирования со знаком сигнала задания.

Выходы элементов 8 и 9 включены на входы-элемента 10, третий вход которого включен на выход 24 распределителя 22 импульсов,вырабатывающего

320792;4

знак на противоположный знаку сигнала задания. Например, при знаке сигнала задания + (сигнал О на шине 13) n(t;) имеет - (сигнал 1 на шине 6), а при знаке сигнала задания - (сигнал 1 на шине 13) имеет + (сигнал О на шине 6).

При динамических изменениях, например, связанных с уменьшением нагрузпропорциональе.

-jg я - (5 водит к изменению знака и интегральной

ки или с торможением, ная составляющая n(t;) изменяет знак на обратный на более длительный период. При более глубоком торможении длительное изменение знака n(t,-) приjg(5 водит к изменению знака и интегральной

составляющей сигнала управления, U(t.) . В результате торможение приобретает интенсивный характер.

В один из моментов времени t регу0 лируемый параметр частоты вращения электродвигателя достигает заданной величины, что немедленно фиксирует сигнал пропорциональной составляющей, изменяя свой знак на знак, соответ5 ствующий знаку сигнала задания. В этот момент времени получается (естественным .образом) совершенно неправильная ситуация работы регулятора. Параметр в норме, пропорциональная

0 составляющая это-идентифицирует, а интегральная составляющая U(t;) в силу инерционности рырабатывает сигнал с обратным знаком управления, не соответствующим по направлению требуе5 мому воз действиюс

Для ликвидации несоответствия и улучшения динамических характеристик сигналы с выхода шин 6 знаков пропорциональной составляющей и шин 11

0 знаков интегральной составляющей поступают на входы элемента 8, который на своем вькоде образует логическую функцию V6 11, фиксируя несоответствие знака сигнала результата интегрирования со знаком сигнала резуль-

тата вычитания.

Сигналы с выхода шин 13 знаков сигнала задания и шин 11 знаков интегральной составляющей поступают на входы элемента 9, который на своем в ыходе образует логическую функцию 13-1IV 13-11, фиксируя несоответствие знака сигнала результата интегрирования со знаком сигнала задания.

Выходы элементов 8 и 9 включены на входы-элемента 10, третий вход которого включен на выход 24 распределителя 22 импульсов,вырабатывающего

на этом выходе второй импульс стро- бирования. В момент строба реализуется логическая функция

(13 Л V il -11) (6-П V 6-11),

в результате чего появление импульса на выходе элемента 10 фиксирует момент несоответствия знака сигнала результата интегрирования со знаком сиг-tO тора, выходные шины знака и модуля

нала задания и одновременно со знаком сигнала результата вычитания. Выход элемента 10 включен на вход 4 установки цифрового параллельного сумматоранакопителя. Поэтому в момент возник- J5 целью повышения точности и быстродейновения сигнала несоответствия, который вырабатывает элемент 10, этим сигналом цифровой интегратор 3 Устанавливается в нулевое состояние, т.е. заменяется сигнал результата интегрирования на другой исходньй сигнал (в данном случае нулевой), начиная с которого далее интегрируют результат вычитания. .

Формула изобретения

25 рого элементов НЕРАВНОЗНАЧНОСТЬ соединены с выходной шиной знака интегратора, выходы первого и второго эл ментов НЕРАВНОЗНАЧНОСТЬ связаны соответственно с первым и вторым вхоПропорционально-интегральньй регулятор, содержащий блок вычитания, интегратор и сумматор, причем шина зна- 30 дами элемента совпадения, выход кока и шина модуля первой группы вхо- торого подключен к входу Установка дов блока вычитания соединены с соответствующими шинами первой группы входов пропорционально-интегральноинтегратора, первый, второй и третий выходы распределителя импульсов связаны соответственно с тактовым

го регулятора, шина знака и шина мо- входом интегратора, третьим входом дуля второй группы входов блока вычи- элементов совпадения и тактовым тания подключены к соответствующим входом сумматора.

шинам второй группы входов пропорционально-интегрального регулятора, выходные шины знака и модуля блока вычитания подсоединены к соответствующим шинам интегратора и соответствующим шинам первой группы входов сумматора, у которого шины знака и модуля второй группы входов подключены к соответствующим выходным шинам инте грасумматора соединены с соответствующими выходными шинами пропорционально-интегрального регулятора от- личающийся тем, что, с

ствия, в него введены два элемента . НЕРАВНОЗНАЧНОСТЬ, элемент СОВПАДЕНИЯ, блок управления, первый вход первого элемента НЕРАВНОЗНАЧНОСТЬ подключен

к выходной шине знака блока вычитания, первый вход второго элемента НЕРАВНОЗНАЧНОСТЬ соединен с шиной знака первой группы входов блока вычитания, вторые входы первого и второго элементов НЕРАВНОЗНАЧНОСТЬ соединены с выходной шиной знака интегратора, выходы первого и второго элементов НЕРАВНОЗНАЧНОСТЬ связаны соответственно с первым и вторым входами элемента совпадения, выход которого подключен к входу Установка

дами элемента совпадения, выход которого подключен к входу Установка

интегратора, первый, второй и третий выходы распределителя импульсов связаны соответственно с тактовым

| название | год | авторы | номер документа |

|---|---|---|---|

| Пропорционально-интегральный регулятор | 1988 |

|

SU1566318A1 |

| Интегральный регулятор | 1982 |

|

SU1297007A1 |

| Устройство для моделирования импульсного частотно-фазового дискриминатора | 1986 |

|

SU1354218A1 |

| ЦИФРОВОЙ РЕГУЛЯТОР | 1971 |

|

SU318017A1 |

| Пневматический регулятор | 1978 |

|

SU840796A1 |

| ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНЫЙ РЕГУЛЯТОР | 2002 |

|

RU2234116C1 |

| Пневматический самонастраивающийся регулятор | 1976 |

|

SU590693A1 |

| СПОСОБ УПРАВЛЕНИЯ ГРУППОЙ ИМПУЛЬСНЫХ ПРЕОБРАЗОВАТЕЛЕЙ | 1983 |

|

SU1284443A1 |

| Самонастраивающаяся система комбинированного регулирования | 1986 |

|

SU1339494A1 |

| Аналого-цифровой интегратор | 1977 |

|

SU682908A2 |

Пропорционально-интегральный регулятор относится к технике автоматического управления и регулирования. Целью изобретения является повышение точности и быстродействия. Поставленная цель достигается тем, что в регулятор введена цепь корр екции, состоящая из двух элементов НЕРАВНОЗНАЧНОСТЬ и элемента совпадения, позволяющая осуществлять сброс интегральной составляющей на основе анализа знаков сигналов пропорциональной и интегральной составляющей. 1 ил. (/)

Редактор Е. Копча

Составитель С. Никитой

Техред М.Моргентал Корректор М. Шароши

Заказ 2658/51Тираж 863Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская иаб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Бесекерский В.А., Попов Е„П, Теория систем автоматического .управления | |||

| М.: Машиностроение, 1972, с | |||

| Говорящий кинематограф | 1920 |

|

SU111A1 |

| Система управления | 1977 |

|

SU705417A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Система управления | 1982 |

|

SU1092461A2 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-06-30—Публикация

1986-01-13—Подача