Изобретение относится к вычислительной технике и может быть нгполь- зовано в арифметических устройствах, работающих п избыточной двоичной системе счисления.

Цель изобретения - упрощение устройства. I

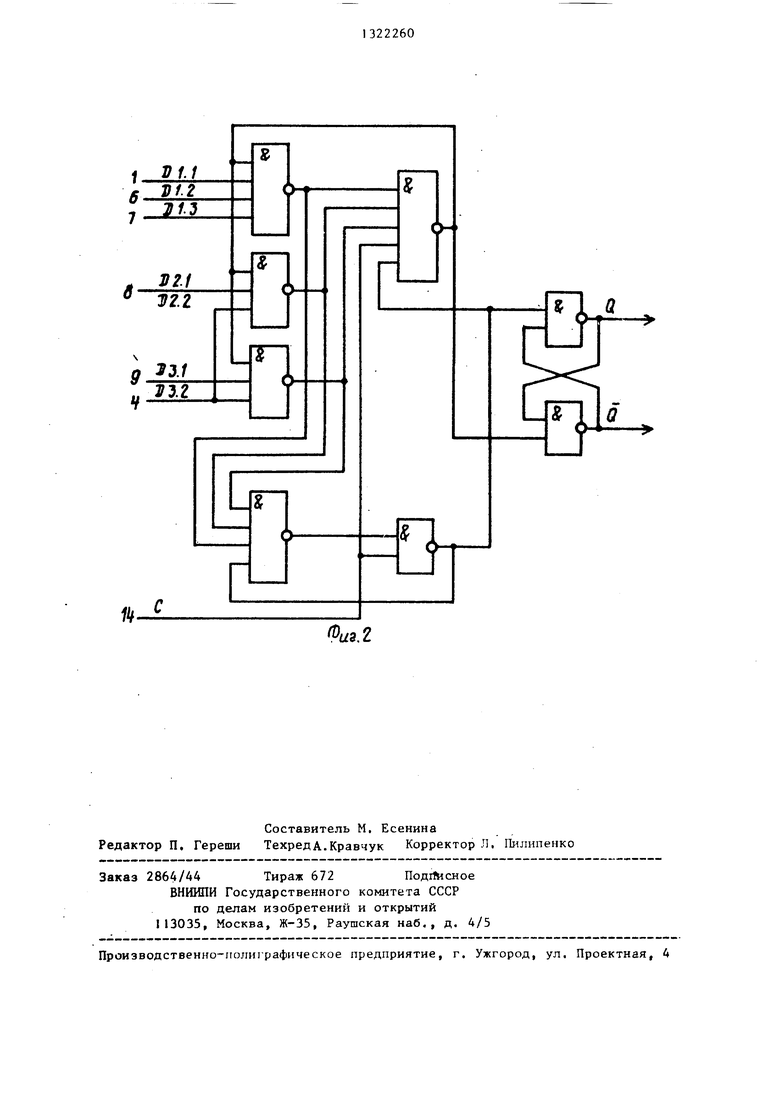

На фиг. I представлена функциональная схема последовательгогч) сумматора; на фиг. 2 - функциональная схема первого D-триггера, пример выполнения .

Последовательный суммагор содержи вход 1 инверсного значения второго операнда (а), первый 2 и второй 3 D-триггеры, вход 4 прямого значения второго операнда (а), третий D-триг- гер 5, вход 6 иччерсного положит ель- ного значения первог о операнда (Ь ),

вход 7 инверсного отрицательного зна- 20 сумматор дает задержку получения

Входная логика второгоD-триггера

3 формирует отрицательноезначение

результата п соответствиис логическим выражением

,4,, b-;.

Входная логика третьего D-триггера 5 формирует положительное значение результата в соответствии с логическим выражением

..

Z

a,S;.,

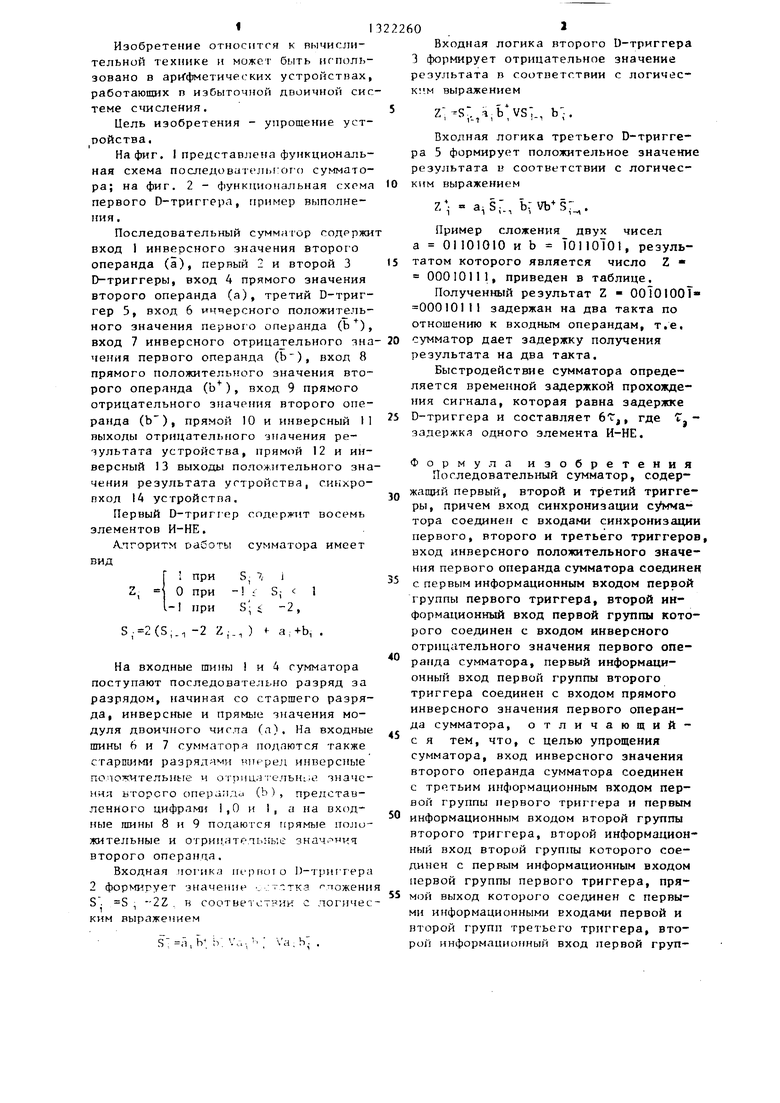

Пример сложения двух чисел а 01101010 и b TOIIOTOI, результатом которого является число Z « 00010111, приведен в таблице.

Полученный результат Z - OOTOIOOT 00010111 задержан на два такта по отношению к входным операндам, т.е.

чеиия первого операнда (Ь ), вход 8 прямого положительного значения второго операнда (Ь ), вход 9 прямого отрицательного значения второго операнда (Ь), прямой 10 и инверсный 11 выходы отрицательного значения результата устройства, прямой 12 и инверсный 13 выходы положительного значения результата устройства, синхро- пхол 1А устройства.

Первый D-TpHri ep содержит восемь злементов И-НЕ.

Алгоритм работы сумматора имеет вид

5,7, i

- i Si 1 SU -2,

S,.2(Si., -2 Z;., ) - a,-t-b, .

Ha входные шины и 4 сумматора поступают последовательно разряд за разрядом, начиная со старшего разряда, инверсные и прямые значения модуля двоичного числа (а). На входные шины 6 и 7 сумматора подаются также старпшми разрядами Н1трред инверсные поаожчтельные и отрица- е.г1ЬН:;с значения второго опера; ли (Ь ) , представленного цифрами 1,0 и 1, а на входные шины 8 и 9 подаются прямые положительные и отрицательные значения второго операнда.

Входная логика nepnoio 1)-триггера 2 формирует значение , тка ложени S . S , -2Z , в соответстрик с логическим выражением

S а, h Ь;

va, ь:

результата на два такта.

Быстродействие сумматора определяется временной задержкой прохождения сигнала, которая равна задержке О-триггера и составляет 6Т,, где Г - задержка одного элемента И-НЕ.

Формула изобретения Последовательный сумматор, содержащий первый, второй и третий триггеры, причем вход синхронизации сумматора соединен с входами синхронизации первого, второго и третьего триггеров, вход инверсного положительного значения первого операнда сумматора соединен с первым информационным входом первой группы первого триггера, второй информационный вход первой группы которого соединен с входом инверсного отрицательного значения первого операнда сумматора, первый информационный вход первой группы второго триггера соединен с входом прямого инверсного значения первого операнда сумматора, отличающий- с я тем, что, с целью упрощения сумматора, вход инверсного значения второго операнда сумматора соединен с тро.тьим информационным входом первой группы первого триггера и первым

информационным входом второй группы второго триггера, второй информационный вход второй группы которого соединен с первым информационным входом первой группы первого триггера, прямой выход которого соединен с первыми информационными входами первой и второй групп третьего триггера, второй информационный вход первой груп

31

пы которого соединен с первыми информационными входами второй и третьей групп первого триггера и входом прямого значения второго операнда сумматора, третий информационный вход первой группы третьего триггера соединен с вторым информационным вхо дом первой группы первого триггера, второй информационный вход второй группы которого соединен с входом прямого положительного значения первого операнда сумматора и вторым информационным входом второй группы третьего триггера, вход прямого отри дательного значения первого операнда

222604

сумматора соединен с информационным входом третьей группы первого триггера, инверсный выход которого соединен с третьим информацион- с ным входом второй группы и вторым информационным пходом первой группы второго триггера, прямой и инверсный выходы которого соединены соответственно с прямым отрицательным и инtO версным отрицательным выходом результата сумматора, прямой и инверсный выходы третьего сумматора соединены соответственно с прямым положительным и инверсным положительным вьг15 ходом результата сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения в избыточной двоичной системе счисления | 1981 |

|

SU1587494A1 |

| Устройство для сравнения чисел | 1979 |

|

SU840890A1 |

| Последовательный сумматор | 1985 |

|

SU1663610A1 |

| Последовательный сумматор в избыточной двоичной системе счисления | 1988 |

|

SU1619251A1 |

| Устройство для сложения в избыточнойдВОичНОй СиСТЕМЕ СчиСлЕНия | 1979 |

|

SU824201A1 |

| Устройство для сложения чисел в из-быТОчНОй СиСТЕМЕ СчиСлЕНия | 1979 |

|

SU824199A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Сумматор в избыточной двоичной системе счисления | 1982 |

|

SU1042011A1 |

| Устройство для умножения | 1982 |

|

SU1059566A1 |

| Устройство для умножения | 1981 |

|

SU1013946A1 |

Изобретение относится к области вычислительной техники, может быть использовано в последовательных арифметических устройствах, работающих в избыточной системе счисления, и позволяет сократить оборудование. Цель изобретения - упрощение устройства. Последовательный сумматор содержит вход 1 инверсного значения второго оператора (а, первый 2 и второй 3 D-триггеры, вход 4 прямого значения второго операнда (а), третий D-трнг- гер 5, вход 6 инверсного положительного значения первого операнда (Ь), вход 7 инверсного отрицательного значения первого операнда (Ь ), вход 8 прямого положительного значения второго операнда (Ь), вход 9 прямого отрицательного значения второго операнда (Ь), прямой и инверсный выходы 10 и 1I отрицательного значения результата устройства, прямой и инверсный выходы 12 и 13 положительного значения результата устройства, синхро- вход 14 устройства. 2 ил., I табл. СЛ Фиг.1

i/a.2

Авторы

Даты

1987-07-07—Публикация

1986-03-11—Подача