регистры 3,-Зр первой группы, блоки 4,-4р преобразования данных, буферные регистры 5,-5р второй грунпы, решающие блоки 6,-6р, блок 7 буферных регистров, блок 8 преобразования результата, буферньп регистр 9. Повы1

Изобретение относится к цифровой вычислительной технике, а именно к устрО 1Ствам для обработки цифролых данных, и можеэ быть использовано дл реиюния дифференциальных ypaBneinri i D частных производных.

иель изобретения - повышение точности решения уравнений.

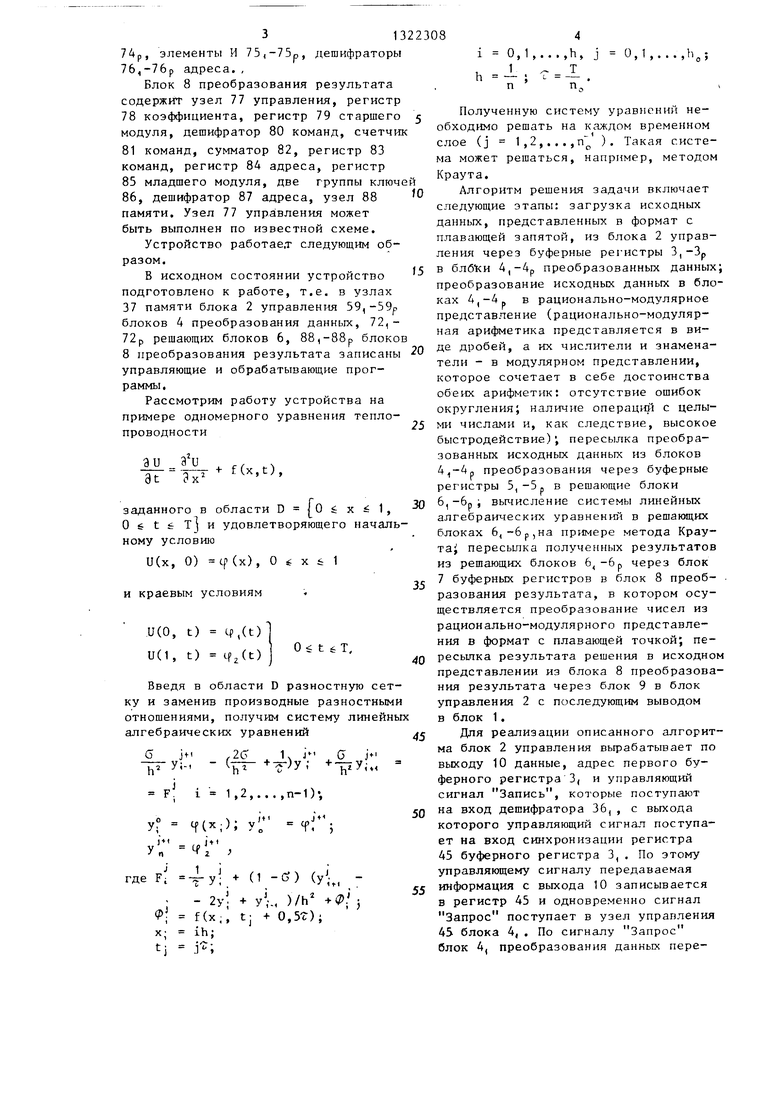

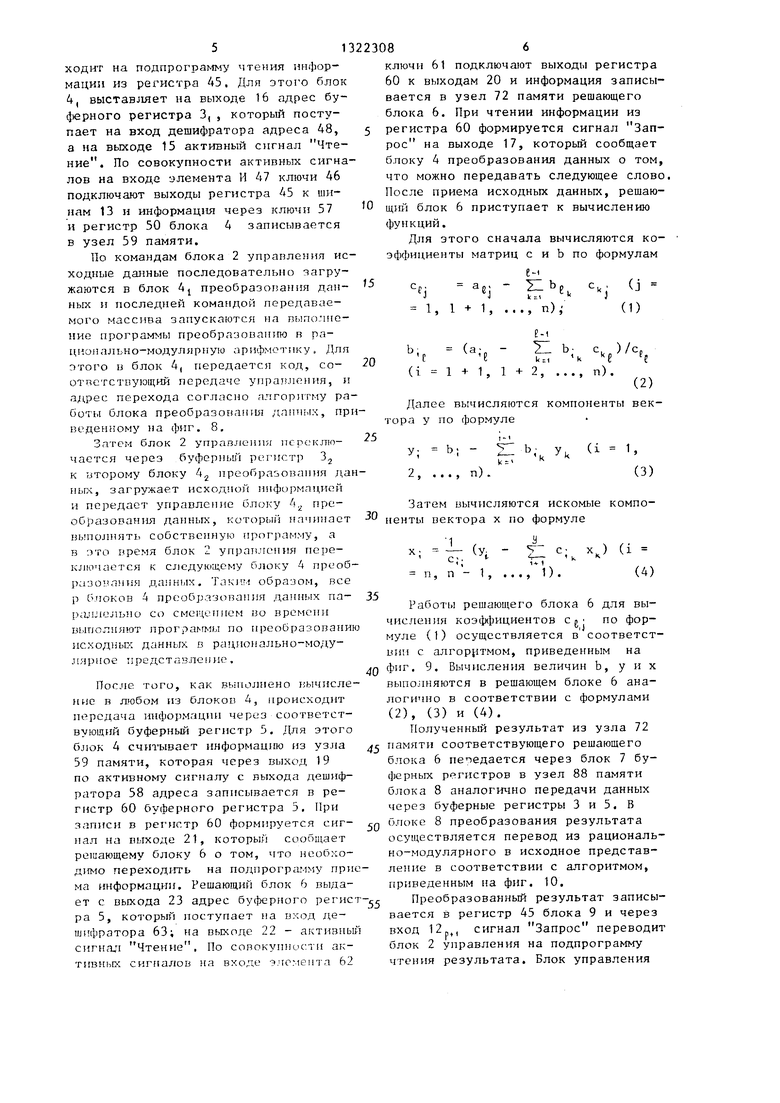

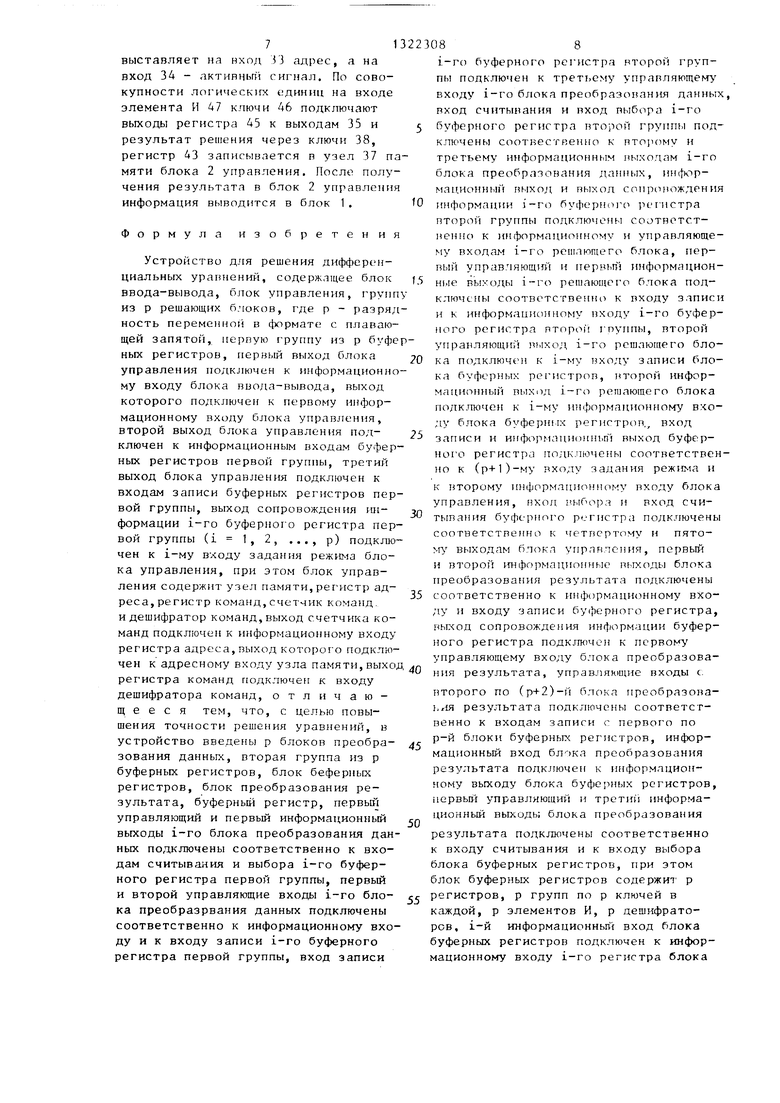

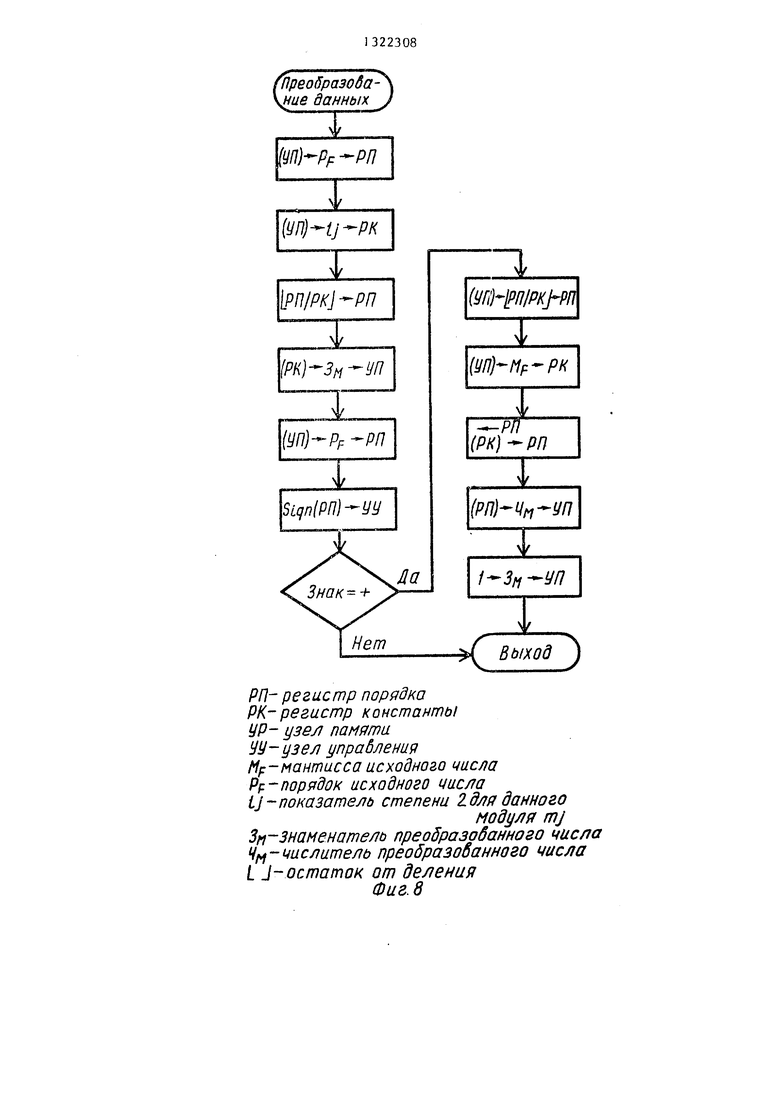

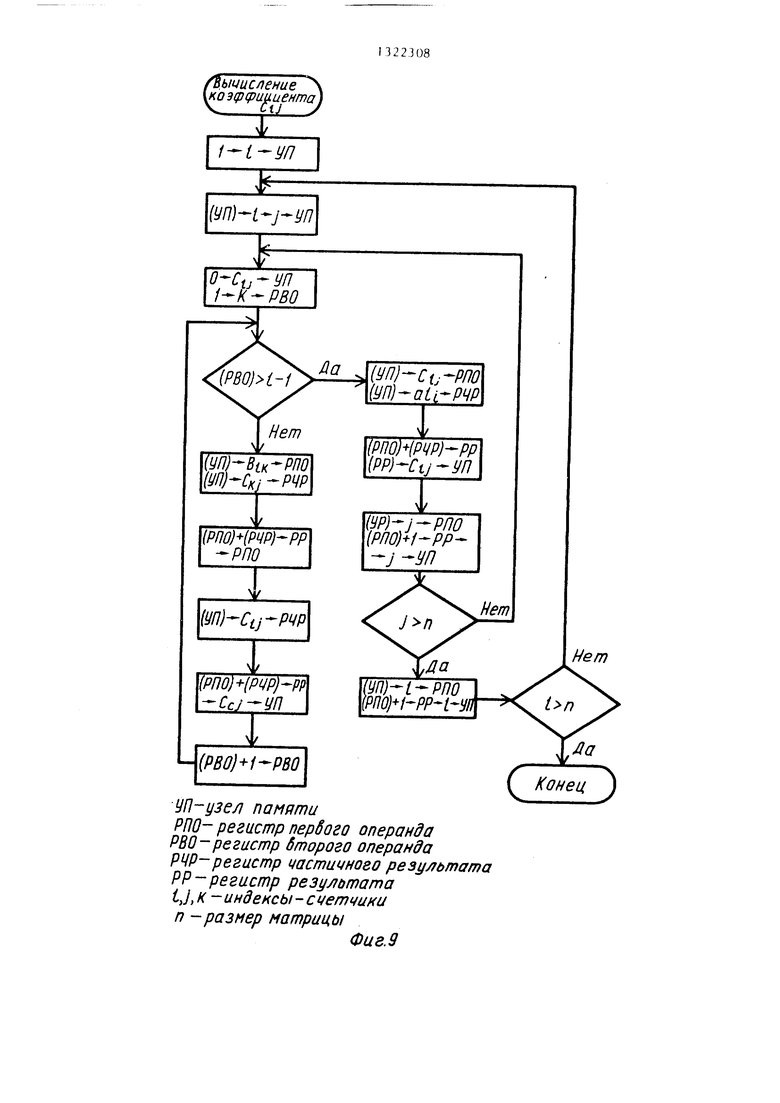

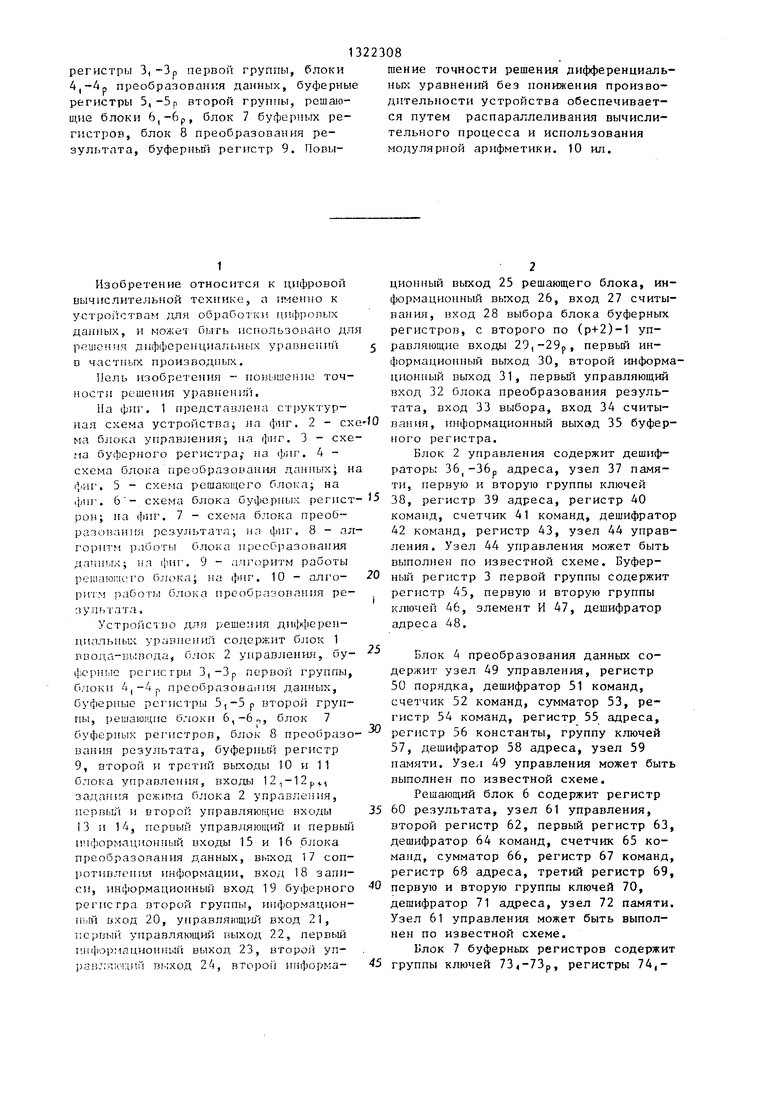

На фиг. 1 представле}иг структурная схема устройства; на фиг, 2 - cx ма блока управления на фиг, 3 - схе па буферного регистра,- на (Ьиг, 4 - схема бло1са преобразования даннь х н 1} ,1Г, 5 - схема решающего блока; на (jjiu , 6- схема блока буферных регист ро}); на фиг, 7 - схема блока преобразования результата; ил фиг, 8 - алгоритм p.iooTbi блока преобразования д,апньгх; па ilnir, 9 - алг.)ритм работы решающего блока; на фиг, 10 - ал го- ри 1 м работы блока преобразования ре- зу.1И1 гата.

Устройство для решения дИ11х1)ере}1- циальньк уравнений содержит блок 1 ввода-вывода, блок 2 управленш}, бу- ферн1ле регистры 3,-Зр первой группы, блоки 4|-Ар преобразования данных, буферные регистры 5,-5р второй группы, реишющие блоки 6,-6 г,, блок 7 буферных регистров, блок 8 преобразо вания результата, буфернь регистр 9, второй и третий выходы 10 и 11 блока управления, входы 12,-12р4, задания рея;ш-га блока 2 управления, первый и второй управляющие входы 13 и 14, первый управляющий и первьш ип(1)ормационный входы 15 и 16 блока преобразования данных, выход 17 соп- ротивленшт информации, вход 18 записи, информационный вход 19 буферного регистра второй группы, информацион- ньм вход 20, у11равляюш,ий вход 21, nepBMii управляющий выход 22, первый 1и1|1|Ормацион11ый выход 23, второй уп- раи::я|01цпГ1 в Гход 24, BTopoii информа-

шение точности решения дифференциальных уравнений без понижения производительности устройства обеспечивается путем распараллеливания вычислительного процесса и использования модулярной арифметики. 10 ил.

ционный выход 25 решающего блока, информационный выкод 26, вход 27 считывание, вход 28 выбора блока буферных регистров, с второго по (р+2)-1 управляющие входы 29,-29р, первый информационный выход 30, второй информационный выход 31, первьш управляющий вход 32 блока преобразования результата, вход 33 выбора, вход 34 считывания, информационный выхэд 35 буферного регистра.

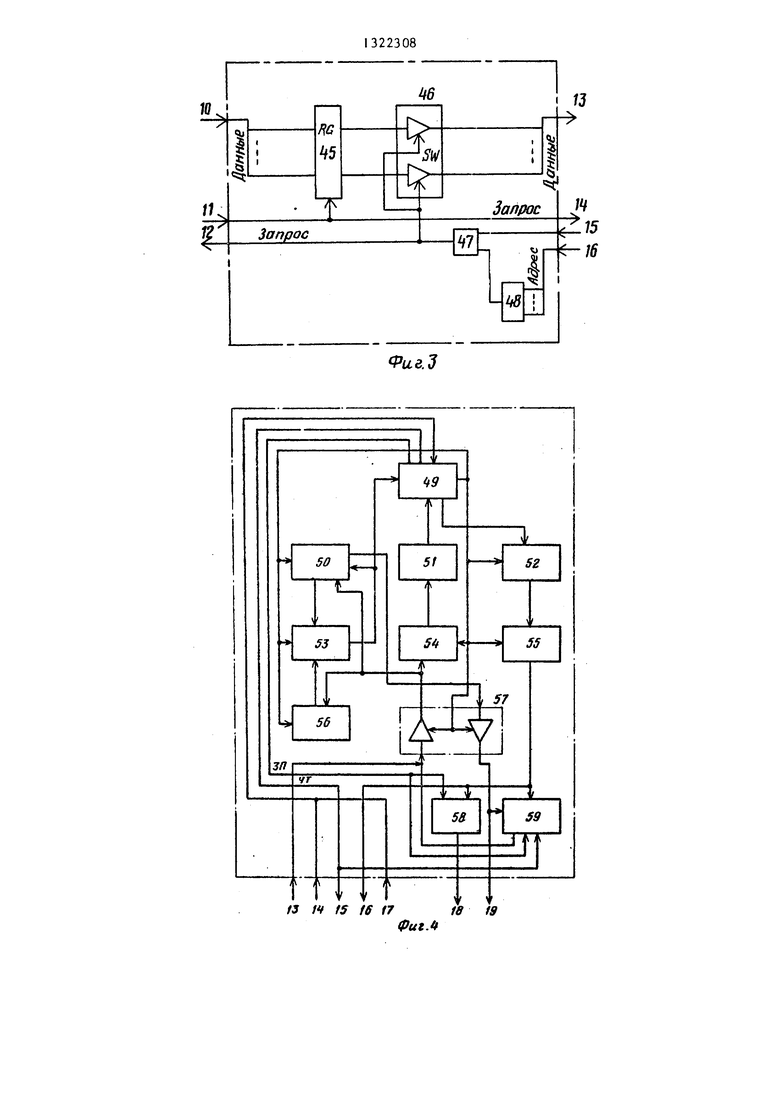

Блок 2 управления содержит дешифраторы адреса, узел 37 памяти, первую и вторую группы ключей 38, регистр 39 адреса, регистр 40 команд, счетчик 41 команд, дешифратор 42 команд, регистр 43, узел 44 управления. Узел 44 управления может быть выполнен по известной схеме. Буферный регистр 3 первой группы содержит регистр 45, первую и вторую группы ключей 46, элемент И 47, дешифратор адреса 48.

Блок 4 преобразования данных содержит узел 49 управления, регистр 50 порядка, дешифратор 51 команд, счетчик 52 команд, сумматор 53, регистр 54 команд, регистр 55 адреса, регистр 56 константы, группу ключей 57, дешифратор 58 адреса, узел 59 памяти, y3eji 49 управления может быть выполнен по известной схеме.

Решающий блок 6 содержит регистр 60 результата, узел 61 управления, второй регистр 62, первый регистр 63, дешифратор 64 команд, счетчик 65 команд, сумматор 66, регистр 67 команд, регистр 68 адреса, третий регистр 69, первую и вторую группы ключей 70, дешифратор 71 адреса, узел 72 памяти, Узел 61 управления может быть выполнен по известной схеме.

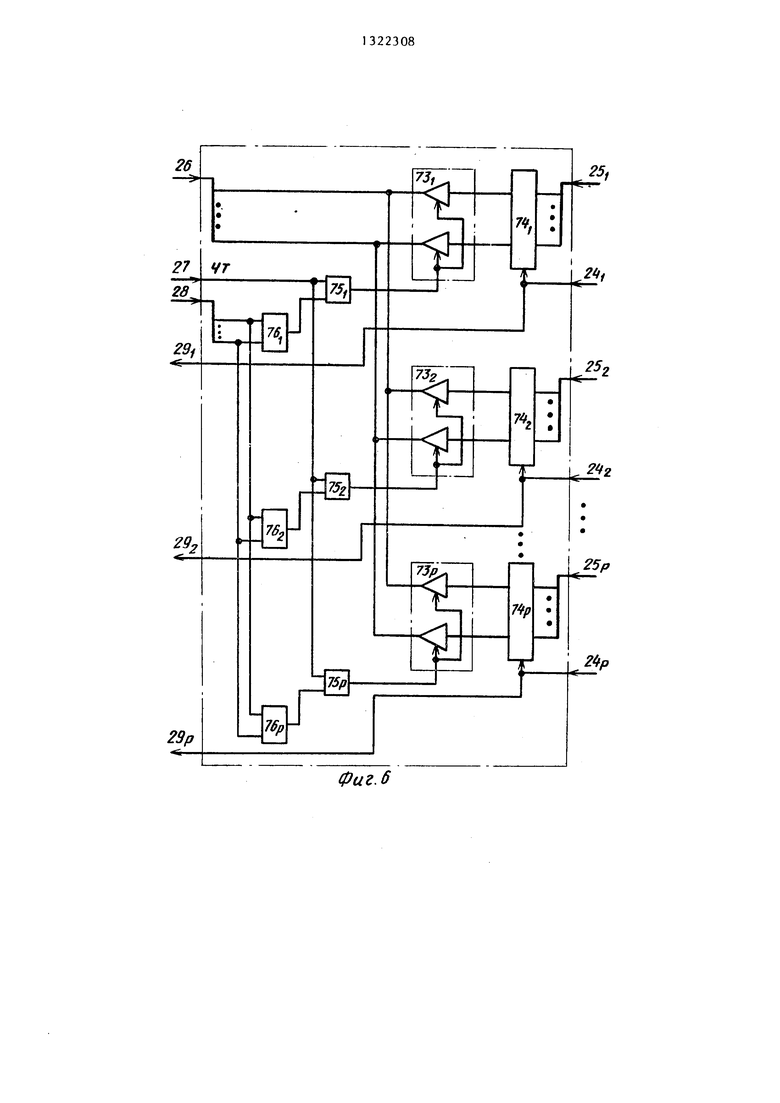

Блок 7 буферных регистров содержит группы ключей 73,-73р, регистры 74,74р, элементы И 75,-75р, дешифраторы 76,-76р адреса. ,

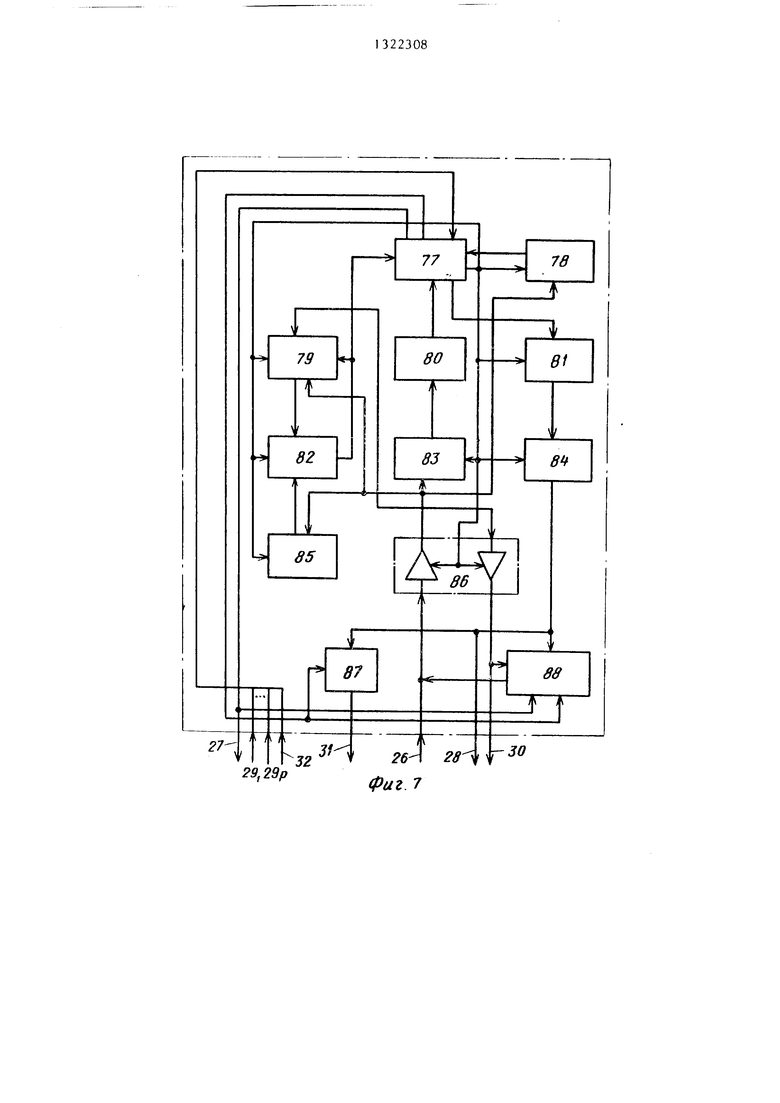

Блок 8 преобразования результата содержит узел 77 управления, регистр 78 коэффициента, регистр 79 старшего модуля, дешифратор 80 команд, счетчи 81 команд, сумматор 82, регистр 83 команд, регистр 84 адреса, регистр 85 младшего модуля, две группы ключ 86, дешифратор 87 адреса, узел 88 памяти. Узел 77 упра1вления может быть выполнен по известной схеме.

Устройство работает следующим образом.

В исходном состоянии устройство подготовлено к работе, т.е. в узлах 37 памяти блока 2 управления 59,-59р блоков 4 преобразования данных, 72, - 72р решающих блоков 6, 88,-88р блоко 8 преобразования результата записаны управляющие и обрабатывающие программы.

Рассмотрим работу устройства на примере одномерного уравнения теплопроводности

аи

3t 9х

т + f(x,t).

заданного в области D | 0ixi1, О t t 5 т и удовлетворяющего начальному условию

и(х, 0) tp (х), О X 6 1 и краевым условиям .

и(0, t) 4,(t)l

U(1, t) .f,(t)

Введя в области D разностную сетку и заменив производные разностными отношениями, получим систему линейных алгебраических уравнений г

.2G

К J

f -ч- .

(-

1,2n-1)v

4(х;); у

/tl

тГ

.

1 J

где Fi 4-у1/ (1 -С) (, - 2у; + yi, )/h j

Ф; f(x;, tj + 0,5t);

x; ih;

J-;

i 0,1,...,h, j 0,1 ,...,b ;

h

JL

По

ьтата егистр аршего 5 счетчик р 83 истр ы ключей 88 ет е.

им обство -5 злах ,-59р , 72, - блоков исаны огнаепло25

i1, ачаль,0

сеттнымиинейных г

-

t

50

55

Полученную систему уравнений необходимо решать на каждом временном слое (j 1 ,2 ,. . ., п ). Такая система может решаться, например, методом Краута.

Алгоритм решения задачи включает следующие этапы: загрузка исходных данных, представленных в формат с плавающей запятой, из блока 2 управления через буферные регистры 3,-Зр в блбХи 4,-4р преобразованных данных; преобразование исходных данных в блоках 4,-4р в рационально-модулярное представление (рационально-модулярная арифметика представляется в виде дробей, а их числители и знаменатели - в модулярном представлении, которое сочетает в себе достоинства обеих арифметик: отсутствие ошибок округления; наличие операций с целыми числами и, как следствие, высокое быстродействие); пересылка преобразованных исходных данных из блоков 4,-4р преобразования через буферные регистры 5,-5р в решающие блоки 6,-6р; вычисление системы линейных алгебраическ1тх уравнений в решающих блоках 6,-6р,на примере метода Крау- та пересылка полученных результатов из решающих блоков 6,-6р через блок 7 буферных регистров в блок 8 преоб- . разования результата, в котором осуществляется преобразование чисел из рационально-модулярного представления в формат с плавающей точкой; пе- ресьшка результата решения в исходном представлении из блока 8 преобразования результата через блок 9 в блок управления 2 с последующим выводом в блок 1.

Для реализации описанного алгоритма блок 2 управления вьфабатывает по выходу 10 данные, адрес первого буферного регистра 3( и управляющий сигнал Запись, которые поступают на вход дешифратора 36, , с выхода которого управляющий сигнал поступает на вход синхронизации регистра 45 буферного регистра 3, . По этому управляющему сигналу передаваемая информация с выхода 10 записывается в регистр 45 и одновременно сигнал Запрос поступает в узел управления 45 блока 4, . По сигналу Запрос блок 4, преобразования данных пере

ходит на подпрограьпчу чтения информации из регистра 45, Для этого блок 4, выставляет на выходе 16 адрес бу- 4)ерного регистра 3, , которьш поступает на вход дешифратора адреса 48, а на выходе 15 активный сигнал Чтение. По совокупности активных сигналов на входа элемента И 47 ключи 46 подключают выходы регистра 45 к шинам 13 и информация через ключи 57 и регистр 50 блока 4 записывается в узел 59 памяти.

По командам блока 2 управления исходные данные последовательно загружаются в блок 4j преобразования данных и последней командой передаваемого массива запускаются на выполнение программы преобразованию в ра- циолально-модулярную арпфмотику. Для этого в блок 4, передается код, со- отпстствующий передаче управления, и адрес перехода согласно алгоритму работы блока преобразования дшшых, прведенному на фиг. 8.

Затем блок 2 управления псрс клю- чается через буферньи регистр 3 к иторому блоку 4,; преобразования даных, загружает исходной информацией и передает управление блоку 4 образования данных, которьп выполнять собственную программу, а в это время блок 2 управления переключается к следующему блоку 4 преоб разонлния данных, TaKJn.i образом, все р блоков 4 преобразования данных па- piUijinjibHO со смещетишм во времени выполняют пpoгpa гмы по иреобразовани псходньк данных в рационально-модулярное представление,

,. пре- начинает

После того, как вьпюлнено вычисление в л-юбом из блоков 4, происходит передача 1«1формации через соответствующий буферный регистр 5. Для этого блок 4 считывает информацию из узла 59 памяти, которая через выход 19 по активному сигналу с выхода дешифратора 58 адреса записывается в регистр 60 буферного регистра 5. При записи в регистр 60 формируется сигнал на выходе 21, который сообщает решающему блоку 6 о том, что необходимо переходить на под11рогр;1г. приема информации. Решающий блок 6 выдает с выхода 23 адрес бу(зерного регист ра 5, который поступает на вход дешифратора 63; на вьпчоде 22 - активный сигна; Чтение, По совокупнис .ти активных сигналов на входе элемента 62

0

23086

ключи 61 подключа от выходы регистра 60 к выходам 20 и информация записывается в узел 72 памяти решающего блока 6. При чтении информации из регистра 60 формируется сигнал Запрос на выходе 17, который сообщает блоку 4 преобразования данных о том, что можно передавать следующее слово. После приема исходных данных, решаю- щш блок 6 приступает к вычислению функций.

Для этого сначала вычисляются коэффициенты матриц с и Ь по формулам

5

-fi

«

0

1, 1 + 1,

-е + 1,

1 +

ей

F

k 1

., п) ,

Е-1 Ь;

kri

Т

- , . . .

(J (1)

)

п).

г (2)

Далее вычисляются компоненты вектора у по формуле

Ь: (i 1,

п).

k

(3)

-

30

Затем вычисляются искомые компоненты вектора х по формуле

п.

J

с; п

(у. а v

1).

(i (4)

-

35

Работы решающего блока 6 для вы -

числения коэ(1к{)ициентов с

e,i

по фор

муле (1) осуществляется в соответствии с алгор11тмом, приведенным на

jQ фиг. 9. Вычисления величин Ь, у и х выпоопшются в решающем блоке 6 аналогично в соответствии с формулами (2), (3) и (4).

Полученный результат из узла 72

памяти соответствующего решающего блока 6 передается через блок 7 буферных регистров в узел 88 памяти блока 8 аналогично передачи данных через буферные регистры 3 и 5. В блоке В преобразования результата осуществляется перевод из рационально-модулярного в исходное представление в соответствии с алгоритмом, приведенным на фиг. 10.

Преобразованный результат записывается в регистр 45 блока 9 и через вход 12 , сигнал Запрос переводи блок 2 управления на подпрограмму чтения результата. Блок управления

50

выставляет на вход ГЗ адрес, а на вход 34 - актиичьп сигнал. По совокупности логических единиц на входе элемента И 47 ключи 46 подключают вькоды регистра 45 к выходам 35 и результат решения через ключи 38, регистр 43 записывается п узел 37 памяти блока 2 управления. После получения результата в блок 2 управления информация выводится в блок 1.

Формула изобретения

Устройство д. гя решения дифферен- циальньгх уравнений, содержащее блок ввода-вывода, блок управления, группу из р решающих блоков, где р - разрядность переме)и1ой в формате с плавающей запятой, первую группу из р буфер - Hi.ie выходы i-ro решающего блока подключены соответственно к входу записи и к информацио)ному входу i-ro буферного регистра второй гпугты, второй управляющий i-ro решающего блоных регистров, первый выход блока 20 ка подключен к i-му входу записи бло- управления подключен к информационно- . буферных регистров, второй инфор- му входу блока ввода-вывода, выход которого подключен к первому информационному входу блока управлен)я, второй выход блока управления подключен к информационным входам буфермационный выход 1-го решающего блока подключен к i-му информационному входу блока буферных регистров., вход записи и информационньп выход буферного регистра подключены соответственно к (р+1)-му входу задания режима и к второму информадионпому входу блока

управления, вход выбора и вход счи- вои группы, выход сопровождения ин- in , к. лтывания буферного регистра подключены

ных регистров первой группы, третий выход блока управления подключен к входам записи буферных регистров перформации 1-го буферног о регистра первой группы (i 1, 2, ..,, р) подключен к i-му входу задания режима блока управления, при этом блок управления содержит узел памяти, регистр адреса, регистр команд,счетчик команд, и дешифратор команд, выход счетчика команд подключен к информационному входу регистра адреса, выход которого подключен к адресному входу узла памяти, выход п

НИН результата, управляк1щие входы с регистра команд подключен к входу

дешифратора команд, отличающееся тем, что, с целью повышения точности решения уравнений, в устройство введены р блоков преобра- 5 зования данных, вторая группа из р буферных регистров, блок беферньк регистров, блок преобразования результата, буферный регистр, первый управляющий и первый информационный выходы i-ro блока преобразования данных подключены соответственно к входам считывания и выбора 1-го буферного регистра первой группы, первый и второй управляющие входы 1-го бло- гг регистров, р групп по р ключей в ка преобразрвания данных подключены каждой, р элементов И, р дешифрато- соответственно к информационному вхо- ров, i-й информационньп вход блока ду и к входу записи i-ro буферного буферных регистров подключен к инфор- регистра первой группы, вход записи мационному входу i-ro регистра блока

соответственно к четвертому и пято- rv выходам блокл управления, первый и второй информационные выходы блока преобразования результата подключены 35 соответственно к информацисжному входу и входу записи буферного регистра, вькод сопровождения информации буферного регистра подключен к первом управляющему входу блока преобразовавторого по (р+2)-й блока преобразова- f,,M результата подключены соответственно к входам записи с первого по р-й блоки буферных регистров, информационный вход преобразования результата подключеп к информационному выходу блока буферных регистров, первый управляющий и третий информационный выходы блока преобразования

50

результата подключены соответственно к входу считывания и к входу выбора блока буферных регистров, при этом блок буферных регистров содержит р

i-ro буферного регистра второй группы подключен к третьему управляющем входу i-ro блока преобразования данных, вход считывания и вход выбора i-ro

буферного регистра второй группы подключены соотвественно к вторс му и третьему информационным выходам i-ro блока преобразования данных, ин(|юр- мапионный выход и выход сопровождения

информации i-ro буферногс jier-ucTpa второй группы подключены соответственно к информационному и управляющему входам i-ro решающего блока, первый управляющш1: и первьш информационHi.ie выходы i-ro решающего блока подключены соответственно к входу записи и к информацио)ному входу i-ro буферного регистра второй гпугты, второй управляющий i-ro решающего блока подключен к i-му входу записи бло- . буферных регистров, второй инфор-

соответственно к четвертому и пято- rv выходам блокл управления, первый и второй информационные выходы блока преобразования результата подключены соответственно к информацисжному входу и входу записи буферного регистра, вькод сопровождения информации буферного регистра подключен к первом управляющему входу блока преобразова и НИН результата, управляк1щие входы с

5 гг регистров, р групп по р ключей в каждой, р элементов И, р дешифрато- ров, i-й информационньп вход блока буферных регистров подключен к инфор- мационному входу i-ro регистра блока

второго по (р+2)-й блока преобразова- f,,M результата подключены соответственно к входам записи с первого по р-й блоки буферных регистров, информационный вход преобразования результата подключеп к информационному выходу блока буферных регистров, первый управляющий и третий информационный выходы блока преобразования

0

результата подключены соответственно к входу считывания и к входу выбора блока буферных регистров, при этом блок буферных регистров содержит р

буферных регистров, i-й вход записи блока буферных регистров подключен к входу записи/считывания i-ro рег ист- ра блока бу4 ерных регистров, выход j-ro разряда (j 1, ..., р) i-ro регистра блока буферных регистров подключен к информационному входу j-ro i-й группы блока буферных регистров, выходы с первого по р-й ключей групп с первой по р-ю блока буферных рег истров объединены и подключены к информационному выходу блока буферных регистров, вход выбора блока буферных регистров подключеп к входам р дешифраторов блока буфер- ных регистров, вход считывания блока буферных регистров нодк.гцочен ; первым входам р элементов И блока буферных регистров, выход i-ro дешифратора блока буферных регистров подключен к второму входу i-ro элемента И блока буферных регистров, выход i-ro элемента И блока буферных регистров подключен к упрПБ.чяющи;. входам р ключе i-ii группы блока бу- ферньгх регистров, при этом блок управления дополнительно содержит две группы ключей, регистр, узел управления, группу из р дешифраторов адреса, первы выход первой группы узла уп11авле11П)1 блока управления иодтслю- чеи к входу синхронизации регистра Ojjjica управления, irropoii выход перв

групп.. узла управления блока управления подключен к счетному входу счетчика команд блока управления, третий nepBoii. узла управления блока управления подключен входу синхронизаци1 регистра адреса илокя управления, четвертый iiepnoii г эугшы узла упр,:1вления блока у11равле 1ия подк. шчен к управляющим входам ктиочей первой грунпы блока управления, пятый выход первой групп узла управления блока управле 1пя подключеп с управляющим входам ключей второй групп) блока управления, той 1ервой группы узла управ- лентш блока управления подключен к входу си1 хронизадии рег истра команд бло}са управления, выходы де иифрато- ра команд блока упра)Ы1ения подключены к входам первой группы узла уп- равле 11ш блока управления, информа- н.ионные входы ключей первой группы блока управле 1ия подключены к дам регистра блока- управления, выхо- ,цы ключей BTopoii блока управления подключены к информационным входам регистра команд и к информа- циопнь м входам регистра блока управления, выход регистра адреса блока управления подключен к информационным входам каждого дешифратора адреса блока управления и к четвертому выходу блока управления, первый выход второй группы узла управления, блока управления, второй выход второй группы узла управления блока управления, выходы ключей первой группы блока управления и регистра адреса блока управления объединены и подключены к первому выходу блока управления, выходы ключей первой группы блока управления объединены и подключены к информационному входу узла памяти блока управления и к второму выходу унравления, первьй выход второй группы узла управления блока управления подключен к входу чтения узла памяти блока управления и к пятому блока управления, в торой выход второй группы узла управления блока управления подключен к входу записи узла памяти и к синхровходу каждого де иифратора адреса блока управления, третий выход второй группы вь ходов узла управления блока управления подключен к счетному входу счетчика команд блока управления, вы- ходь дешифраторов блока управления объед1шены и подключены к третьему выходу блока управления, входы с первого по (р+1)-й задания режима блока управления подключены к входам второй группы узла управления блока управления, первь Й информационный вход блока управления, второй информационны вход блока управления и выход узла памяти блока управления объединены и подключены к информационным входам ключей второй группы блока управления, при этом каждый блок преобразования данных содержит узел управления, регистр порядка, де1 ифратор команд, счетчик команд, сумматор, регистр команд, регистр адреса, регистр константы, группы ключей дешифратор адреса, узел памяти, в каждом блоке преобразования данных пер- БЬП1 выход первой группы узла управления подключен к счетному входу счетчика команд блока преобразования данных, второй выход первой группы узла управления преобразования данных подклочен к входу синхронизации ре

гистра адреса блока преобразования данных, третий выход первоу группы узла упраления блока преобразования данных подключен к управляющим входам ключей первой группы блока преоб разования данных, четвертый выход первой группы узла управления блока преобразования данных подключен к управляющим входам ключей второй группы блока преобразования данных, пятый выход первой группы узла управления блока преобразования данных подключен к входу синхронизации регистра команд блока преобразования данных, шестой выход первой группы узла управления блока преобразования данных подключен к входу синхронизации регистра порядка блока преобразования данных, седьмой выход первой группы узла управления блока преобразования данных подключен к синхро- входу сумматора блока преобразования данных, восьмой выход первой группы узла управления блока преобразования данных подключен к входу синхро низации регистра константы блока преобразования данных, входы первой группы узла управления блока преоб

гистра порядка блока преобразования данных подключены к соответстгзующим информационным входам ключей первой группы блока преобразования данных, первый выход второй группы узла управления блока преобразования данных подключен к входу записи узла памяти блока преобразования данньгх и к сипхровходу дешифратора адреса блока преобразования данных, второй выход второй груги1ы узла управления блока преобразования данньгх подключен к входу чтения узла памяти блока преобразования данных и к первому управ- (5 ляющему выходу блока преобразования данных, третш выход второй группы узла управления блока преобразования данных подключен к входу синхронизации счетчика команд блока преобразования данных, первый управляющий вход блока преобразования данных объединен с выходом узла памяти блока преобразования данных и подключен к информационным входам ключей первой группы блока преобразования данньк, выход регистра адреса блока преобразования данных подключен к входу узла блока преобразования данньгх, к входу дешифратора адреса блока преобразоваразования данньгх подключен к выходам дешифратора команд блока преобразова- 30 ния данных и к первому информацион- ния данных, вход которого подключен ному выходу блока преобразования дан- к выходу регистра команд блока преобразования данньгх, выходы ключей первой группы блока преобразования данных, выход дешифратора адреса блока преобразования данных подключен к второму информационному выходу блока

ных, выходы .ключей первой группы бло- 35 преобразования данных, выходы ключей

ка преобразования данньгх объединены и подключены к информационным входам регистра константы и с установочным входом регистра порядка блока преобразования данных, информационный выход счетчика команд блока преобразования данных подключен к информационному входу регистра адреса блока преобразования данных, выходы

первой группы регистра порядка блока преобразования данных подключены к первым информационным входам сумматора блока преобразования данных, вторые информационные входы сумматора блока преобразования данных подключены к выходам регистра константы I блока преобразования данных, выходы

сумматора блока преобразования данных подключены к входам второй группы узла управления блока преобразования данньгх и информационным входам регистра порядка блока преобразования данных, выходы второй группы ре0

гистра порядка блока преобразования данных подключены к соответстгзующим информационным входам ключей первой группы блока преобразования данных, первый выход второй группы узла управления блока преобразования данных подключен к входу записи узла памяти блока преобразования данньгх и к сипхровходу дешифратора адреса блока преобразования данных, второй выход второй груги1ы узла управления блока преобразования данньгх подключен к входу чтения узла памяти блока преобразования данных и к первому управ- 5 ляющему выходу блока преобразования данных, третш выход второй группы узла управления блока преобразования данных подключен к входу синхронизации счетчика команд блока преобразования данных, первый управляющий вход блока преобразования данных объединен с выходом узла памяти блока преобразования данных и подключен к информационным входам ключей первой группы блока преобразования данньк, выход регистра адреса блока преобразования данных подключен к входу узла блока преобразования данньгх, к входу дешифратора адреса блока преобразова0

0 ния данных и к первому информацион- ному выходу блока преобразования дан-

ния данных и к первому информацион- ному выходу блока преобразования дан-

ных, выход дешифратора адреса блока преобразования данных подключен к второму информационному выходу блока

второй группы блока блока преобразования данных объед1тены к информационному входу узла памяти блока и к третьему информационному выходу блока

преобразования данных, второй и третий управляющие входы блока преобразования данных объединены и подключены к входу узла управления блока преобразования данных, при этом блок

преобразования результата содержит узел управления, регистр коэффициента, регистр старшего модуля, дешифратор команд, счетчик команд, сумматор, регистр команд, регистр адреса, регистр младшего модуля, две группы

ключей, дешифратор адреса, узел памяти, причем в каждом блоке преобразования результата первьп выход первой группы узла управления блока преоб- разования результата подключен к

входу синхронизации регистра коэффициента блока преобразования результата, второй выход первой группы узла правления блока преобразования ре131322308

зультата подключен к счетному входуционные входы, входы сумматора блока счетчика команд блока преобразованияпреобразования результата подключены результата, третий выход перпой труп-к выходам регистра младшего модуля nfci узла управления блока преобразова-блока образования результата, информа- ния результата подключен к входу i 5ционные выходы сумматора блока пре- синхронизации регистра адреса блокаобразования результата подключены к преобразования результата, четвертыйвторым информационным входам регистра выход первой группы узла управлениястаршего модуля и к входам второй блока преобразования результата под-группы узла управления блока преобра- ключен к управляющ17м входам ключей (Озования результата, выходы регистра первой группы блока преобразованиякоэффициента блока преобразования результата, пятый выход первой группырезультата подкл}очены к входам треть- узла управления блока преобразованияей группы узла управления блока пре- результата подключен к управляющимобразования результата, первый вы- входам ключей второй группы блока - 15ход второй группы узла управления преобразования результата, шестой вы-блока преобразования результата подход пирвой групп, упла управленияключен к входу записи узла памяти блока преобразоваяия результата под-блока преобразования результата и к ключей к входу сш1хроппзац1П1 рсгист-синхровходу дешифратора адреса блока ра команд блока преобразования рс- 20преобразовапия результата, второй зх-1ьтлтл, седьмой выход перво; группывыход второй группы узла управления узлл управления блока преоОрсЧзопанияблока преобразования результата под- резулругата подключен к входу синхро-ключей к первому-управляющему выходу низации регистра старшего модуля бло-блока преобразования результата и к кп преобразователя результат, весь- 25входам чтения узла памяти блока ире- MOI выход первой группы узла унрав-образования результата, третий выход ления блока преобразования рсзульта-второй группы узла управления блока та пол глючен к синхровходу сумматорапреобразования результата подключен Плока преобразования репультлта, де-к информационному входу установки I l Ti-fi имход первой г 1унпм унрпв- 30счетчика команд блока преобразования . юппл блока прсобоаз( ре-зульта-результата, 1шформационный вход блока та тюлклгочен к Bxo. си; хптп; и1цги1преобразования результата объединен рогистра младшего модуля преоб- с выходом узла памяти блока преобра- ра-зования результата, входы нервойзования результата и подключен к ин- групны узла управления блока прсобра- 35Формационным входам ключей первой .(окьания результата подключены к вы-группы блока преобразования результа- ходам деппфратора команд пре-та, выходы ключей второй группы бло- образования результата, входы которо-ка преоб{Ьазования результата объеди- го подключены к вькодам регистра и подключены к информационному манд блока преобразования результа- 40входу узла памяти блока преобразова- та, ВЫХОД.; ключей второй группы блока я результата и к первому информа- н)еобразования результата объедине-ционному выходу блока преобразования ны и подключены к информационнымрезультата, выход дешифратора адреса иходам регистра коэффициента блокаблока преобразования результата подк- :1 К1образопа1пш результата, регистра 45™чен к второму информационному выхо- команд блока преобразовапия результа-МУ блока преобразования результата, та, регистра младшего модуля блокавыход регистра адреса блока преобра- прообразования результата и с первымзования результата подключен к адрес- ин-Ьормационным входом регистра стар- о У входу узла памяти блока преобра- ;ие.го модуля блока преобразования ре- 50зования результата, к информационному зу.1 ьтата, выходы счетчика команд бло-входу дешифратора адреса блока пре- ка преобразования результата подклю-образования результата и к третьему чоиы к информационным входам регист-информационному выходу блока преоб- ра адреса блока преобразования ре-разования результата, управляющие зультата, первые выходы регистра стар-55 ° первого по (р+2)-й блоков шего модуля блока преобразования ре-преобразования результата объединены зультата подключены к первым информа-и подключены к входу узла управления циоиным входам сумматора блока преоб-блока преобразования данных, выходы разования результата, Езторые информа-регистра старшего модуля блока пре15132230816

.образования данных подключены к нн-чей второй группы блока преобразова-формационным входам одноименных клю-ния данньк.

Фиг 2

Pae.J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения дифференциальных уравнений | 1985 |

|

SU1348854A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1233148A1 |

| Устройство для обработки нечеткой информации | 1985 |

|

SU1564603A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для решения дифференциальных уравнений | 1985 |

|

SU1330635A1 |

| Микропроцессорное устройство для моделирования систем массового обслуживания | 1984 |

|

SU1196886A1 |

| Мультипрограммное вычислительное устройство | 1990 |

|

SU1777147A1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1104513A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1269151A1 |

Изобретение относится к цифровой вычислительной технике, к устройствам обработки цифровых данных, и может быть использовано для решения дифференциальных уравнений в частньк производных. Цель изобретения - повышение точности решения уравнений. Поставленная цель достигается тем, что устройство содержит блок 1 ввода-вывода, блок 2 управления, буферные С/: с

v

/J / 15 tS t718 19

фиг Л

Фиг. 5

Фиг.6

29,29р

фиг. 7

(Преобразоба- шеданнь1к)

(ynhPf -Р//

(

PniPKJ -Р/7

/

}- ЗМ-УП

/

(УП) -РП

f

SLgn(

Ш-lPniPKj-pn

(yfJhHp-PH

i

-ял

(РН)РП

(

f

с Выход

РП регистр порядка РК-регистр константы УР- узел памяти УУ-узел управления Mf-мантисса исходного часла Pf-порядок исходного ци.сла Ij-показатель степени 2. d/fи данного

модули mj

Зп знаменатель преодразобанного числ Ц{ -цаслитель преобразобанного числа L J-остаток от деления Фиг. 8

fB.biQucfienue Л ко эффиаиента}

i-L-УП

(yn)-t-j-yfj

O-Ctj-УП

Щ-BtK-PfJO т-Ск1-РЧР

I

ipnoHP4p)-pp

-РПО

(ynj-Cij-pno

(yn)-nLL-P4P

(рпоИР р)-рр

iPP)-Ctj-yn

m-j-pno

iPfJO)+f-PP-j -yn

f

iynhCij-pyp

(PnO)+()-PP -Ccj-УП

(PBffJ+f-PBO

УП-уз ел памяти

РПО- регистр пербого операнда

РВО-регистр бторого операнда

РЧР-регистр цастичного резу/ftmama

РР-регистр peзljлtзmama

J,« индексы - с 1 етчиии

п -размер матрацы

Фиг.9

Hem

да

Hem

(УП)-1-РПО {PnO)+i-PP-LС Конец J

Редактор Е.Папп

Составитель В.Смирнов

Техред Л.Олийнык Корректор Г.Решетник

2867/47

Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. А/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для решения уравнения математической физики | 1976 |

|

SU584314A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительная система для решения дифференциальных уравнений | 1975 |

|

SU565299A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-07—Публикация

1985-12-11—Подача