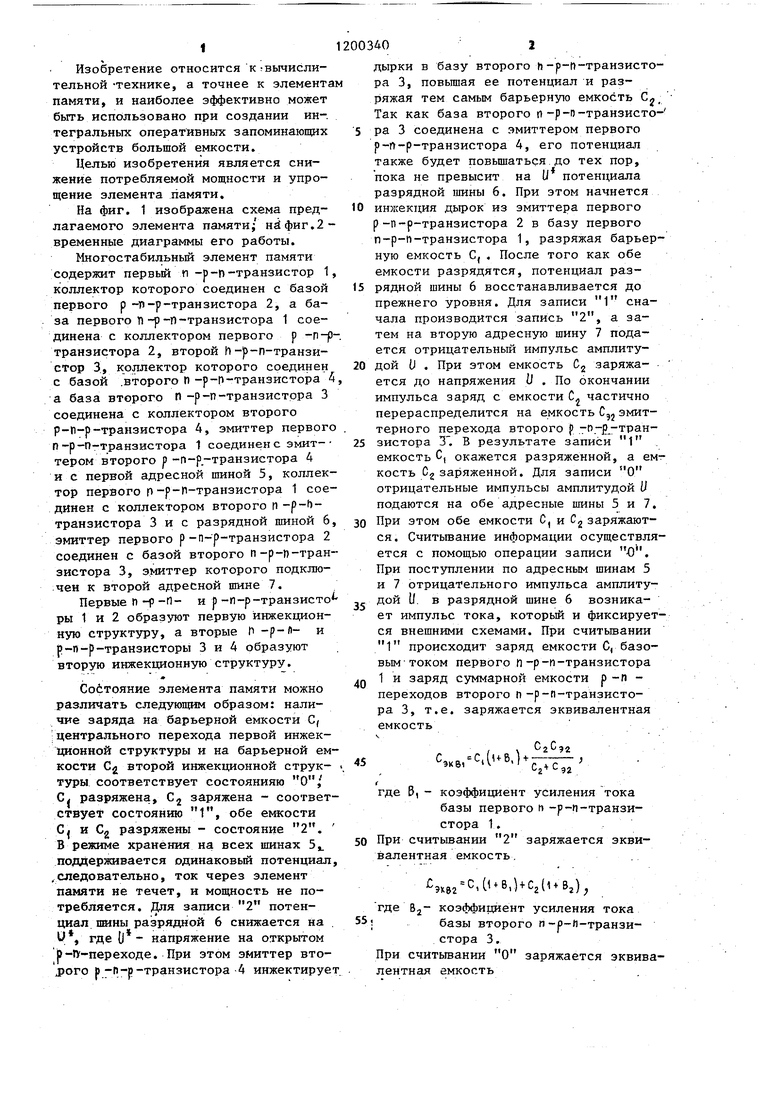

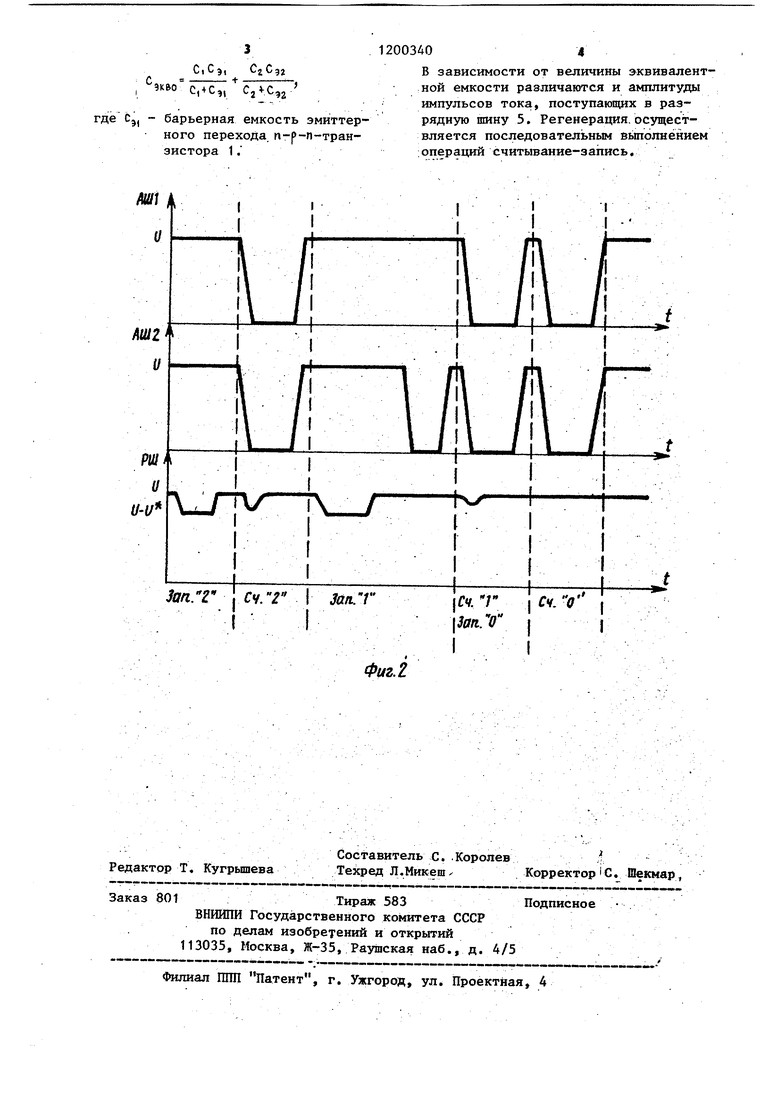

Изобретение относитсяк вычислительной -технике, а точнее к элемент памяти, и наиболее эффективно может быть использовано при создании интегральных оперативных запоминающих устройств большой емкости. Целью изобретения является снижение потребляемой мощности и упрощение элемента памяти. На фиг. 1 изображена схема предлагаемого элемента памяти; ни фиг.2 временные диаграммы его работы. Многостабильный элемент памяти содержит первый п -р-п-транзистор 1 коллектор которого соединен с базой первого р -я-р-транзистора 2, а ба. за первого П-р-П-транзистора 1 соединена с коллектором первого р -птранзистора 2, второй И-р-п-транзистор 3, коллектор которого соединен с базой .второго П-p-fi-транзистора а база второго п -р-п-транзистора 3 соединена с коллектором второго р-П-р-транзистора 4, эмиттер первог р р П-транзистора 1 соединен с эмиттером второго р -п-р.-транзистора 4 и с первой адресной шиной 5, коллек тор первого П-р-П-транзистора 1 сое динен с коллектором второго п -p-fiтранзистора 3 и с разрядной шиной 6 эмиттер первого р-п-р-транзистора 2 соединен с базой второго п-р-Г)-тран зистора 3, эмиттер которого подклю:чен к второй адресной шине 7. Первые п -р -И- и р -п-р-транзисто ры 1 и 2 образуют первую йнжекционную структуру, а вторые П -р-л- и р-п-р-транзисторы 3 и 4 образуют вторую инжекционную структуру. Состояние элемента памяти можно различать следующим образом: наличие заряда на барьерной емкости С, центрального перехода первой инжекционной структуры и на барьерной ем кости С второй инжекционной структуры соответствует состоянияю О, Cj разряжена, Cj заряжена - соответ ствует состоянию 1, обе емкости С и Cg разряжены - состояние 2. В режиме хранения на всех шинах 5. поддерживается одинаковый потенциал .следовательно, ток через элемент памяти не течет, и мощность не потребляется. Для записи 2 потенциал шины разрядной 6 снижается на U, где О напряжение на открытом р-П-переходе. При этом эмиттер втоjjoro р-п-р-транзистора 4 инжектируе 40 2 дырки в базу второго h-р-П-транзистора 3, повьшая ее потенциал и разряжая тем самым барьерную емкость Сл. Так как база второго п-р-п-транзистора 3 соединена с эмиттером первого р-п-р-транзистора 4, его потенциал также будет повьш1аться до тех пор, пока не превысит на I/ потенциала разрядной иганы 6. При этом начнется инжекция дырок из эмиттера первого р-п-р-транзистора 2 в базу первого п-р-п-транзистора 1, разряжая барьерную емкость Cj . После того как обе емкости разрядятся, потенциал разрядной шины 6 восстанавливается до прежнего уровня. Для записи 1 сначала производится запись 2, а затем на вторую адресную шину 7 подается отрицательный импульс амплитудои и . При этом емкость С заряжается до напряжения il . По окончании импульса заряд с емкости С частично перераспределится на емкость С,,, эмиттерного перехода второго f -о- -транзистора 3, В результате записи 1 емкость С, окажется разряженной, а емт кость Cg заряженной. Для записи О отрицательные импульсы амплитудой У подаются на обе адресные шины 5 и 7. При этом обе емкости С, и Cg заряжаются. Считьгаание информации осуществляется с помощью операции записи О. При поступлении по адресным шинам 5 и 7 отрицательного импульса амплитудой и. в разрядной шине 6 возникает импульс тока, которьй и фиксируется внешними схемами. При считьшании 1 происходит заряд емкости С, базовым током первого п-р-п-транзистора 1 и заряд суммарной емкости р-п переходов второго п-р-п-транзистора 3, т.е. заряжается эквивалентная емкость СэкйГ...-. где &, - коэффициент усиления тока базы первого п -р-п-транзистора 1., При считьшании 2 заряжается эквивалентная емкость . 9K82° e)C,,{l+Bj) где Bj- коэффициент усиления тока базы второго п-р-п-транзистора 3. При считьшании О заряжается эквивалентная емкость

CiC9i СгСэ2

-t, ,4С„/С24,С,2

Cj, - барьерная емкость эмиттерного перехода п-р-п-транэистора 1.

12003ДО4

В зависимости от величины эквивалентной емкости различаются и амплитуды импульсов тока, поступающих в разрядную шину 5. Регенерация, осуществляется последовательным вьполнёнием ;операций считывание-запись.

т

шг и

Сч. о

Сч./ Зал.Т

I

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| ЯЧЕЙКА ПАМЯТИ ДИНАМИЧЕСКОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2001 |

|

RU2216795C2 |

| Управляющий регистр для буферного запоминающего устройства | 1987 |

|

SU1499405A1 |

| Запоминающее устройство | 1974 |

|

SU658600A1 |

| Ячейка памяти | 1974 |

|

SU1327185A1 |

| Накопитель для полупроводникового запоминающего устройства | 1980 |

|

SU955202A1 |

| Регистр сдвига для буферного запоминающего устройства | 1985 |

|

SU1432609A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Способ записи и считывания информации в запоминающих устройствах с инжекционным питанием и устройство для его осуществления | 1975 |

|

SU646371A1 |

| Ячейка памяти | 1974 |

|

SU536527A1 |

МНОГОСТАБИПЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ, содержащий первый и-р-п-транзистор, коллектор которого соединен с базой первогор -п-р-транзистора, а база первого л-f-П-транзистора соединена с коллектором первого р -п-ртранзистора, второй -р-Я-транзистор, коллектор которого соединен с базой второгор -п-р-транзистора, а база второго П -р-п-транзистора соедине- на с коллектором второго р -П-р-транзистора, адресные и разрядную шины, отличающийся тем, что, с целью снижения потреблйемой мощности, и упрощения элемента памяти, змиттер первого п-р-

| Многоустойчивый динамический запоминающий элемент | 1977 |

|

SU767839A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| I ЙОКСОЮЗНАЯ 1^:,, ,ТУ-'^л.^,-г,--.(!«;;;угг»г, 5 • -.-•' - '..*„ ' ', t;'V i й1--^'л^'--3 bia'- цц; | 0 |

|

SU366497A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-12-23—Публикация

1983-10-11—Подача