Изобретение относится к вычислительной технике и может быть использовано в устройствах управления при обработке сигналов датчиков синхронизации.

Цель изобретения - повышение надежности работы умножителя за счет синхронизации выходных сигналов формирователя импульсов и генератора тактовых импульсов.

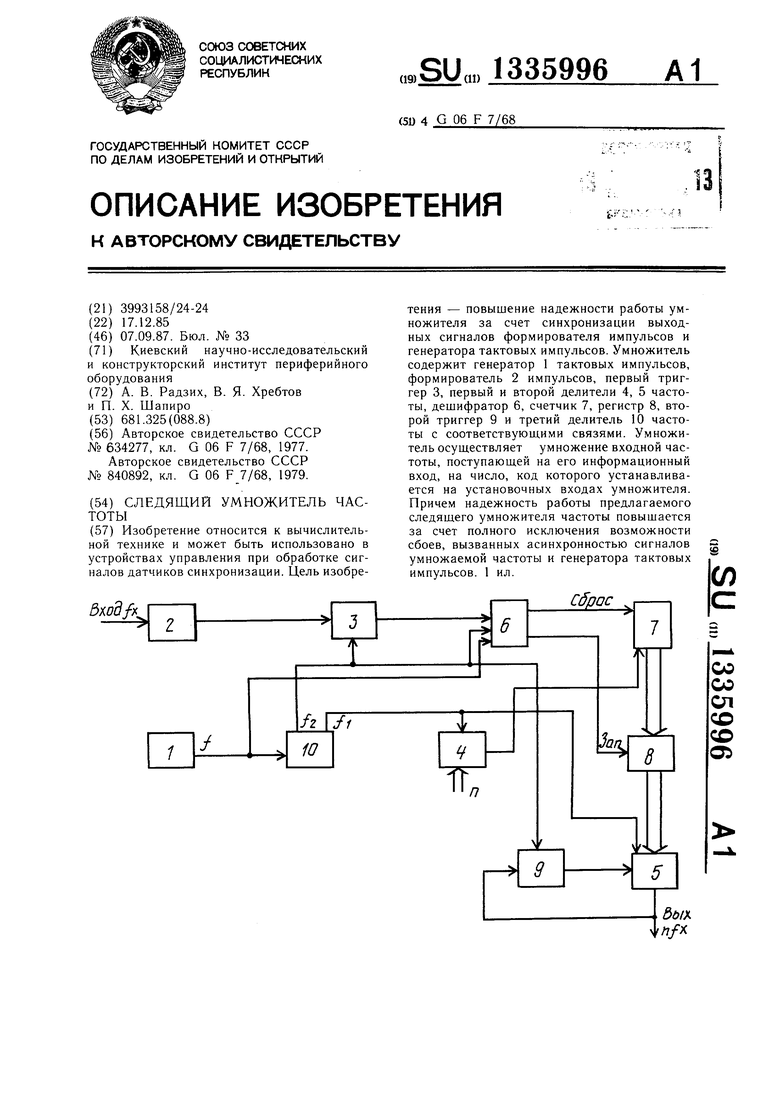

На чертеже приведена функциональная схема следящего умножителя частоты.

Умножитель содержит генератор 1 тактовых импульсов, формирователь 2 импульсов, первый триггер 3, первый делитель 4 частоты, второй делитель 5 частоты, дешифратор 6, счетчик 7, регистр 8, второй триггер 9 и третий делитель 10 частоты, причем информационный вход умножителя соединен с входом формирователя 2 импульсов, выход которого соединен с входом установки в единицу первого триггера 3, выход которого соединен с первым входом дешифратора 6, второй вход которого соединен со вторым выходом третьего делителя 10 частоты, с входом синхронизации первого триггера 3 и входом установки в ноль второго триггера 9, третий вход дешифратора 6 соединен с выходом генератора 1 тактовых импульсов и с информационным входом третьего делителя 10 частоты, первый выход которого соединен с информационными входами первого и второго делителей 4 и 5 частоты, установочные входы умножителя соединены с установочными входами первого делителя 4 частоты, выход которого соединен со счетным входом счетчика 7, разрядные выходы которого соединены соответственно с информационными входами регистра 8, разрядные выходы которого соединены соответственно с установочными входами второго делителя 5 частоты, выход которого соединен с выходом умножителя и с входом установки в единицу второго триггера 9, выход которого соединен с входом разрешения записи информации второго делителя 5 частоты, вход разрешения записи регистра 8 соединен с первым выходом дешифратора 6, второй выход которого соединен с входом сброса счетчика 7.

Умножитель частоты работает следую- шим образом.

Сигналы, формируемые генератором 1 тактовых импульсов, поступают на информационный вход третьего делителя 10 частоты, с первого выхода которого сигналы частотой f|() поступают на информационный вход второго делителя 5 частоты и на информационный вход первого делителя 4 частоты, с выхода которого сигналы с частотой, разделенной на число п, установленное на установочных входах первого делителя 4 частоты, поступают на счетный вход счетчика 7. С приходом очередного сигнала на информационный вход умножителя частоты на выходе формирователя 2 импуль0

5

0

5

0

сов формируется импульс, поступающий на вход установки в единицу триггера 3, который устанавливается в единичное состояние, как только на его синхровход поступит импульс со второго выхода третьего делителя 10 частоты (). Выходной сигнал триггера 3 разрешает работу дешифратора 6, на первом выходе которого формируются импульсы разрешения записи информации в регистр 8, а на втором выходе - импульсы сброса счетчика 7, причем эти импульсы разнесены во времени и вырабатываются в момент, когда счетчик 7 находится в устойчивом состоянии. В регистр 8 запишется код числа N, равный N Т;., где Tj - период входного сигнала; п - коэффициент деления делителя 4 частоты.

В течение следующего периода входного сигнала код числа, записанный в регистр 8, задает коэффициент деления второго делителя 5 частоты. Триггер 9, синхронизируемый сигналами со второго выхода тр.етьего делителя 10 частоты, исключает задание кода в момент переходных процессов в регистре 8. Занесение информации на установочные входы второго делителя 5 частоты производится по формированию импульса переполнения на его выходе. Таким образом, частота импульсов переполнения на выходе второго делителя 5 частоты будет определяться величиной кода N. Поскольку на информационный вход второго делителя 5 частоты поступают импульсы с частотой

f. то f

f1.

вых Jf n-fex. N

Формула изобретения

5

0

5

0

5

Следящий умножитель частоты, содержащий формирователь импульсов, генератор тактовых импульсов, первый, второй и третий делители частоты, регистр и счетчик, причем выход первого делителя частоты соединен со счетным входом счетчика, разрядные выходы которого соединены соответственно с информационными входами регистра, разрядные выходы которого соединены соответственно с установочными входами второго делителя частоты, выход которого является выходом умножителя, установочные входы первого делителя частоты являются входами коэффициента умножения умножителя, вход формирователя импульсов является информационным входом умножителя, а выход генератора тактовых импульсов соединен с информационным входом третьего делителя частоты, первый выход которого соединен с информационным входом первого и второго делителей частоты, отличающийся тем, что, с целью повышения надежности работы умножителя за счет синхронизации выходных сигналов формирователя импульсов и генератора тактовых импульсов, в него введены первый и второй

3 13359964

триггеры и дешифратор, причем выход фор-частоты, а третий вход дешифратора соедимирователя импульсов соединен с входомнен с выходом генератора тактовых импульустановки в «1 первого триггера, вход син-сов, первый выход дешифратора соединен с

хронизации которого соединен с вторымвходом разрешения записи регистра, а втовыходом третьего делителя частоты и входом5 рой - с входом сброса счетчика, выход втоустановки в «О второго триггера, выход пер-рого делителя частоты соединен с входом

вого триггера соединен с первым входомустановки в «1 второго триггера, выход кодешифратора, второй вход которого соеди-торого соединен с входом разрешения занен с вторым выходом третьего делителяписи информации второго делителя частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой умножитель частоты | 1980 |

|

SU928353A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Цифровой умножитель частоты следования импульсов | 1980 |

|

SU1013952A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928352A1 |

| Оптическое устройство для вычисления корреляционной функции | 1988 |

|

SU1520541A1 |

| Умножитель частоты | 1989 |

|

SU1649538A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Способ деления временных интервалов и устройство для его осуществления | 1987 |

|

SU1492352A1 |

| Устройство для кодирования сигналов частотных датчиков | 1985 |

|

SU1336246A1 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах управления при обработке сигналов датчиков синхронизации. Цель изобретения - повышение надежности работы умножителя за счет синхронизации выходных сигналов формирователя импульсов и генератора тактовых импульсов. Умножитель содержит генератор 1 тактовых импульсов, формирователь 2 импульсов, первый триггер 3, первый и второй делители 4, 5 частоты, дешифратор 6, счетчик 7, регистр 8, второй триггер 9 и третий делитель 10 частоты с соответствуюш,ими связями. Умножитель осуществляет умножение входной частоты, поступаюш,ей на его информационный вход, на число, код которого устанавливается на установочных входах умножителя. Причем надежность работы предлагаемого следяшего умножителя частоты повышается за счет полного исключения возможности сбоев, вызванных асинхронностью сигналов умножаемой частоты и генератора тактовых импульсов. 1 ил. S (Л

| Цифровой следящий умножитель частоты | 1977 |

|

SU634277A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Следящий умножитель частоты | 1979 |

|

SU840892A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-07—Публикация

1985-12-17—Подача