оо

О)

ел

ю

со

113

Изобретение относится к вы исли- тельной технике и может быть использовано для построения оперативных запоминающих устройств.

Целью изобретения является повышение надежности устройства

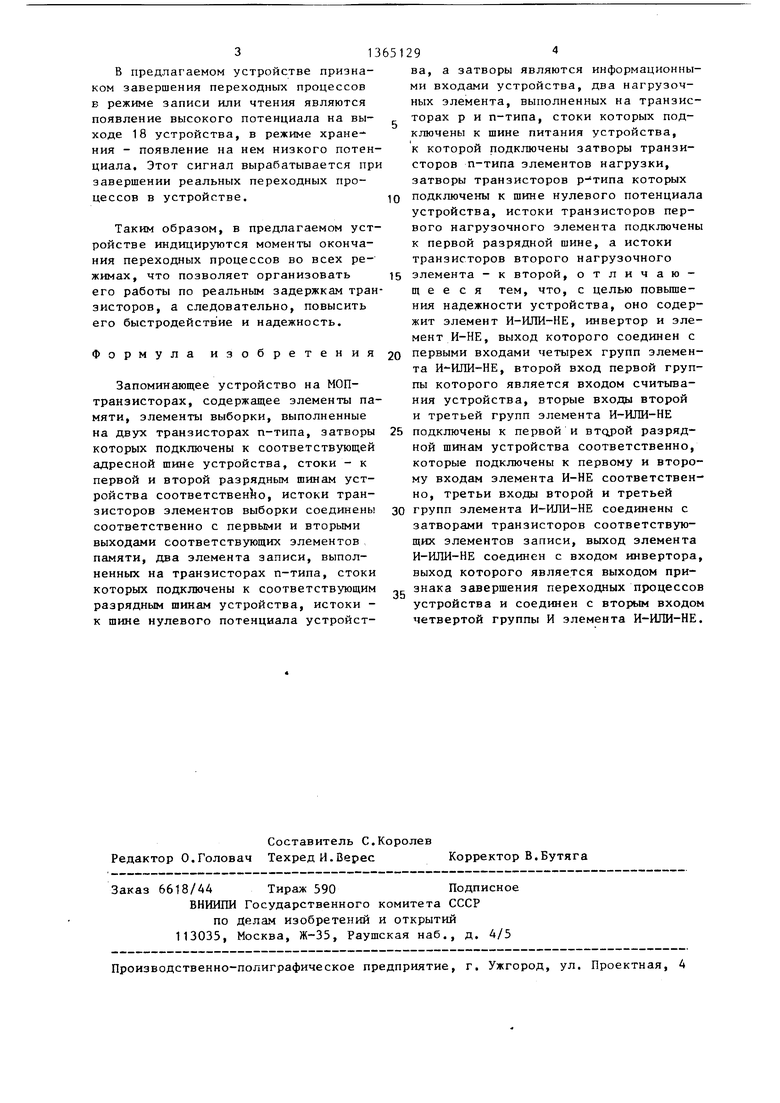

На чертеже приведена f:,. лма запоминающего устройства.

Устройство содержит элементы 1 памяти, элементы выборки на тоанзисгорах Z и

нэгрузочыые эл м янты на

транзисторах 4. 5 и 6, 7 соответственно; п-типа и р-типа, элементы записи на транзисторах 8 и 9, тлемент И-тИ-НЕ 10, элемент И-НЕ 11, инвертор 12, разрядные J и I ( и адресные 15 П ины,

Устройство нмеет пиформациоиш-ю входы 16 и 17, выхол 18 признака завершения npo i.eccoB и вход 19 счить - вания,

Запоминающее устройство работает с.педующим образом,

Б режиме хранеи --: на адресные шин 15 всех ячеек 1 подается низкий потенциал, закрывающий транз сторы 2 и 3, на вхоп 19 управ пения считывани ем - та1;же н зки Д noi енцялл. .-vie того, на оба ипформаи. - онных вход. 16 и 1/ подается низкий гтотунпиа.п., закрывающий транзисторы 8 и 9, Такшл образо . в pexaiNse хранения tiri тинах 13 -Ч 14 устанавливается высокий потенциал и н результате на выходе элемента 1 имеется низкий потенциал, на выходе элемента 10 - высокий потенциал, а на. выходе инвертора 12 и выходе 18 устройства - низкий, что свидетельс гвует о завершен ии переходных процессов в этом peniiMe,

3 реж№- е считывания информац1ги из элемента 1 на его адресную шину 15 подается .; .ысак1ГЙ потенциал, открывающий транз1к;торы 2 v 3, и низкий потенциал с ЕЬ1 ХОдов зтого элемента поступает на шияы 13 и 14, Одновременно подается высотсий потенциал на вход 19 считывания устройства. После jToro, как на ь.юде элемента 1 1 появляется высокий потенциал, на выходе элемента iO появляется низкий потен- циал, э затеи на выходе инвертора 12 и выходе 18 устройства - высокий, что явлнется признаком завершения переходных процессов в это режз-ме ,

В pe.-Aicie записи информации в ячейку 1 на ге адреснчпо 1 ; порается высокий потенциал, открывающий т :.-Н651

292

зисторы 2 и 3, и низкий потенциал с одного из выходов этого элемента 1 поступает на шину 16 или 17. Одновременно с этим на информационные входы 16 и 17 устройства выставляется записываемая информация, т.е. на один из них подается высокий потенциал, а на

другой

низкий, в результате чего

0

0

5

0

5

0

0

5

открывается один из транзисторов 8 или 9. Появление низкого потенциала на шине 13 или 14 приводит к тому, что на выходе элемента 11 появляется высокий потенциал. Если информация, /становленная на информационных входах 16 и 17 устройства, совпадает с ранее :э,яг1чсанной в ячейку 1 , то изме- iiei HH состояния последней не происхо- у-мт, II после того, как на выходе элемента 11 появляется высокий потенциал, tia 1 ыходе элемента 10 появляется };изкий потенциал, а затем на выходе инвертора 12 и выходе 18 устройства - высокий., что, как и в режиме ттения, является признаком завершения переходных процессов. информация, устанояленная на информационных входах 16 и 17 устройства, противоположна раке.с записанро т з элемент 1, происходит перек,гпоч(ииг последнего. Гри 3 j4iM, несмотря на высокий потен- Ц11ал на пь1ходе элемента 11, переключение элемента 10 не происходит до тех пор. пока в элементе i не устанавливается требуемое состояние. В этом случае сначала на обеих шинах

13и 14 появляется низкий потенциал, Затем, когда информация записывается в элемент 1, на одной из шин 13 или

14восстанавливается высокий потенциал. Только после этого на выходе элемента 10 появляется низкий потенциал, а на лыходе инвертора 12 и выходе 18 устройства - ВЫСОК1-1Й, что является признаком завершения переходных про- ;j:eccoB в режи йе записи.

Для того, чтобы вернуть устройство в режим хранения необходимо устано - вить низкий потенциал на адресной 15 злементз 1 и низкий потенциал на управляющем входе 19, если был режим считывания, или низкий потенциал Н1 5-шформационкых входах 16 и 17, усл ч был реж11м записи. В результате перехода в реж51м хранения на выходе 18 устанавливается низкий.потенциал, чтс является признаком завер)ления пе- рех1) процессов.

313651

В предлагаемом устройстве признаком завершения переходных процессов в режиме записи или чтения являются появление высокого потенциала на выходе 18 устройства, в режиме хранения - появление на нем низкого потенциала. Этот сигнал вырабатывается при завершении реальных переходных процессов в устройстве.10

Таким образом, в предлагаемом устройстве индицируются моменты окончания переходных процессов во всех режимах, что позволяет организовать его работы по реальным задержкам транзисторов, а следовательно, повысить его быстродейств ие и надежность.

Формула изобретения 20

Запоминающее устройство на МОП- транзисторах, содержащее элементы памяти, элементы выборки, выполненные на двух транзисторах п-типа, затворы которых подключены к соответствующей адресной шине устройства, стоки - к первой и второй разрядным шинам устройства cooTBeTCTBenko, истоки транзисторов элементов выборки соединены соответственно с первыми и вторыми выходами соответствующих элементов памяти, два элемента записи, выполненных на транзисторах п-типа, стоки которых подключены к соответствующим разрядным шинам устройства, истоки - к шине нулевого потенциала устройст

0

5

5

0

0

5

29

ва, а затворы являются информационными входами устройства, два нагрузочных элемента, выполненных на транзисторах р и п-типа, стоки которых подключены к шине питания устройства, к которой подключены затворы транзисторов п-типа элементов нагрузки, затворы транзисторов р- типа которых подключены к шине нулевого потенциала устройства, истоки транзисторов первого нагрузочного элемента подключены к первой разрядной шине, а истоки транзисторов второго нагрузочного элемента - к второй, отличающееся тем, что, с целью повышения надежности устройства, оно содержит элемент И-ИЛИ-НЕ, инвертор и элемент И-НЕ, выход которого соединен с первыми входами четырех групп элемента И ИЛИ-НЕ, второй вход первой группы которого является входом считьгаа- ния устройства, вторые входы второй и третьей групп элемента И-ИЛИ-НЕ подключены к первой и второй разрядной шинам устройства соответственно, которые подключены к первому и второму входам элемента И-НЕ соответственно, третьи входы второй и третьей групп элемента И-ИЛИ-НЕ соединены с затворами транзисторов соответствующих элементов записи, выход элемента И-ШШ-НЕ соединен с входом инвертора, выход которого является выходом признака завершения переходных процессов устройства и соединен с вторым входом четвертой группы И элемента И-ИЛИ-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство на МОП-транзисторах | 1986 |

|

SU1336112A1 |

| Запоминающее устройство на МОП-транзисторах | 1986 |

|

SU1411823A2 |

| Запоминающее устройство типа "очереди | 1987 |

|

SU1532977A1 |

| Запоминающее устройство | 1987 |

|

SU1474738A1 |

| Запоминающее устройство | 1987 |

|

SU1465911A1 |

| Магазинное запоминающее устройство | 1986 |

|

SU1472947A1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Элемент памяти | 1990 |

|

SU1786508A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения оперативных запоминающих устройств. Цель изобретения - повьппение надежности запоминающего устройства. Поставленная цель достигается введением в устройство элементов И ИЛИ-НЕ 10, И-НЕ 11 и инвертора 12 с соответствующими связями. Перечисленные элементы позволяют выработать сигнал завершения переходных процессов в устройстве, поэтому устройство работает по реальным задержкам транзисторов. 1 ил. с

| Запоминающее устройство | 1982 |

|

SU1109804A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Intel Memory Design Handbook | |||

| Способ изготовления зажимов конденсатора | 1919 |

|

SU3065A1 |

| Bovers Ave, St | |||

| Clare, c | |||

| Способ правки цилиндрических винтовых пружин | 1952 |

|

SU95051A1 |

| Способ и прибор для акустического исследования земных напластований | 1923 |

|

SU488A1 |

Авторы

Даты

1988-01-07—Публикация

1986-07-09—Подача