13

Изобретение относится к вычислительной технике, в частности к элементам памяти для запоминающих устройств.

Цель изобретения - повышение надежности элемента памяти.

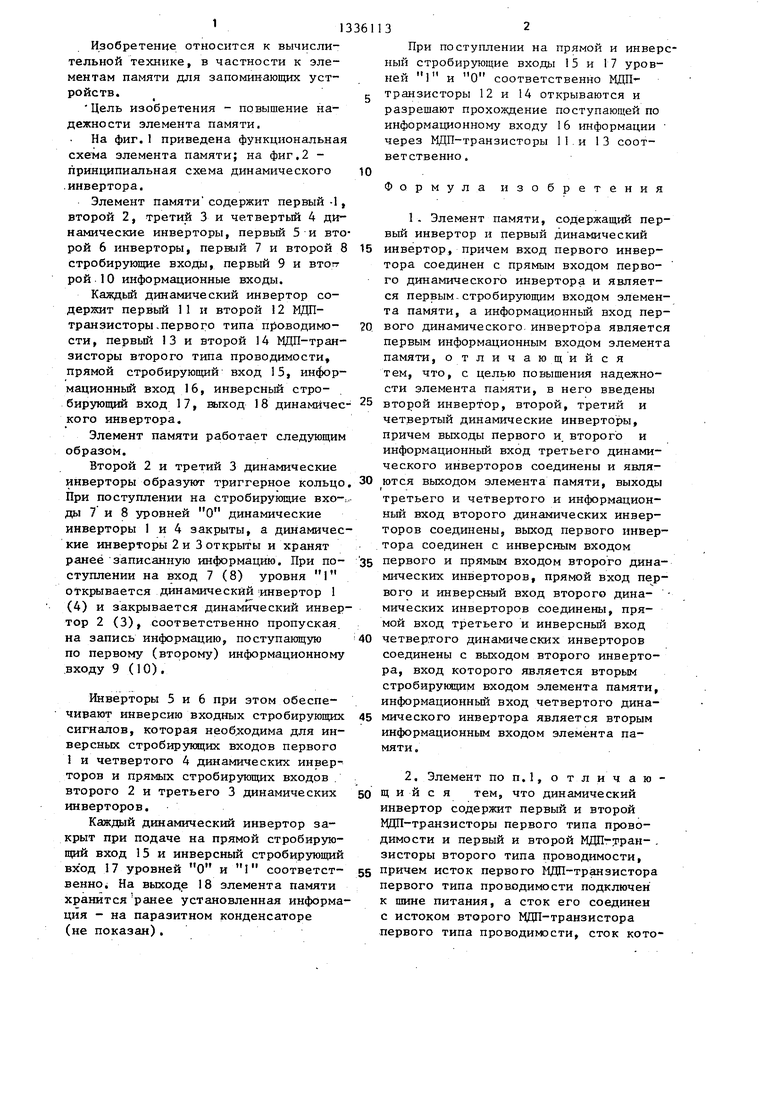

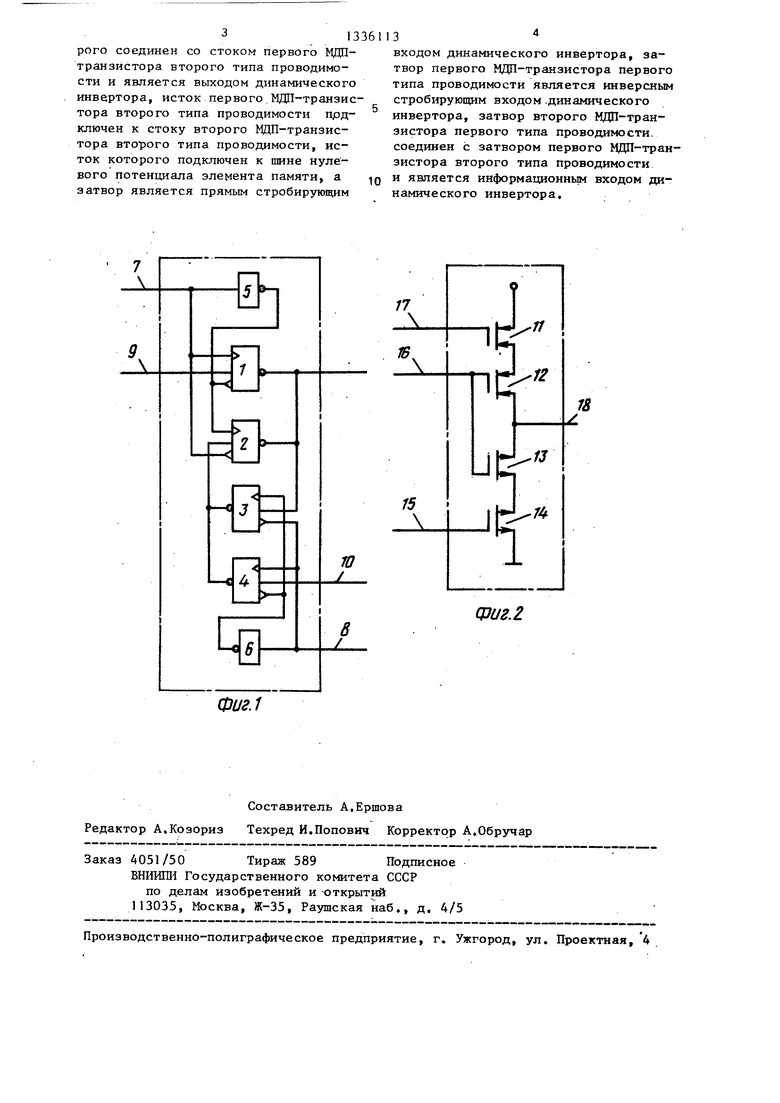

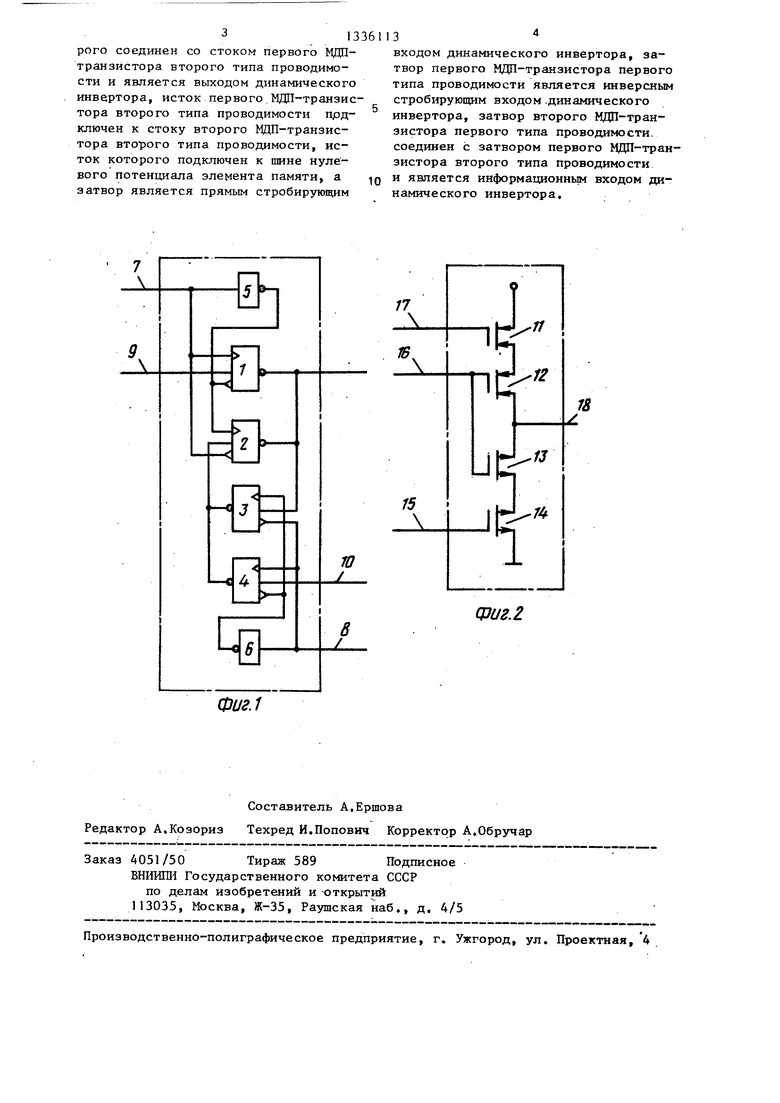

На фиг.1 приведена функциональная схема элемента памяти; на фиг,2 - принципиальная схема динамического .инвертора.

Элемент памяти содержит первый-1, второй 2, третий 3 и четвертый 4 динамические инверторы, первый 5 и второй 6 инверторы, перН)1Й 7 и второй 8 стробирующие входы, первый 9 и втоп- рой 10 информационные входы.

Каждьй динамический инвертор содержит первый 1 1 и второй 12 ЩЩ- транзисторы.первого типа проводимо- сти, первьй 13 и второй 4 МДП-тран- зисторы второго типа проводимости, прямой стробирующий вход 15, инфор- мационньй вход 16, инверсньй стро- бирующий вход 17, выход 18 динамичес кого инвертора.

Элемент памяти работает следующим образом.

Второй 2 и третий 3 динамические инверторы образуют триггерное кольцо При поступлении на стробирующие входы 7 и 8 уровней О динамические инверторы 1 и 4 закрыты, а динамические инверторы 2 и 3 открыты и хранят ранее записанную информацию. При по- ступлении на вход 7(8) уровня I открывается динамический ;инвертор 1 (4) и закрывается динамический инвертор 2 (3), соответственно пропуская. на запись информацию, поступающую по первому (второму) информационному .входу 9 (10).

Инверторы 5 и 6 при этом обеспечивают инверсию входных стробирующих сигналов, которая необходима для инверсных стробирующих входов первого 1 и четвертого 4 динамических инверторов и прямых стробирующих входов . второго 2 и третьего 3 динамических инверторов.

Каждый динамический инвертор закрыт при подаче на прямой стробирующий вход 15 и инверсный стробирующий вх од 17 уровней О и 1 соответст- венно. На вькоде 18 элемента памяти хранится ранее установленная информация - на паразитном конденсаторе (не показан).

32

При поступлении на прямой и инверсный стробирующие входы 15 и 17 уровней 1 и О соответственно МДП- транзисторы 12 и 14 открываются и разрешают прохождение поступающей по информационному входу 16 информации через МДП-транзисторы 11. и 13 соответственно.

Формула изобретения

1.Элемент памяти, содержащий первый инвертор и первый динамический инвертор, причем вход первого инвертора соединен с прямым входом первого динамического инвертора и является первым.стробирующим входом элемента памяти, а информационный вход первого динамического, инвертора является первым информационным входом элемента памяти, отличающийся

тем, что, с целью повышения надежности элемента памяти, в него введены второй инвертор, второй, третий и четвертый динамические инверторы, причем выходы первого и. второго и информационный вход третьего динамического инверторов соединены и являются выходом элемента памяти, выходы третьего и четвертого и информационный вход второго динамических инверторов соединены, выход первого инвертора соединен с инверсным входом первого и прямьш входом второго динамических инверторов, прямой вход первого и инверсный вход второго дина- - мических инверторов соединены, прямой вход третьего и инверсный вход четвертого динамических инверторов соединены с выходом второго инвертора, вход которого является вторым стробирующим входом элемента памяти, информационный вход четвертого динамического инвертора является вторым информационным входом элемента памяти .

2.Элемент по п.1, отличающий с я тем, что динамический инвертор содержит первый и второй МДП-транзисторы первого типа прюво- димости и первый и второй МДП тран- . зисторы второго типа проводимости, причем исток первого МДП-транзистора первого типа проводимости подключен

к шине питания, а сток его соединен с истоком второго ВДП-транзистора первого типа проводимости, сток кото313

рого соединен со стоком первого МДП- транзистора второго типа проводимости и является выходом динамического инвертора, исток первого МДП-транзис тора второго типа проводимости прд- ключен к стоку второго НЦП-транзис- тора второго типа проводимости, исток которого подкпючен к шине нулевого потенциала элемента памяти, а затвор является прямым стробирующим

входом динамического инвертора, затвор первого МДП-транзистора первого типа проводимости является инверсным стробирующим входом .динамического инвертора, затвор второго МДП-транзистора первого типа проводимости, соединен с затвором первого МДП-транзистора второго типа проводимости и является информационньм входом динамического инвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи информации в МДП динамический-матричный накопитель | 1982 |

|

SU1091222A1 |

| Запоминающее устройство | 1987 |

|

SU1465911A1 |

| Запоминающее устройство | 1986 |

|

SU1372357A1 |

| Управляемый мажоритарный элемент | 1981 |

|

SU993479A1 |

| Накопитель для оперативного запоминающего устройства | 1986 |

|

SU1376118A1 |

| Усилитель считывания (его варианты) | 1983 |

|

SU1137923A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1494041A1 |

| Параллельный дешифратор на допол-НяющиХ Мдп-ТРАНзиСТОРАХ" | 1978 |

|

SU798997A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Логический элемент | 1983 |

|

SU1148114A1 |

Изобретение относится к вычислительной технике, в частности к эле1«нтам памяти на КМОП-транзисто- jsax. Цель изобретения - повышение надежности и упрощение схемы элемента памяти, расширение функциональных возможностей элемента памяти за счет включения второго направления записи информации. Поставленная цель достигается тем, что в элемент памяти введе- ны второй инвертор, второй, третий и четвертый динамические инвер торы, содержащие первый и второй,МДП-транзис- торы первого типа проводимости н первый и второй МДП-транзисторы вто-, рого типа проводимости с соответстг- вующнми связями,.это позволяет проектировать регистровые структуры с двумя направлениями записи, сдвиговые регистры и счетчики с параллельной записью при минимальных аппаратурных затратах, так как не требуется совмещения отключения обратной связи в триггере при первом и;втором, режимах записи. 1 з,п, фг-лы, 2 ил. (Л

Фиг.1

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-11—Подача