„13

Изобретение относится к вычислительной технике.

Цель изобретения - расширение iliyii- кциональных возможностей за счет pea- лизации доступа к устройству абонентов с удвоенной длиной слова.

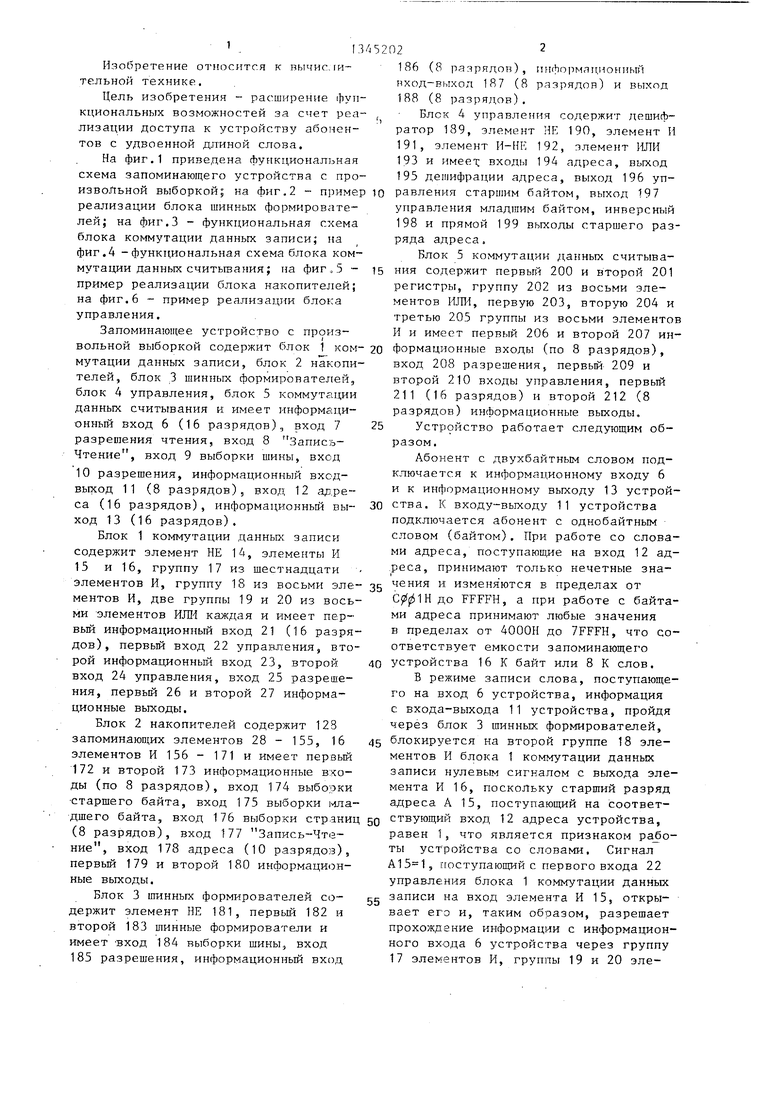

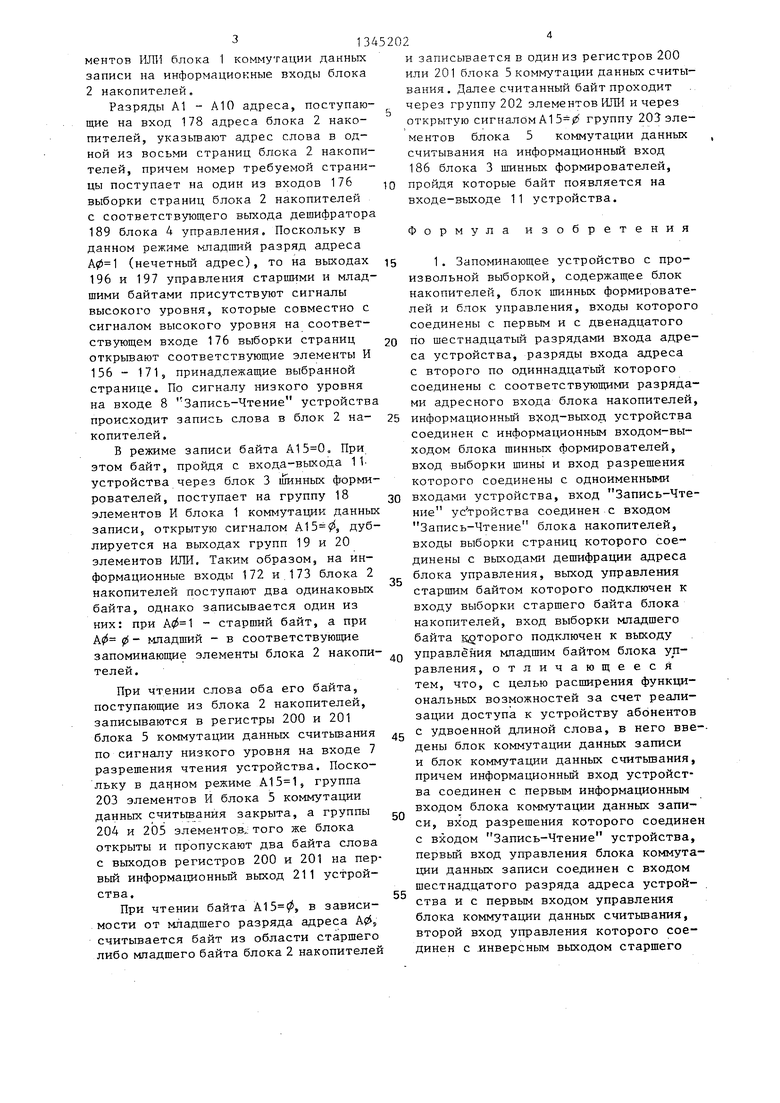

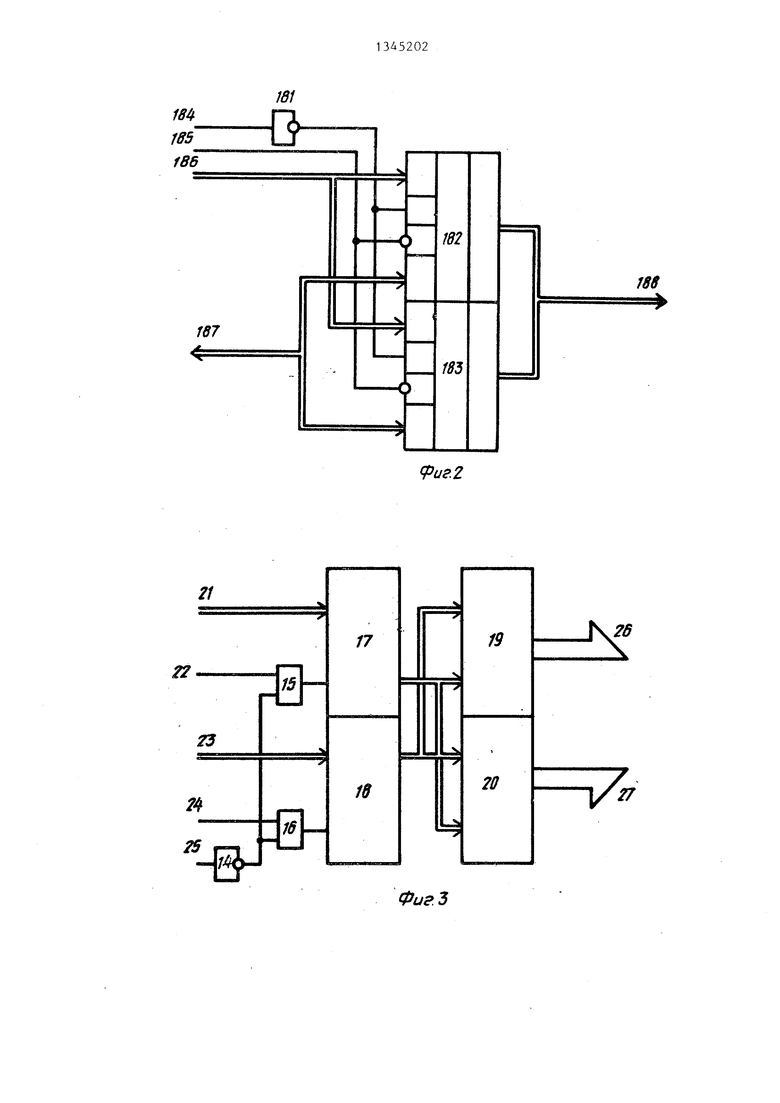

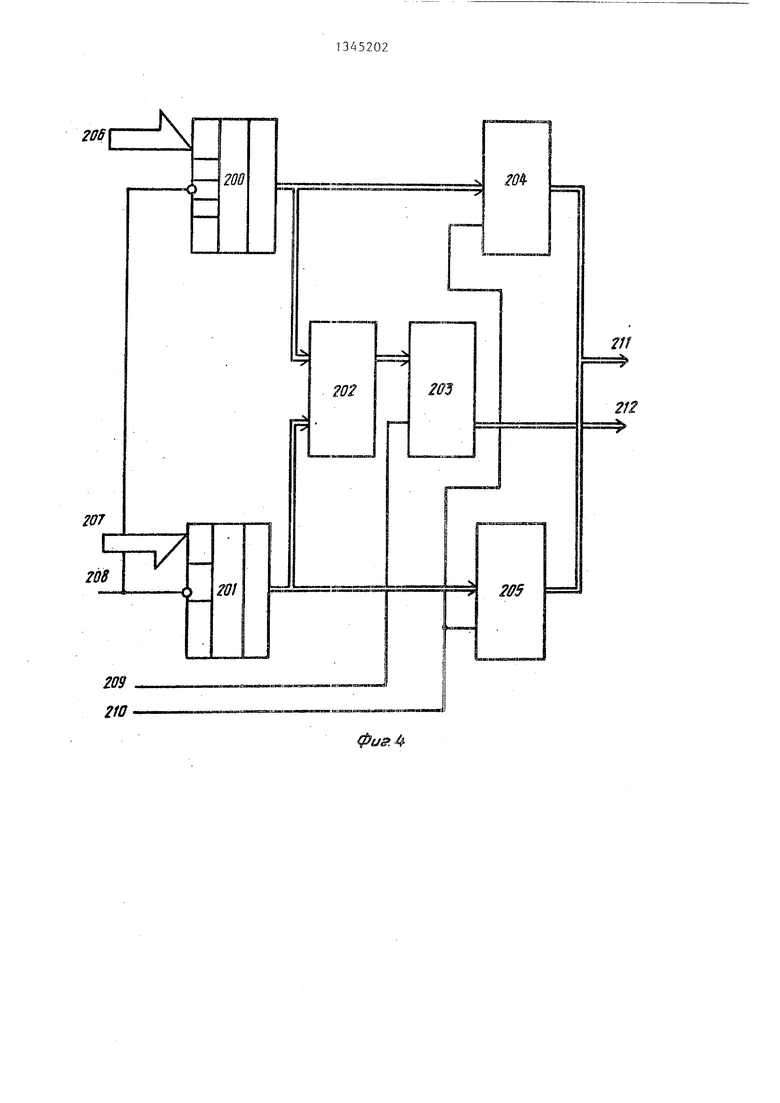

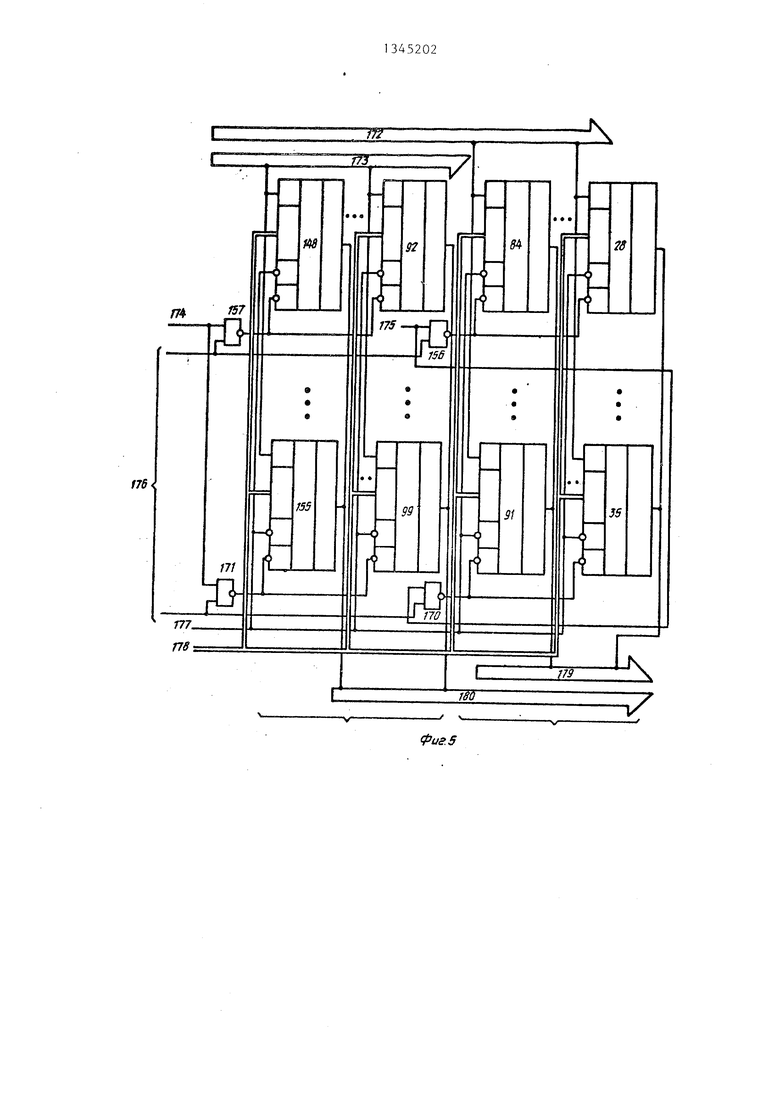

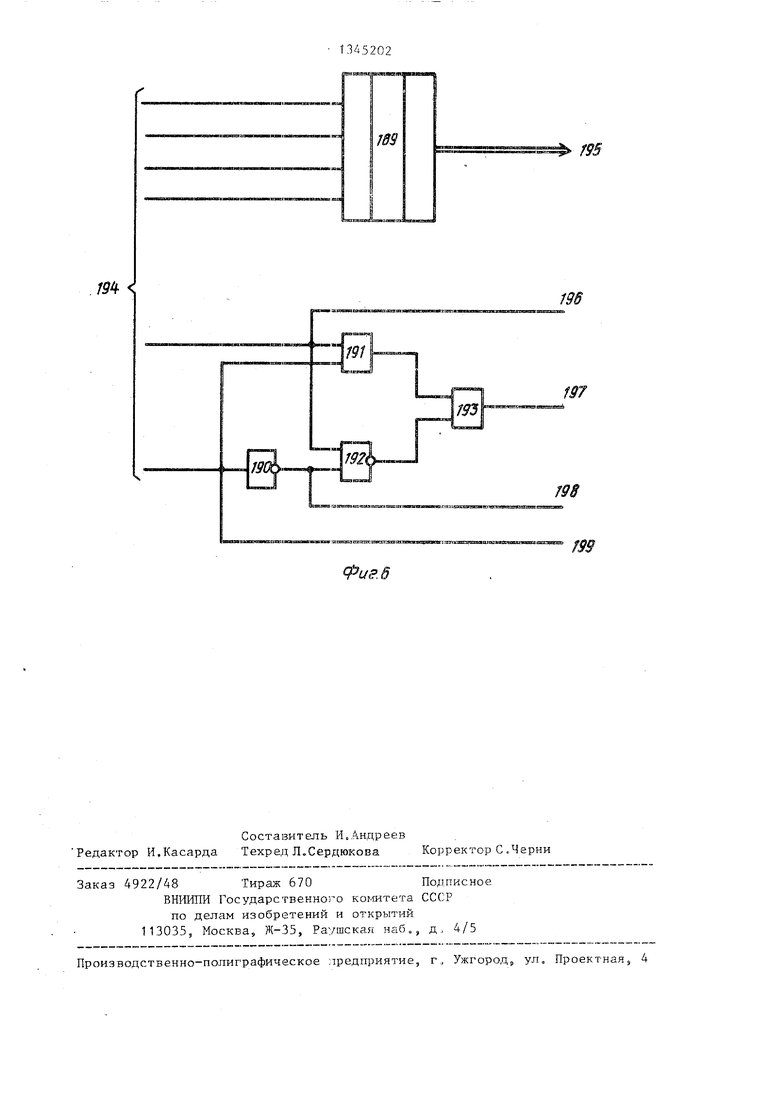

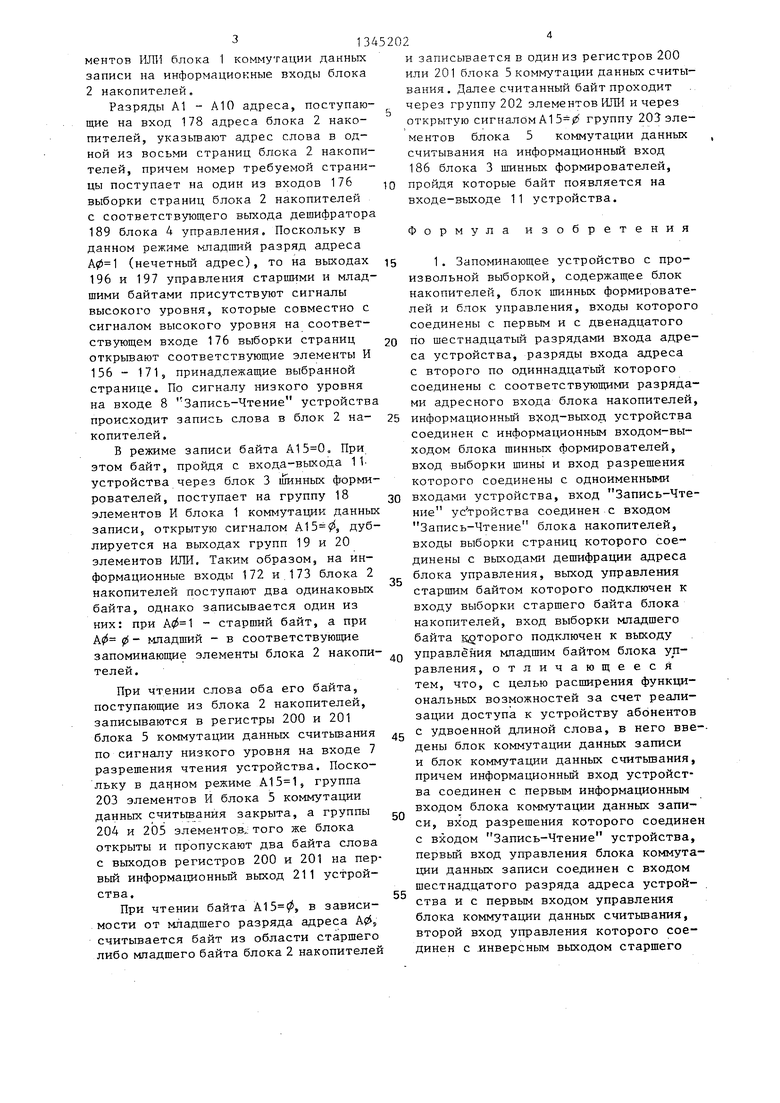

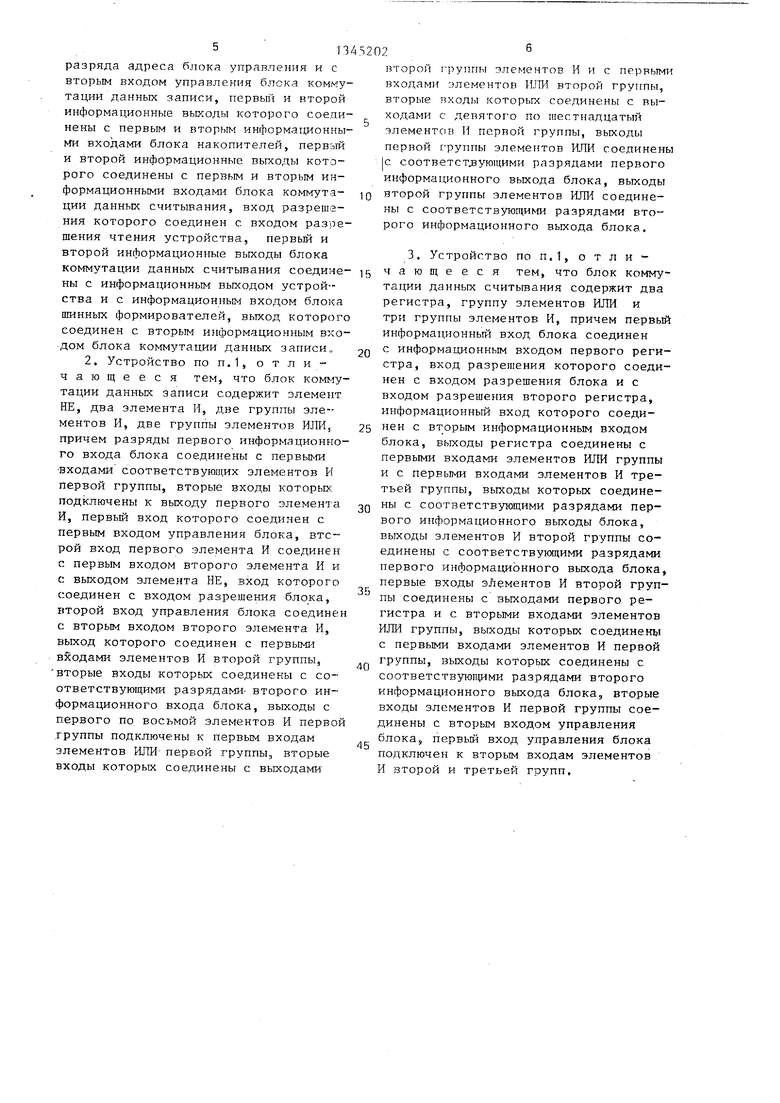

На фиг.1 приведена функциональная схема запоминающего устройства с произвольной выборкой; на фиг. 2 - п 5имер реализации блока шинных формирователей; на фиг.З - функциональная схема блока коммутации данньгх записи; на фиг.4 -функциональная схема блока коммутации данных считьгоания; на фиг„5 - пример реализации блока накопителей; на фиг.6 - пример реализации блока управления.

Запоминающее устройство с произвольной выборкой содержит блок 1 ком- мутации данньгх записи, блок 2 накопителей, блок 3 шинных формирователей, блок 4 управления, блок 5 коммутации данных считывания и имеет информационный вход 6 (16 разрядов), вход 7 разрешения чтения, вход 8 Запись- Чтение, вход 9 выборки шины, вход 10 разрешения, информационный вход- вьпсод 11 (8 разрядов), вход 12 ад,ре- са (16 разрядов), информационный вы- ход 13 (16 разрядов).

Блок 1 коммутации данньк записи содержит элемент НЕ 14, элементы И 15 и 16, группу 17 из шестнадцати элементов И, группу 18 из восьми эле- ментов И, две группы 19 и 20 из восьми элементов ИЛ- каждая и имеет первый информационный вход 21 (16 разрядов), первый вход 22 управления, второй информационный вход 23, второй вход 24 управления, вход 25 разрешения, первый 26 и второй 27 информационные выходы.

Блок 2 накопителей содержит 128 запоминающих элементов 28 - 155, 16 элементов И 156 - 171 и имеет первый 172 и второй 173 информационные входы (по 8 разрядов), вход 174 выборки старшего байта, вход 175 выборки младшего байта, вход 176 выборки страниц (8 разрядов), вход 177 Запись-Чтение, вход 178 адреса (10 разрядов), первый 179 и второй 180 информационные выходы.

Блок 3 шинных формирователей со- держит элемент НЕ 181, первый 182 и второй 183 шинные формирователи и имеет -вход 184 выборки шины, вход 185 разрешения, информационный вх(5Д

22

186 (8 разрядов), ииформл ;нониьп1 вход-выход 187 (8 разрядов) и выход 188 (8 разрядов).

Блок 4 управления содержит дешифратор 189, элемент ИР 190, элемент И 191, элемент И-НК 192, элемент ИЛИ 193 и имеет; входы 194 адреса, выход 195 дешифрации адреса, выход 196 управления старшим байтом, выход 197 управления младшим байтом, инверсный 198 и прямой 199 выходы старшего разряда адреса.

Блок 5 коммутации данньгх считывания содержит первьт 200 и второй 201 регистры, группу 202 из восьми элементов ИШ-1, первую 203, вторую 204 и третью 205 группы из восьми элементов И и имеет первый 206 и второй 207 информационные входы (по 8 разрядов), вход 208 разрешения, первый 209 и второй 210 входы управления, первый 211 (16 разрядов) и второй 212 (8 разрядов) информационные выходы.

Устройство работает следующим образом.

Абонент с двухбайтным словом подключается к информационному входу 6 и к информационному выходу 13 устройства. К входу-выходу 11 устройства подключается абонент с однобайтным словом (байтом), При работе со словаи адреса, поступающие на вход 12 ад- реса, принимают только нечетные значения и изменя ются в пределах от до FFFFH, а при работе с байтами адреса принимают любые значения в пределах от 4000Н до 7FFFH, что соответствует емкости запоминающего устройства 16 К байт или 8 К слов.

В режиме записи слова, поступающего на вход 6 устройства, информация с входа-выхода 11 устройства, пройдя через блок 3 шинных формирователей, блокируется на второй группе 18 элементов И блока 1 коммутации данных записи нулевым сигналом с выхода элемента И 16, поскольку старший разряд адреса А 15, поступающий на соответствующий вход 12 адреса устройства, равен 1, что является признаком ть устройства со словами. Сигнал поступающий с первого входа 22 управления блока 1 коммутации данных записи на вход элемента И 15, открывает его и, таким образом, разрешает прохождение информации с информационного входа 6 устройства через группу 17 элементов И, группы 19 и 20 элементов lUW блока 1 коммутации данных записи на информациокные входы блока 2 накопителей.

Разряды А1 - А10 адреса, поступающие на вход 178 адреса блока 2 накопителей, указьшают адрес слова в одной из восьми страниц блока 2 накопителей, причем номер требуемой страницы поступает на один из входов 176 выборки страниц блока 2 накопителей с соответствующего выхода дешифратора 189 блока 4 управления. Поскольку в данном режиме младший разряд адреса (нечетный адрес), то на выходах 196 и 197 управления старшими и младшими байтами присутствуют сигналы высокого уровня, которые совместно с сигналом высокого уровня на соответствующем входе 176 выборки страниц открьшают соответствующие элементы И 156 - 171, принадлежащие выбранной странице. По сигналу низкого уровня на входе 8 Запись-Чтение устройства происходит запись слова в блок 2 накопителей.

В режиме записи байта При этом байт, пройдя с входа-выхода 11. устройства через блок 3 шинных формирователей, поступает на группу 18 элементов И блока 1 коммутации данных записи, открытую сигналом , дублируется на выходах групп 19 и 20 элементов ИЛИ. Таким образом, на информационные входы 172 и 173 блока 2 накопителей поступают два одинаковых байта, однако записывается один из них: при - старший байт, а при ф ф - младший - в cooтвeтcтвyюшд e запоминающие элементы блока 2 накопителей.

При чтении слова оба его байта, поступающие из блока 2 накопителей, записываются в регистры 200 и 201 блока 5 коммутации данных считьшания по сигналу низкого уровня на входе 7 разрешения чтения устройства. Поскольку в дачном режиме , группа

203элементов И блока 5 коммутации данных считывания закрыта, а группы

204и 205 элементов,: того же блока открыты и пропускают два байта слова с выходов регистров 200 и 201 на первый информационный выход 211 устройства.

При чтении байта , в зависимости от младшего разряда адреса , считывается байт из области старшего либо младшего байта блока 2 накопителей

и записывается в один из регистров 200 или 201 блока 5 коммутации данных считывания. Далее считанный байт проходит через группу 202 элементов ИЛИ и через открытую сигналом А1 5- группу 203 элементов блока 5 коммутации данных считывания на информационный вход 186 блока 3 шинных формирователей, пройдя которые байт появляется на входе-выходе 11 устройства.

Формула изобретения

5

0

5

0

0

5

1. Запоминающее устройство с произвольной выборкой, содержащее блок накопителей, блок шинных формирователей и блок управления, входы которого соединены с первым и с двенадцатого по шестнадцатый разрядами входа адреса устройства, разряды входа адреса с второго по одиннадцатый которого соединены с соответствуюш тми разрядами адресного входа блока накопителей, информационный вход-выход устройства соединен с информационным входом-выходом блока шинных формирователей, вход выборки шины и вход разрешения которого соединены с одноименными входами устройства, вход Запись-Чтение ус тройства соединен с входом Запись-Чтение блока накопителей, входы выборки страниц которого соединены с выходами дешифрации адреса блока управления, выход управления старшим байтом которого подключен к входу выборки старшего байта блока накопителей, вход выборки младшего байта которого подключен к выходу Q управления младшим байтом блока управления, отличающееся тем, что, с целью расширения функциональных возможностей за счет реализации доступа к устройству абонентов с удвоенной длиной слова, в него вве-- дены блок коммутации данных записи и блок коммутапд и данных считьшания, причем информационный вход устройства соединен с первым информационным входом блока коммутации данных записи, вход разрешения которого соединен с входом Запись-Чтение устройства, первый вход управления блока коммутации данных записи соединен с входом шестнадцатого разряда адреса устройства и с первым входом управления блока коммутации данных считьшания, второй вход управления которого соединен с .инверсным выходом старшего

5

5

513

разряда адреса блока управления и с вторым входом управления блока коммутации данных записи, первьй и второй информационные выходы которого соединены с первым и втор1 гм информационными входами блока накопителей, первый и второй информационные выходы которого соединены с первым и вторым информационными входами блока коммутации данных считывания, вход разрешения которого соединен с входом разрешения чтения устройства, перньш и второй информационные выходы блока коммутации данных считьгаания соединены с информационным выходом устройства и с информационным входом блока шинных формирователей, выход которого соединен с вторым информационным входом блока коммутации данных записи,, 2. Устройство по П.1, от л и - чающееся тем, что блок коммутации данных записи содержит элемент НЕ, два элемента И, две группы элементов И, две группы элементов ИТШ, причем разряды первого информационного входа блока соединены с первыми Входами соответствующих элементов И первой группы, вторые входы которых: подключены к выходу первого элемента И, первый вход которого соединен с первым входом управления блока, второй вход первого элемента И соединен с первым входом второго элемента И и с выходом элемента НЕ, вход которого соединен с входом разрешения блока, второй вход управления блока соединен с вторым входом второго элемента И, выход которого соединен с первыми входами элементов Ji второй группы, вторые входы которых соединены с соответствующими разрядами- второго информационного входа блока, выходы с первого по восьмой элементов И первой группы подключены к первым входам элементов ИЛИ первой группы,, вторые входы которых соединены с выходами

3202

второй г руппы элементов И и с первыми входами элементов ИЛИ второй группы, вторые пходь которых соединены с выходами с девятог о по шестнадцатый элементов И первой группы, выходы первой г руппы элементов КПИ соединены с соответст;вую1цими разрядами первого информационного выхода блока, выходы второй группы элементов ИЛИ соединены с соответствующими разрядами второго информационного выхода блока.

3. Устройство по п,1, о т л и чающееся тем, что блок коммутации данных считывания содержит два регистра, группу элементов ИЛИ и три группы элементов И, причем первый информационный вход блока соединен

с информационным входом первого регистра, вход разрешения которого соединен с входом разрешения блока и с входом разрешения второго регистра, информационный вход которого соедииен с информационным входом блока, выходы регистра соединены с первыми входами элементов ИЛИ группы и с первыми входами элементов И третьей группы, выходы которых соединены с соответствующими разрядами первого информационного выходы блока, выходы элементов И второй группы соединены с соответствующими разрядами первого информационного вькода блока, первые входы элементов И второй группы соединены с выходами первого регистра и с вторыми входами элементов ИЛИ группы, выходы которых соединен) с первыми входами элементов И первой группы, выходы которых соединены с соответствующими разрядами второго информационного выхода блока, вторые входы элементов И первой группы соединены с вторым входом управления блока, первый вход управления блока

подключен к вторым входам элементов И второй и третьей групп.

ue.Z

17

19

JV

22

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода-вывода информации | 1987 |

|

SU1451674A1 |

| Запоминающее устройство | 1987 |

|

SU1443029A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

| Запоминающее устройство с произвольной выборкой | 1988 |

|

SU1548790A1 |

| Устройство для адресации памяти | 1990 |

|

SU1741142A1 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| Устройство для программного управления технологическими процессами | 1989 |

|

SU1633377A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Устройство для сопряжения микропроцессорных внешних устройств с каналом ввода-вывода ЭВМ | 1985 |

|

SU1278871A1 |

| НАКОПИТЕЛЬ ЦИФРОВОЙ ИНФОРМАЦИИ | 2002 |

|

RU2236710C2 |

Изобретение относится к вычислительной технике и может быть использовано в технике микро-ЭВМ при сопряжении 8-разрядного микропроцессора с 16-разрядными абонентами. Целью изобретения является расширение функциональных возможностей запоминающего устройства с произвольной выборкой за счет реализации доступа к устройству абонентов с удвоенной (двухбайт ной) длиной информационного слова. Поставленноя цель достигнута путем введения в запоминающее устройство блоков 1 и 5 коммутации данных записи и считывания, управляемых неиспользуемыми младшим и старшим разрядами входа 12 адреса. 2 з.п. ф-лы, бил. I (Л (puei

2

25

19

20

Фиг. 5

20В

200

202

208

т

209 210

//74

2П

20

212

205

172

N

J80

V

т

189

т

196

198

Фиаб

Составитель И.Андреев Редактор И.Касарда Техред Л,Сердюкова Корректор С .Черни

Заказ 4922/48 Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб, д, 4/5

Производственно-полиграфическое предприятие, г, Ужгород уЛо Проектная, 4

| Полупроводниковые запоминающие устройства и их применение | |||

| Под ред | |||

| А.ЮоГордонова | |||

| - М.: Радио и связь, 1981, с | |||

| Способ получения жидкой протравы для основных красителей | 1923 |

|

SU344A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ приготовления пищевого продукта сливкообразной консистенции | 1917 |

|

SU69A1 |

Авторы

Даты

1987-10-15—Публикация

1986-06-19—Подача