Иэобретемие отиосится к 1.н:-.п;нгли- тельной технике и может 6i,iT, мспо. п, - зовано при разработке с:лецка/1изкра-- ванных и универсальных вычисмп-гтельгс.п устройств, предназнач:ен:ныл для обработки ц):- фррвой информации „

Цель изобретения - ; овьп1 С ир быстродействия устройства.

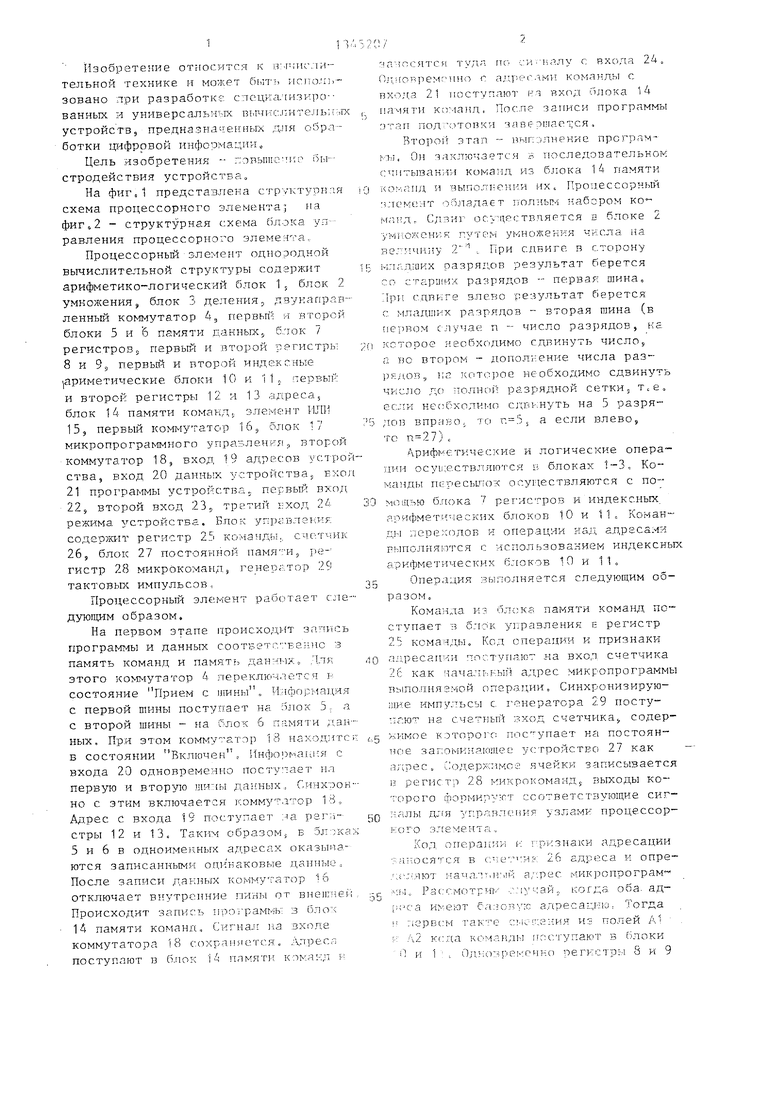

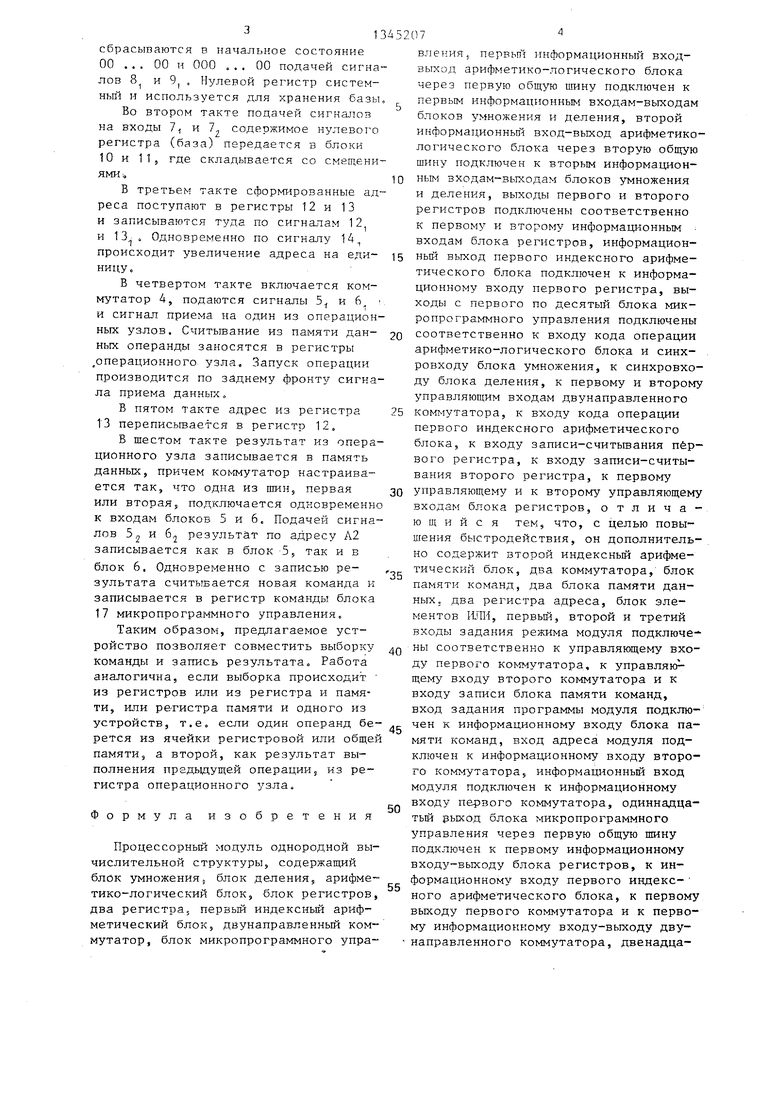

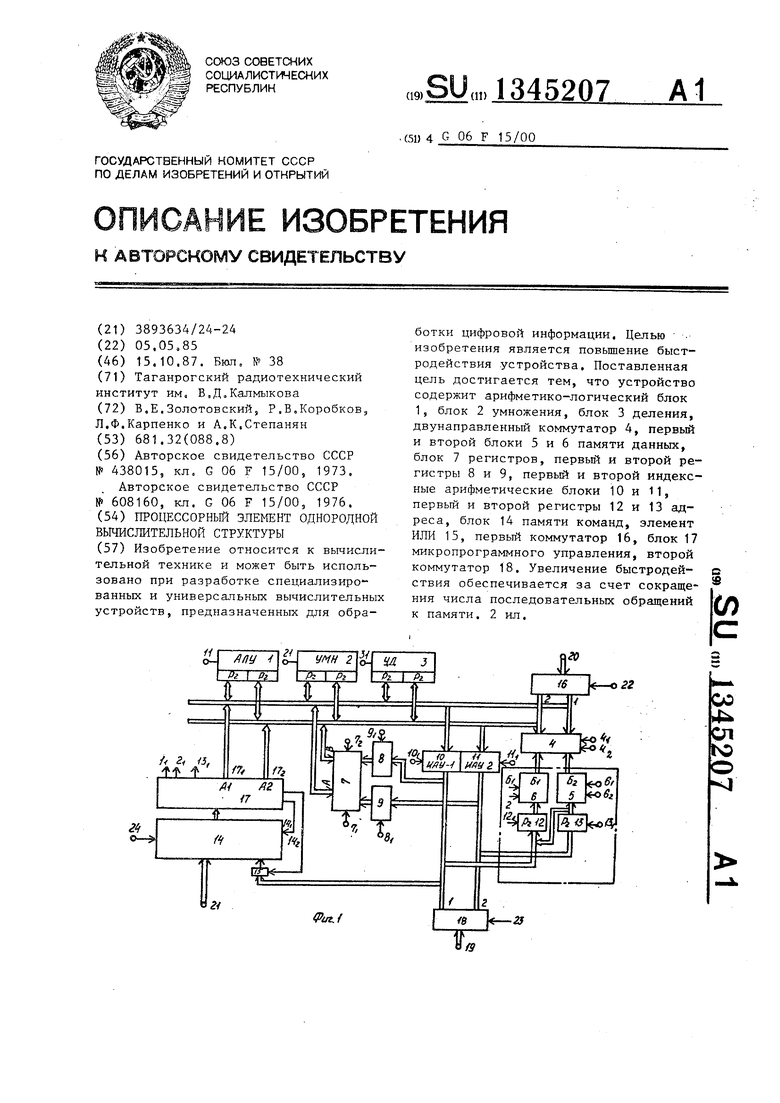

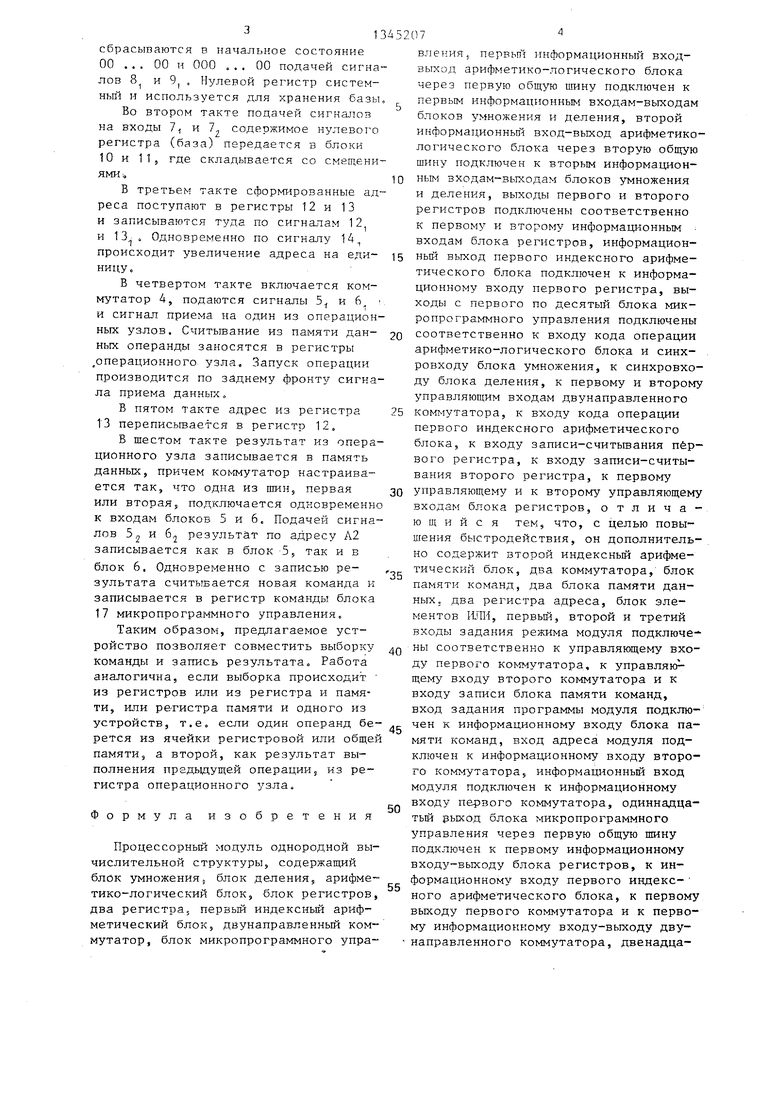

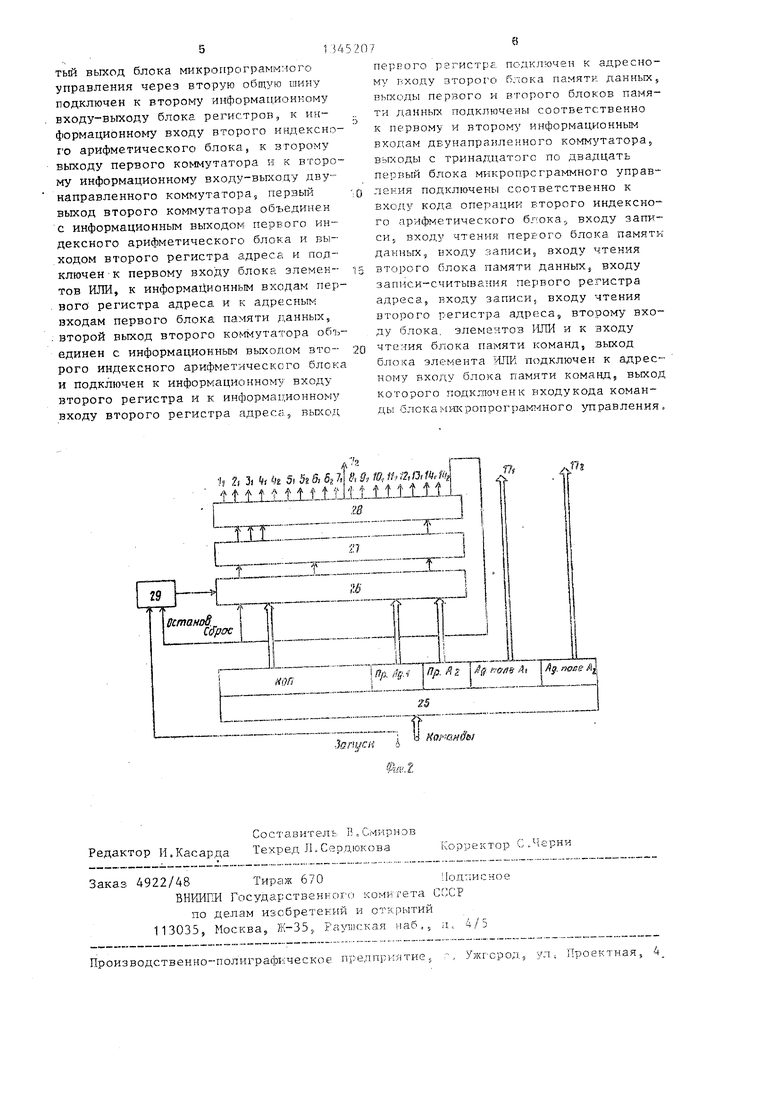

На фиг, 1 представлена стр у ктуртпя схема процессорного элемента; на фиг S 2 - структурная схема уп-- равления процессорного элемента.

Процессорный элемент однородной вычислительной структуры содержит арифметико-логический блок 1, блок 2 умножения, блок 3 деления,, дзунаправленньм коммутатор 4, первьп-: -л второй блоки 5 и 6 памяти данных, б.лок 7 регистров, первый и второй регистрь: 8 и 9, первый и второй индекснь е ариметические блоки 10 и 11,. первый и второ-й регистры 12 и 13 адреса; блок 14 памяти команд элемент ИЛИ 15, первый коммутатор 16, блок 17 микропрограммного упраьлени я, второй коммутатор 18, вход 19 адресов устройства, вход 20 данных устройства« вход 21 программы устройства., псрвьш вход 22, второй вход 23 5 третий ::ход 24 режима устройства. Блок упр;;влекия содержит регистр 25 ко;панды,, счктчик 26, блок 27 постоянной намя - и, ре- гистр 28 микрокоманд, генер;;;тор 29 тактовьпс импульсов,

Процессорньш элемент работает с ле- дующим образом.

На первом этапе происходит запись програ№-1Ы и данных соотБетг/; Ееннс з память команд и памят, данных, Ллк этого комдчутатор 4 лереключлйтся Р состояние Прием с ишны, ИисЬормадия с первой шины поступает на блок 5, а с второй ШИВЫ - на блок 6 данных, При этом коммутатор 18 находите в состоянии Включен, Инфорт-итдия с входа 20 одновременно поступает на первую и вторую шилы данных, Синхэонно с этим включается комму атор 16, Ад:рес с входа 19 по(.;тупает ла стры 12 и 13, Таким o6pa30Mj Б 5л-;ках 5 и 6 в одноиме чНЬ х адресах оказываются записанными оци наковые .::1,анньге,, После записи данных коммутат 1р 6 отключает внутренние пины от внешнеГ; Происходит запчлсъ программь: з (Злох 14 памяти команп:,, Сигнаи на зхогге коммутатора 18 с охраняется, .; хлреся поступают в блок 14 плмятк команд v0

: а псятся туда по с и. налу с входа 24 Oji;(oFipe;-ic НПО г адр.еглмн команды с вхо,л,а 21 поступают К а вход блока 14 на-мяти Koi-iaiLH. После записи программы э ;-ап под ОТОПКИ завб01 1ае-;;ся ,

Второ1г этап - выполнение програм- N:hb Он заключается к последовательном считыван;ли комагьт :-13 блока 14 памяти и вь пол :с};ии их. Процессорный злемент обладает полньра набором ко м;1нд, Слзиг ос - це ;твпяртся в блоке 2 yMJiOKCHv K умножения числа на велмлину , При сдвиге в сторону .дших разря1:1,ов результат берется со стгф ких разрядов - первая шина, лри. сдвиге влево результат берется с младших разрядов - вторая шина (в первом случае п - число разрядов, на ; :оторое необходимо сдвинуть число, а во втором - дополг,ение числа раз- 1)ядов, }:а ji;oTC 5oe необходимо сдвинуть число до полноГ; разрядной сетки, т.е. если необходимо с тгплнуть на 5 разрядов вправо. TCi г. 55 а если влево, то ).

- pиф eт ;чecj гиe и логические опера- ИНН осупжствллются VI блоках 1-3. Ко- п( :ресьшо:-: осуг1;ествляются с помощью блока регистров и индексных арифмет1Г-1еских блоков 10 и 11 Команды лере;а)доБ и операции ка,1л адресами Р1-ЛПОЛНЯ10ТСЯ с использованием индексных, а рифметических блоков 10 и 1 .

Операция зыгю;гняется следующим образом.

Команда из б л.;; к а памяти команд по стунает з б.ло к уп равления Е регистр

25команды. Код операции и признаки , sj,pc;can u-i ппстунагс Т на вхол счетчика

26как -1ача..лг-л--.Ь1Й адрес микропрограммы выпо.1И{яемой операции. Синхронизирующие импульсы с 1 енератора 29 посту- гмт на зход счетчика содержимое которого пос -упает на постоянное заг;оми; ак1. иее устройстве. 27 как . ,е.ржиког ячейки записывается 13 регистр 28 микрокоманд выходы которого формиг1у гт соответст1 ующие сиг- малы ДоЛя ут1равлен1- .я узлами процессорного э (емента.,

Код оггераиии и признаки адресации ; ;июся л:я в сл;е - :ир; 26 адреса и опре- .лг.ляют мала.: .1;мй a/;pec мик ;1опрограм -;ьь Ра(л мотриг .. лучай,, когда оба. ад- р;ч. а имеют сазоп ук адресацию. Тогда и лервс:м гак Т е с:;.so сияния из полей А Л2 ксгга лг;С гупают Б блоки Пи 1 , Од};озоекснно пегк1;тпы S и 9

сбрасываются в начальное состояние 00 ... 00 н 000 ... 00 подачей сигналов 8 и 9, , Нулевой регистр систем- ньш и исполг зуется для хранения базы

Во втором такте подачей сигналов на входы 7 и 7 содержимое нулевого регистра (база) передается в блоки 10 и 11, где складывается со смещениями,

В третьем такте сформированные адреса поступают в регистры 12 и 13 и записываются туда по сигналам 12 и 13. Одновременно по сигналу 14 происходит увеличение адреса на еди- ницу.

В четвертом такте включается коммутатор 4, подаются сигналы 5 и 6, и сигнал приема на один из операционных узлов. Считывание из памяти дан- ньпс операнды заносятся в регистры операционного узла. Запуск операции производится по заднему фронту сигнала приема данных о

В пятом такте адрес из регистра 13 переписьшается в регистр 12,

В шестом такте результат из операционного узла записывается в память данных, причем ког-мутатор настраивается так, что одна из шин, первая или вторая, подключается одновременно к входам блоков 5 и 6. Подачей сигналов 5 2 и 6.2 результа.т по адресу А2 записывается как в блок 5, так и в блок 6, Одновременно с записью ре зультата считывается новая команда к записывается в регистр команды блока 17 микропрограммного управления.

Таким образом, предлагаемое устройство позволяет совместить выборку команды и запись результата Работа аналогична, если выборка происходит из регистров или из регистра и памяти, или регистра памяти и одного из устройств, т.е. если один операнд бе- рется из ячейки регистровой или общей памяти, а второй, как результат выполнения предыдущей операции, из регистра операционного узла.

Формула изобретения

Процессорный модуль однородной вычислительной структуры, содержащий блок умножения, блок деления, арифметико-логический блок, блок регистров, два регистра; первый индексньй арифметический блок, двунаправленный коммутатор, блок микропрограммного упрад

5

0

5

о

Q

0

5

101

БлетшЯ;, первьй информационный вход- выход арифметико-логического блока через первую общую шину подключен к первьЕм информационным входам-выходам блоков умножения и деления, второй информационньй вход-выход арифметико- логического блока через вторую общую шину подключен к вторым информацион- ньм входам-выходам блоков умножения и деления, выходы первого и второго регистров подключены соответственно к первому и второму информационным входам блока регистров, информационный выход первого индексного арифметического блока подключен к информационному входу первого регистра, выходы с первого по десятый блока микропрограммного управления подключены соответственно к входу кода операции арифметико-логического блока и синх- . ровходу блока умножения, к синхровхо- ду блока деления, к первому и второму управляющим входам двунаправленного коммутатора, к входу кода операции первого индексного арифметического блока, к входу записи-считьюания первого регистра, к входу записи-считывания второго регистра, к первому управляющему и к второму управляющему входам блока регистров, отличающийся тем, что, с целью повышения быстродействия, он дополнительно содержит второй индексный арифметический блок, два коммутатора, блок памяти команд, два блока памяти данных, два регистра адреса, блок элементов 1ШИ, первый, второй и третий входы задания режима модуля подключе- ны соответственно к управляющему входу первого коммутатора, к управляющему входу второго коммутатора и к входу записи блока памяти команд, вход задания программы модуля подклю- чен к информационному входу блока памяти команд, вход адреса модуля подключен к информационному входу второго коммутатора, информационньй вход модуля подключен к информационному входу первого коммутатора, однннадца- тьм рыход блока микропрограммного управления через первую общую шину подключен к первому информационному входу-выходу блока регистров, к информационному входу первого индекс- него арифметического блока, к первому выходу первого коммутатора и к первому информационному входу-выходу дву направленного коммутатора, двенадцатьй выход блока микропрограмм: ого управления через вторую общую шину подключен к BTopONry информационному входу-выходу блока, регистров, к информационному входу второго индексного арифметического блока, к второму выходу первого коммутатора и к втсфо- му информационном входу-вькоду дву нацравленного коммутатора, пер:аый выход второго коммутатора объединен с информационным выходом первого индексного арифметического блока и выходом второго регистра адреса и подключен к первому входу блока элементов ИЛИ, к информационным входам первого регистра адреса и к адресным входам первого блока памяти данных, второй выход второго коммутатора объ- единен с информационным выходом второго индексного арифметического блока и подключен к информационному входу второго регистра и к: информационному входу второго регистра адреса, выход

0

первого регистре, подключен к адресному рходу второго блока памяти данных, выходы первого и второго блоков памяти данных подключены соответственно к первому и второму информационным входам двунаправленного коммутатора, выходы с тринадцатого по двадцать первый блока митфопрсграммного управления подключены соответственно к входу кода операции второго индексного арифметического входу записи, входу чтения перрого блока памяти данных, входу записи, входу чтения второго блока памяти данныхj входу записи-считывания первого регистра адреса, входу записи, входу чтений второго регистра адреса, второму входу блока, элементов ИЛИ и к входу чтения блока памяти команд, выход блока элемента ЖК подключен к адресному входу блока памяти команд, выход которого подключен к входу кода команды блокамш ропрогра№- ного управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки нечеткой информации | 1985 |

|

SU1564603A1 |

| Программируемый процессор спектральной обработки сигналов | 1982 |

|

SU1092517A1 |

| КОНВЕЙЕРНЫЙ ПРОЦЕССОР | 1992 |

|

RU2032215C1 |

| Однородная вычислительная система | 1984 |

|

SU1275458A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| ПРОЦЕССОР | 1990 |

|

SU1826787A1 |

| Многопроцессорная вычислительная система | 1979 |

|

SU751238A1 |

| Микропрограммный процессор | 1978 |

|

SU741269A1 |

| Устройство для обработки изображений | 1991 |

|

SU1836693A3 |

| Вычислительный модуль и способ обработки с использованием такого модуля | 2018 |

|

RU2689433C1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке специализированных и универсальных вычислительных устройств, предназначенных для обработки цифровой информации. Целью . изобретения является повьшение быстродействия устройства. Поставленная цель достигается тем, что устройство содержит арифметико-логический блок 1, блок 2 умножения, блок 3 деления, двунаправленный коммутатор 4, первый и второй блоки 5 и 6 памяти данных, блок 7 регистров, первьй и второй регистры 8 и 9, первый и второй индексные арифметические блоки 10 и 11, первый и второй регистры 12 и 13 адреса, блок 14 памяти команд, элемент ИЛИ 15, первый коммутатор 16, блок 17 микропрограммного управления, второй коммутатор 18. Увеличение быстродействия обеспечивается за счет сокращения числа последовательных обращений к памяти. 2 ил. (Л -огг

д /гг1

:1| .,Ъ, и 5, 5г S, б. /Ти S- ff, ir, 12,D,№..Щ

„И,.1-1111-11 JxLLU..iiJLl 1 .

-Записи

4

f7s

Составитель Е Смирнов Редактор И.Касарда Техред Л, Сердюкова

Заказ 4922/48 Тираж 670Подписное

ВНКИПИ Государственног о комигета CUCP

по делам изсбретекргй и открытий 113035, Москва, W.-35, Раушская наб,, ц... 4/5

Производственно-полиграфическое П1 едпр1-;ятие,

;рни

У жг с р од 5 ул, S Пр о е к т н а я , 4

| Центральный процессор | 1972 |

|

SU438015A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Центральный процессор | 1975 |

|

SU608160A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-15—Публикация

1985-05-05—Подача