Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств вычислительных машин с пла вающей 3апятой.

Целью изобретения является iioHbiutc ние быстродействия устройства для суммирования чисел с гшава101цей пятой.

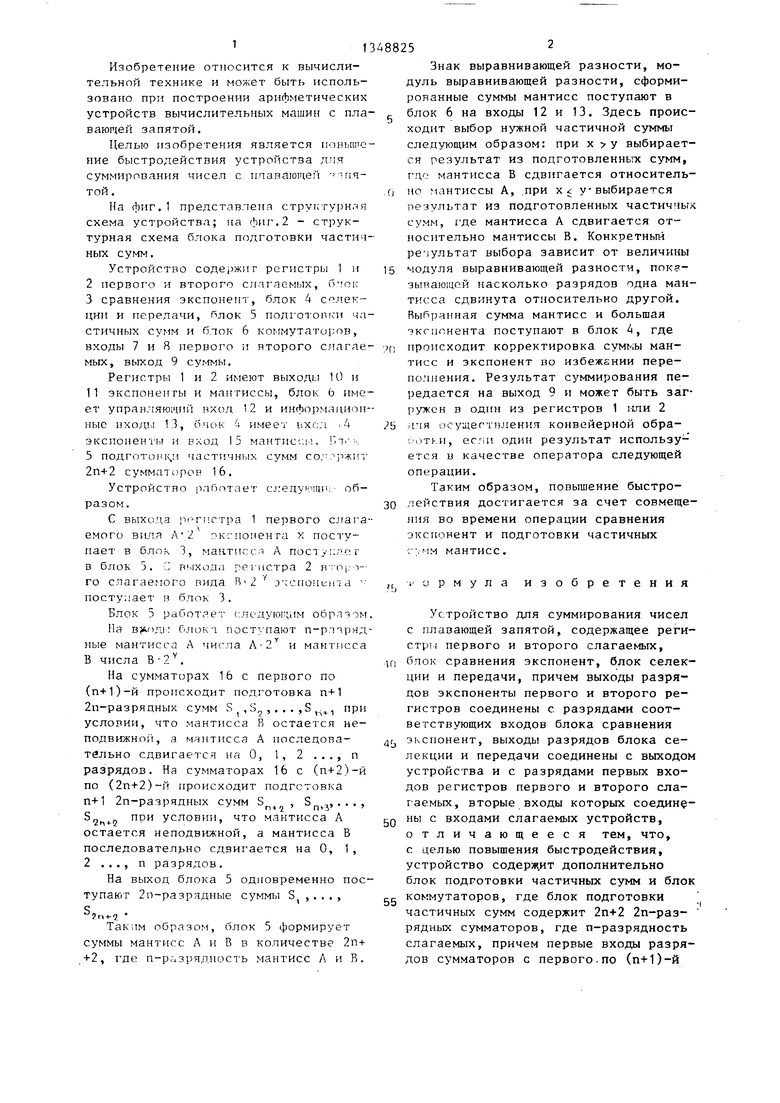

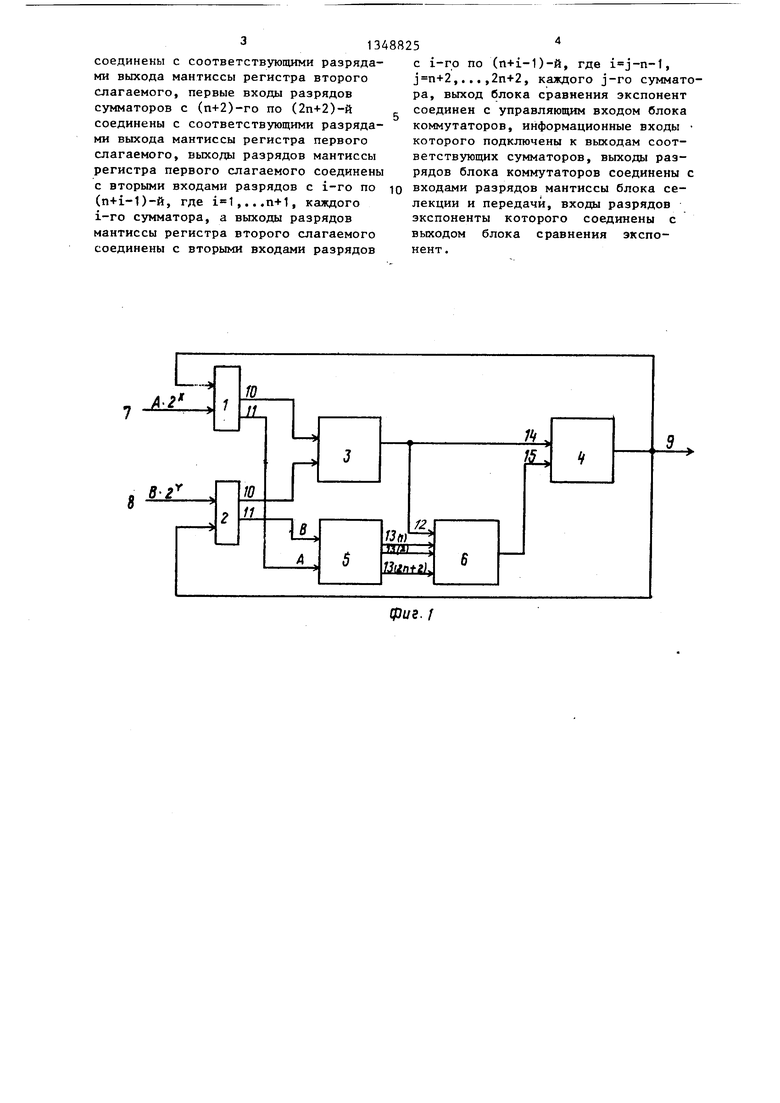

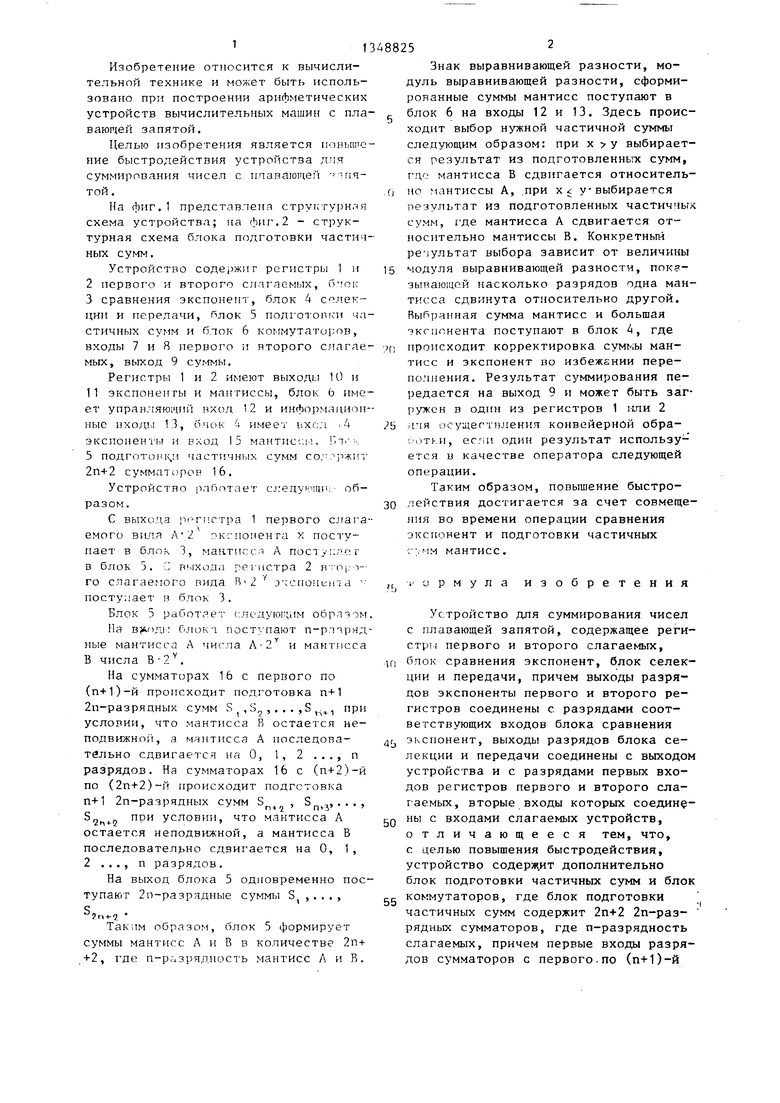

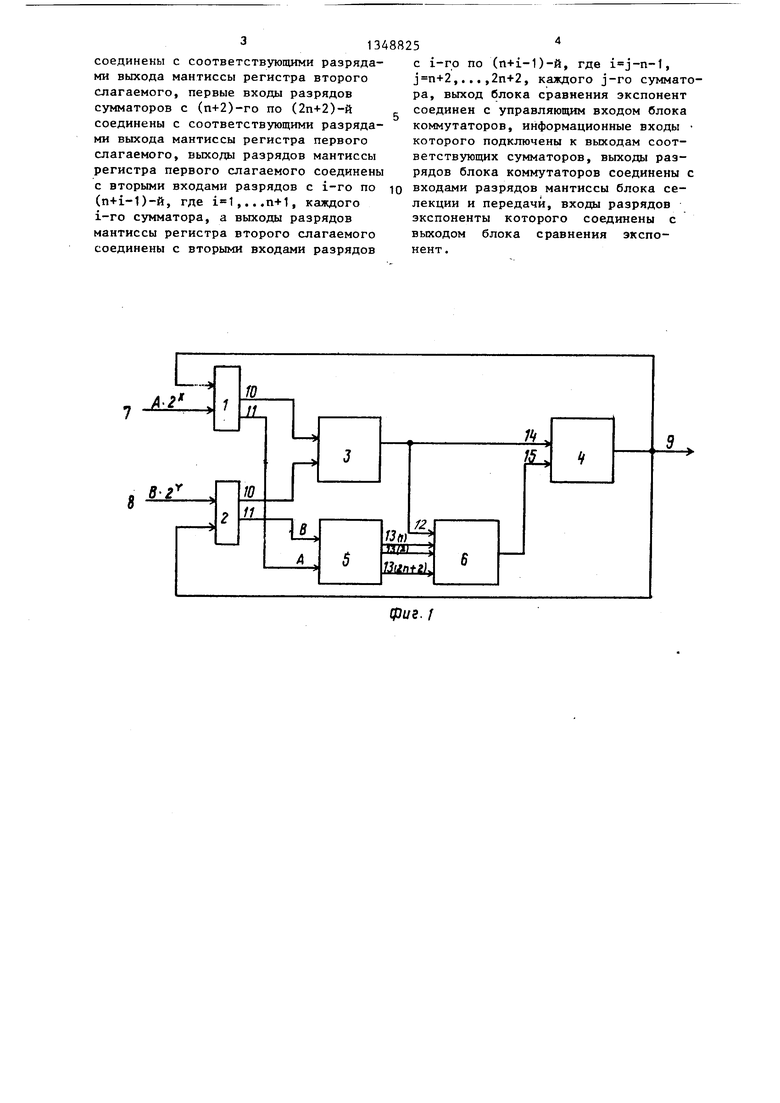

На фиг.1 представлена структурн.чя схема устройства; на (Ьиг.2 - структурная схема блока подготовки частич ных сумм.

Устройство содержит регистры 1 и

2иервого и второго слагаемых, б-гок

3сравнения экспонент, блок 4 сплек- ции и передачи, блок 5 подготопки частичных сумм и блок 6 кo гмyтa гupoв, входы 7 и 8 первого и второго слагав мых, выход 9 суммы.

Регистры 1 и 2 имеют выходы 10 и 11 экспоненты и мантиссы, блок b имеет управ:1ЯЮ1ций вход 12 и информационные входы 13, блок 4 имеет кхсл 4 экспонент, и вход 15 мантис;:.. Г)7 -|-. 5 подгото ч и частичн)1х сумм co/ iv/Ki;T 2п+2 сумматоров 16.

Устройство работает следу1(1гщч образом.

С выхода Магистра 1 первого cjrara емого вида А 2 эксчюиенга х поступает в блок 3, мантисся А пос1у:;ает в блок 5. С выхода регистра 2 rr; oi;o-- го слагаемого вида э сспоиен ; а поступает в блок 3.

Блок 5 работает с:лодую1цим образом

На .: блока поступают п-р.прядные мантисса А числа А 2 и мантясса В числа В 2.

На сумматорах 16 с первого по ()-й происходит подготовка n+l 2п-разрядных сумм S , S , . . . ,S , при условии, что мантисса F5 остается не- подвижноЕ, а мантисса А последовательно сдвигается на О, 1, 2 ..., п разрядов. На сумматорах 16 с (п+2)-й по (2п+2)-й происходит подготовка п+1 2п-разрядных сумм S , S ,..., 2h4-2 Р условии, что мантисса А остается неподвижной, а мантисса В последовател 5но сдвигается на О, 1 , 2 . . ., п разрядов.

На выход блока 5 одновременно поступают 2п-разрядные cyNrMiii S ,. . . ,

n-H5

Таким образом, блок 5 формирует суммы мантисс А и В в количестве 2п+ +2, где п-разрядность мантисс А и В.

А88252

Знак выравнивающей разности, модуль выравнивающей разности, сформированные суммы мантисс поступают в

блок 6 на входы 12 и 13. Здесь происходит выбор нужной частичной суммы следующим образом: при х у выбирается результат из подготовленных сумм, гдс мантисса В сдвигается относитель- fj но мантиссы А, .при х у-выбирается результат из подготовленных частичных сумм, где мантисса А сдвигается относительно мантиссы В. Конкретньм ре )ультат выбора зависит от величины 15 модуля выравнивающей разности, показывающей насколько разрядов одна мантисса сдвинута относительно другой. Выбранная сумма мантисс и большая экспонента поступают в блок 4, где

7f; происходит корректировка суммы мантисс и экспонент во избежании пере- по-чнения. Результат суммирования передается на выход 9 и может быть загружен в один из регистров 1 i-ши 2

2й цпя осущег г}зления конвейерной обра- ;и:1тки, ес.чи один результат используется в качестве оператора следующей операции.

Таким образом, повышение быстро30 действия достигается за счет совмещения во времени операции сравнения экспонент и подготовки частичных ; ;, -(м мантисс.

рч ормула изобретения

Устройство для суммирования чисел с плавающей запятой, содержащее регистры первого и второго слагаемых,

If блок сравнения экспонент, блок селекции и передачи, причем выходы разрядов экспоненты первого и второго регистров соединены с разрядами соответствующих входов блока сравнения

4, экспонент, выходы разрядов блока селекции и передачи соединены с выходом устройства и с разрядами первых входов регистров первого и второго слагаемых, вторые входы которых соедин gQ ны с входами слагаемых устройств, отличающееся тем, что, с целью повышения быстродействия, устройство содержит дополнительно блок подготовки частичных сумм и блок

gg коммутаторов, где блок подготовки

частичных сумм содержит 2п+2 2п-раз- рядных сумматоров, где п-разрядность слагаемых, причем первые входы разрядов сумматоров с первого.по (п+1)-и

соединены с соответствующими разрядами выхода мантиссы регистра второго слагаемого, первые входы разрядов сумматоров с (п+2)-го по (2п+2)-й соединены с соответствующими разрядами выхода мантиссы регистра первого слагаемого, выходы разрядов мантиссы регистра первого слагаемого соединены с вторыми входами разрядов с i-ro по (п+1-1)-й, где ,...п+1, каждого i-ro сумматора, а выходы разрядов мантиссы регистра второго слагаемого соединены с вторыми входами разрядов

с i-ro по (n+i-1)-ft, где i j-n-1, ,...,2п+2, каждого j-ro сумматора, выход блока сравнения экспонент соединен с управляющим входом блока коммутаторов, информационные входы которого подключены к выходам соответствующих сумматоров, выходы разрядов блока коммутаторов соединены с входами разрядов мантиссы блока селекции и передачи, входы разрядов экспоненты которого соединеиы с выходом блока сравнения экспонент.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования чисел в дополнителььном коде с плавающей запятой | 1991 |

|

SU1833864A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для суммирования-вычитания чисел с плавающей запятой | 1989 |

|

SU1667056A1 |

| Устройство для суммирования массива чисел | 1989 |

|

SU1647556A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для суммирования двух чисел с плавающей запятой | 1985 |

|

SU1290300A1 |

| Устройство для умножения | 1984 |

|

SU1226447A1 |

| Устройство для вычисления гиперболических функций у = @ и у = с @ | 1990 |

|

SU1735845A1 |

| Устройство для сложения последовательности чисел с плавающей запятой | 1984 |

|

SU1182512A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

Изобретение относится к вычислительной технике и предназначено для суммирования чисел с плавающей запятой. Целью изобретения является повышение быстродействия. Цель достигается за счет введения в состав устройства блока подготовки частичных сумм и блока коммутаторов. Это позволяет совместить во времени процессы сравнения экспонент и подготовки частичных сумм, представляющих собой суммы первого числа со сдвинутым на различное число разрядов вторым числом и второго числа со сдвинутым первым. Блок коммутаторов выбирает в зависимости от знака и модуля разности значений соотвутствующую частичную сумму. 2 ил. i (Л со 4 00 00 го ел

tpus.f

| Соловьев Г.Н | |||

| Арифметические устройства ЭВМ | |||

| М.: Энергия, 1978, с | |||

| Прялка для изготовления крученой нити | 1920 |

|

SU112A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Самофалов К.Г., Луцкий Г.М | |||

| Структура и функционирование ЭВМ и систем | |||

| Киев: Вища школа, 1978, с | |||

| Приспособление для записи звуковых явлений на светочувствительной поверхности | 1919 |

|

SU101A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-10-30—Публикация

1986-01-08—Подача