Изобретение относится к области вычислительной техники и может быть использовано при построении арифметических устройств вычислительных машин с плавающей запятой.

Цель изобретения - повышение быстродействия и расширение области применения.

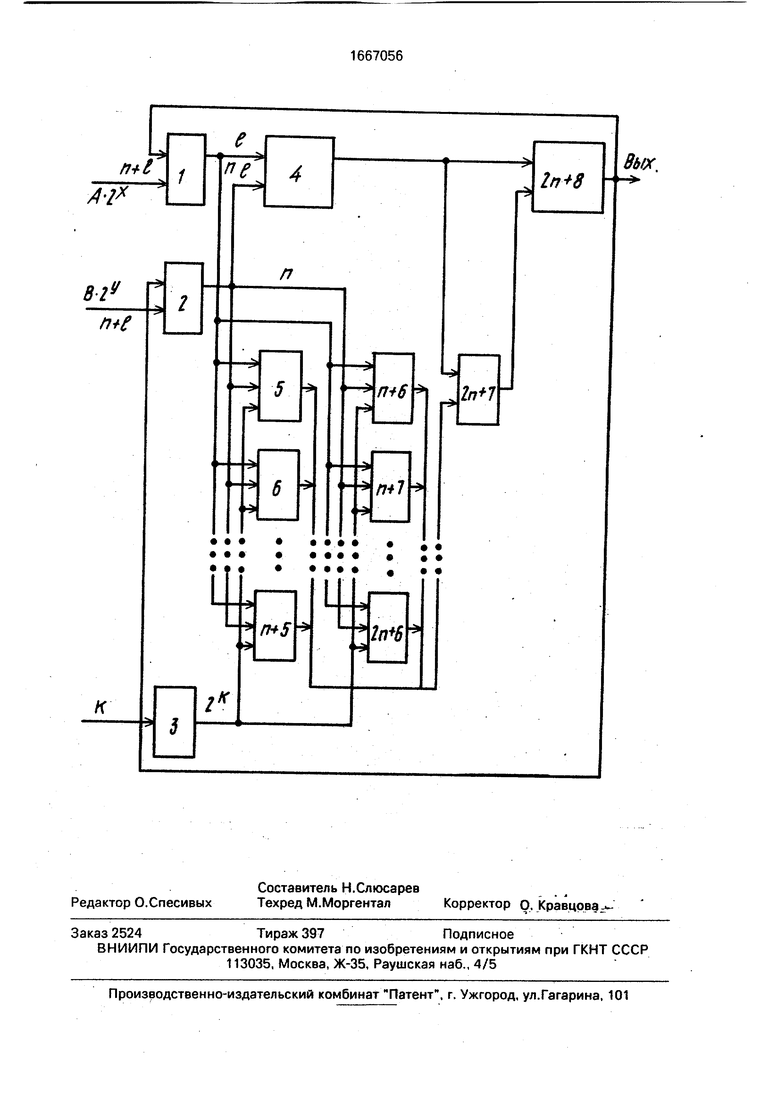

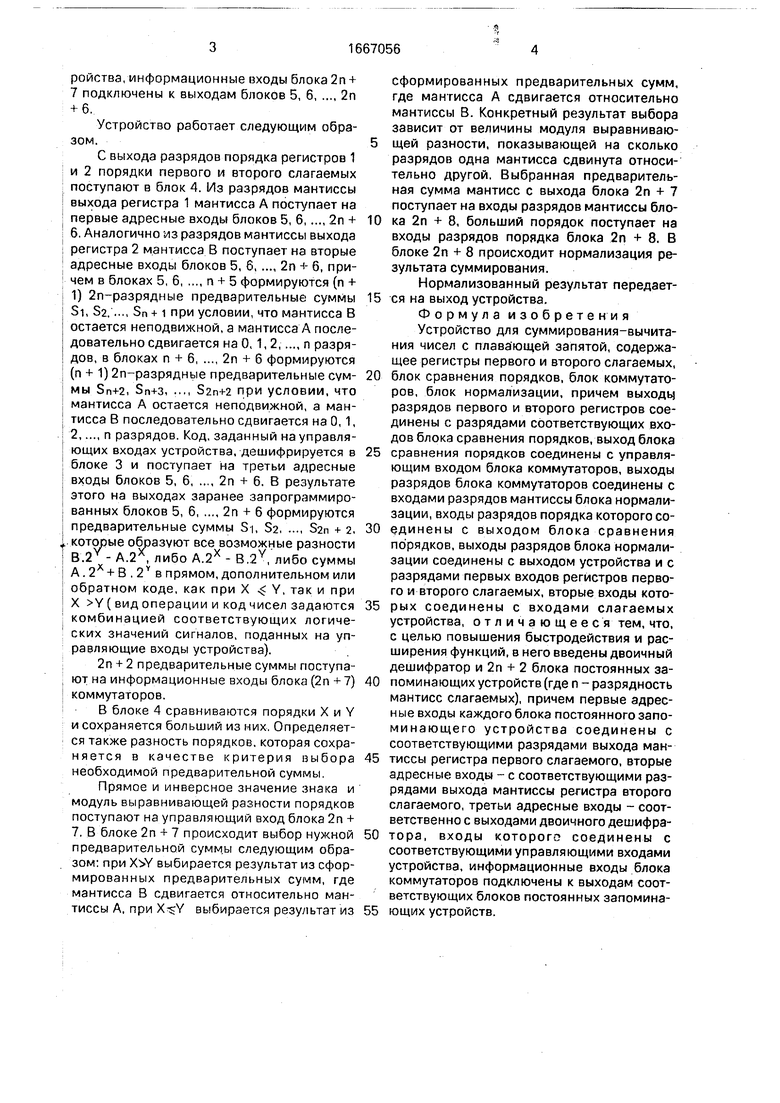

На чертеже изображена структурная схема предложенного устройства.

Устройство для суммирования/вычитания чисел с плавающей запятой содержит регистры 1 и 2 первых и вторых слагаемых соответственно, двоичный дешифратор 3, блок 4 сравнения порядков, (2п + 2), где п - разрядность мантисс операндов, блоков постоянных запоминающих устройств с номерами 5, 62п + 6, блок коммутаторов 2п +

7. блок нормализации 2п + 8.

Выходы разрядов порядков регистров 1 и 2 соединены с разрядами соответствующих входов блока 4, выход блока 4 соединен с управляющим входом блока 2п + 7, выходы разрядов блока 2п + 7 соединены с входами разрядов мантиссы блока 2п + 8, а его входы разрядов порядка соединены с выходом блока 4, выходы разрядов блока 2п + 8 соединены с выходом устройства и с разрядами первых входов регистров 1 и 2, вторые входы которых соединены со входами слагаемых устройства, первые адресные входы блоков 5, 62п + 6 соединены с соответствующими разрядами выхода мантиссы регистра 1. вторые адресные входы блоков 5,

62п + 6 соединены с соответствующими

разрядами выхода мантиссы регистра 2,

третьи адресные входы блоков 5. 62п +

6 соединены с соответствующими выходами блока 3, входы которого соединены с соответствующими управляющими входами уст

Ё

О

о VI о ел

Оч

ойства, информационные входы блока 2п + подключены к выходам блоков 5, 6, .... 2п 6.

Устройство работает следующим обраом.

С выхода разрядов порядка регистров 1 и 2 порядки первого и второго слагаемых поступают в блок 4. Из разрядов мантиссы выхода регистра 1 мантисса А поступает на

первые адресные входы блоков 5, 62п +

6. Аналогично из разрядов мантиссы выхода регистра 2 мантисса В поступает на вторые адресные входы блоков 5, 62п + 6, причем в блоках 5, 6п + 5 формируются (п +

1) 2п-разрядные предварительные суммы Si, 82..... Sn + 1 при условии, что мантисса В остается неподвижной, а мантисса А последовательно сдвигается на 0, 1, 2п разрядов, в блоках п + 62п + 6 формируются

(п + 1) 2п-разрядные предварительные суммы Sn+2, Sn+3S2n+2 При УСЛОВИИ, ЧТО

мантисса А остается неподвижной, а мантисса В последовательно сдвигается на 0, 1, 2п разрядов. Код, заданный на управляющих входах устройства, дешифрируется в блоке 3 и поступает на третьи адресные

входы блоков 5, 6 2п + 6. В результате

этого на выходах заранее запрограммированных блоков 5, 62п + 6 формируются

предварительные суммы Si, 82 S2n + 2.

которые образуют все возможные разности В.2 - А.2 , либо А.2х - В.2У, либо суммы А. 2х + В . 2Y в прямом, дополнительном или обратном коде, как при X Y, так и при X Y ( вид операции и код чисел задаются комбинацией соответствующих логических значений сигналов, поданных на управляющие входы устройства).

2п + 2 предварительные суммы поступают на информационные входы блока (2п + 7) коммутаторов.

В блоке 4 сравниваются порядки X и Y и сохраняется больший из них. Определяется также разность порядков, которая сохра- няется в качестве критерия выбора необходимой предварительной суммы.

Прямое и инверсное значение знака и модуль выравнивающей разности порядков поступают на управляющий вход блока 2п + 7. В блоке 2п + 7 происходит выбор нужной предварительной суммы следующим образом: при выбирается результат из сформированных предварительных сумм, где мантисса В сдвигается относительно мантиссы А, при выбирается результат из

сформированных предварительных сумм, где мантисса А сдвигается относительно мантиссы В. Конкретный результат выбора зависит от величины модуля выравнивающей разности, показывающей на сколько разрядов одна мантисса сдвинута относительно другой. Выбранная предварительная сумма мантисс с выхода блока 2п + 7 поступает на входы разрядов мантиссы блока 2п + В, больший порядок поступает на входы разрядов порядка блока 2п + 8. В блоке 2п + 8 происходит нормализация результата суммирования.

Нормализованный результат передается на выход устройства.

Формула изобретения Устройство для суммирования-вычитания чисел с плавающей запятой, содержащее регистры первого и второго слагаемых,

блок сравнения порядков, блок коммутаторов, блок нормализации, причем выходц разрядов первого и второго регистров соединены с разрядами соответствующих входов блока сравнения порядков, выход блока

сравнения порядков соединены с управляющим входом блока коммутаторов, выходы разрядов блока коммутаторов соединены с входами разрядов мантиссы блока нормализации, входы разрядов порядка которого соединены с выходом блока сравнения порядков, выходы разрядов блока нормализации соединены с выходом устройства и с разрядами первых входов регистров первого и второго слагаемых, вторые входы которых соединены с входами слагаемых устройства, отличающееся тем, что, с целью повышения быстродействия и расширения функций, в него введены двоичный дешифратор и 2п + 2 блока постоянных запоминающих устройств (где п - разрядность мантисс слагаемых), причем первые адресные входы каждого блока постоянного запо- минающего устройства соединены с соответствующими разрядами выхода мантиссы регистра первого слагаемого, вторые адресные входы - с соответствующими разрядами выхода мантиссы регистра второго слагаемого, третьи адресные входы - соответственно с выходами двоичного дешифратора, входы которого соединены с соответствующими управляющими входами устройства, информационные входы блока коммутаторов подключены к выходам соответствующих блоков постоянных запоминающих устройств.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для деления чисел | 1981 |

|

SU1012241A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для суммирования чисел в дополнителььном коде с плавающей запятой | 1991 |

|

SU1833864A1 |

| Устройство для суммирования чисел с плавающей запятой | 1986 |

|

SU1348825A1 |

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах машин с плавающей точкой. Целью изобретения является повышение быстродействия и расширение функций устройства. С этой целью в устройство, содержащее регистры первого и второго слагаемых, блок сравнения порядков, блок коммутаторов, блок нормализации, введены двоичный дешифратор и 2N + 2 блоков постоянных запоминающих устройств (N - разрядность мантисс слагаемых). 1 ил.

| Малиновский Б.Н | |||

| Справочник по цифровой вычислительной технике | |||

| Киев: Техника, 1974, с | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Самофалов К.Г., Луцкий Г.М | |||

| Структура и организация функционирования ЭВМ и систем | |||

| Киев: Вища школа, 1978, с | |||

| Облицовка комнатных печей | 1918 |

|

SU100A1 |

| Устройство для суммирования чисел с плавающей запятой | 1986 |

|

SU1348825A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-30—Публикация

1989-07-14—Подача