1

Изобретение относится к технике передачи цифровой информации и может быть использовано для тактовой синхронизации приемных схем.

Целью изобретения является уменьшение времени вхождения в синхронизм.

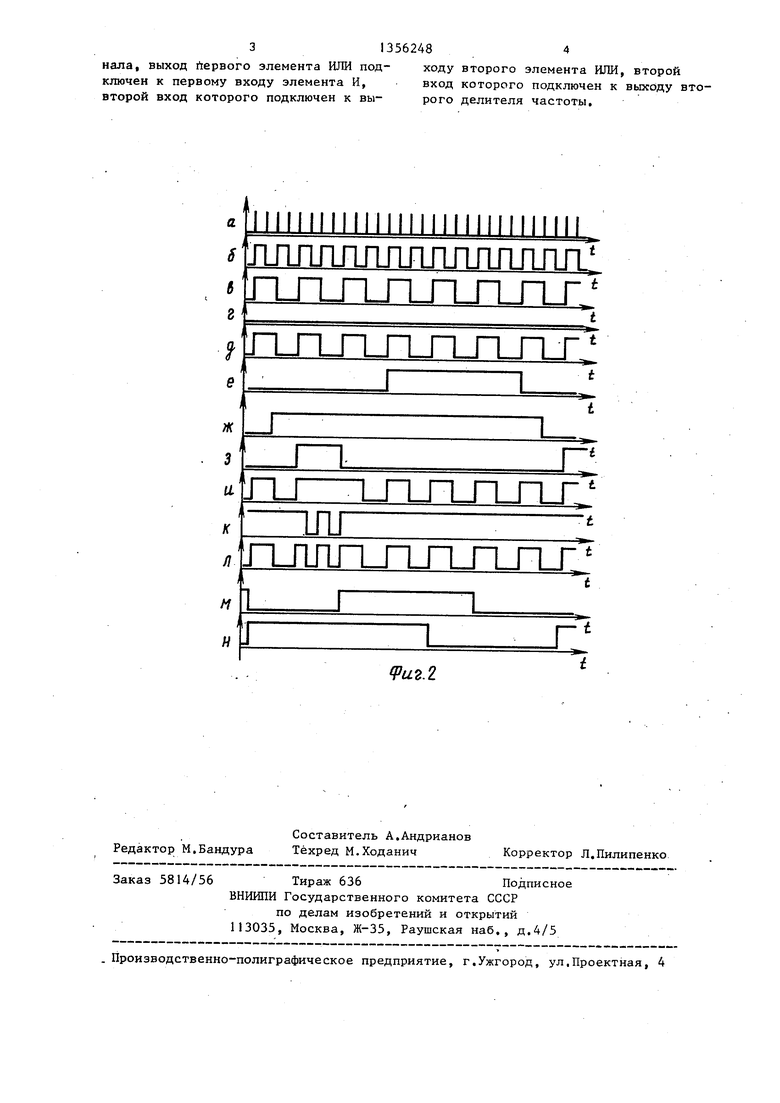

На фиг.1 представлена функциональная схема устройства тактовой синхронизации; на фиг. 2 - временные диаграммы работы устройства.

Устройство тактовой синхронизации содержит задающий генератор 1, первый, второй и третий делители 2,3, и 4 частоты, блок 5 выделения значащих моментов входного сигнала, первый и второй элементы ИЛИ 6 и 7,элемент И 8, причем блок 5 выделения значащих моментов входного сигнала содержит регистр 9 сдвига и полусумматор 10.

Устройство работает следующим образом.

Задающий генератор 1 вырабатывает импульсы произвольной скважности (фиг.2а), которые поступают на вход первого делителя 2 частоты с частотой F. Первый делитель 2 частоты обеспечивает деление исходной частоты до величины F/2 (фиг,2б), а третий делитель частоты - до величины F/4 (фиг.2в).

Информация, поступающая из канала связи (фиг.2ж) на вход регистра 9 сдвига блока 5 выделения, записывается импульсами с частотой F/4 и поступает на вход полусумматора 10. При этом начало и конец информационного

13562482

импульсы (фиг,2з),которые, поступая на вход первого элемента ИЛИ 6, не разрешают прохождение в эти моменты импульсов с выхода третьего делителя 4 частоты (фиг.2и).

Работа второго элемента ИЛИ 7 определяется обратной связью элемента ИЛИ 7. Сигнал в цепи обратной связи

Q определяет направление си-нхрониза- ции.

в случае, если входная информация опережает по фазе тактовую последовательность, то во время действия

15 сигнала с выхода полусумматора 10 на выходе второго элемента ИЛИ 7 формируются два импульса (фиг.2к).При этом выходной сигнал элемента И 8 содержит на один импульс больше, чем

2д сигнал частоты F/4 (фиг,2к), что определяет изменение фазы тактовой последовательности (фиг.2м),

В случае, если входная информация отстает по фазе от тактовой последо25 вательности., то во время действия сигнала с выхода полусумматора 10 на вход второго делителя частоты 3 поступает на один импульс меньше (фиг, 2л), что определяет изменение фазы

30 тактовой последовательности (фиг.

35

2н

Формула изобретения

Устройство тактовой синхронизации, содержащее соединенные последовательно задающий генератор и первый делитель частоты, элемент И и второй делитель частоты, выход которого являУстройство тактовой синхрониз содержащее соединенные последова но задающий генератор и первый д тель частоты, элемент И и второй литель частоты, выход которого я

импульса фиксируются на выходе .полусумматора 10 импульсами длительностью до тся выходом устройства, а также Т 4/F (фиг.2з).блок выделения значащих моментов

При отсутствии входного сигнала

входного сигнала, вход которого ляется входом устройства, отл чающееся тем, что, с цел уменьшения времени вхождения в си ронизм, введены первый и второй менты ИЛИ и третий делитель част при этом вход третьего делителя ч тоты объединен с первым входом в го элемента ИЛИ и подключен к вы ду первого делителя частоты, вых третьего делителя частоты подключ к второму входу блока выделения чащих моментов входного сигнала первому входу первого элемента ИЛ второй вход которого объединен с инверсным входом второго элемента ИЛИ и подключен к- выходу блока вы ления значащих моментов входного

на выходе полусумматора устанавливается состояние логического О (фиг,2г), что обеспечивает формирова- ние сигнала, соответствующего логической 1 на выходе второго элемента ИЛИ 7, и разрешает прохождение импульсов.с выхода третьего делителя 4 частоты (фиг.2в) через элементы И 8, Второй делитель 3 частоты при этом формирует выходные тактовые импульсы путем деления импульсов частоты F/4 (фиг,2д) на п, которые выдает на выходе устройства (фиг,2е, для случая ),

При появлении на входе устройства информационного сигнала (фиг,2ж) на выходе полусумматора 10 формируются

Формула изобретения

Устройство тактовой синхронизации, содержащее соединенные последовательно задающий генератор и первый делитель частоты, элемент И и второй делитель частоты, выход которого явля тся выходом устройства, а также блок выделения значащих моментов

0

5

5

входного сигнала, вход которого является входом устройства, отличающееся тем, что, с целью уменьшения времени вхождения в синхронизм, введены первый и второй элементы ИЛИ и третий делитель частоты, при этом вход третьего делителя частоты объединен с первым входом второ-- го элемента ИЛИ и подключен к выходу первого делителя частоты, выход третьего делителя частоты подключен к второму входу блока выделения значащих моментов входного сигнала и первому входу первого элемента ИЛИ, второй вход которого объединен с инверсным входом второго элемента ИЛИ и подключен к- выходу блока выделения значащих моментов входного сиг313562484

нала, выход rtepsoro элемента ИЛИ под- ходу второго элемента ИЛИ, второй ключей к первому входу элемента И, вход которого подключен к выходу вто- второй вход которого подключен к вы- рого делителя частоты.

Редактор М.Бандура

Составитель А.Андрианов Техред М.Ходанич

Заказ 5814/56 Тираж 636Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

аг.г

Корректор Л.Пилипенко

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1985 |

|

SU1370792A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1338096A1 |

| Устройство синхронизации | 1986 |

|

SU1483660A1 |

| Устройство фазовой синхронизации | 1985 |

|

SU1256226A1 |

| Устройство для демодуляции частотно-манипулированных сигналов | 1987 |

|

SU1450127A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1254589A1 |

| Устройство дискретной автоподстройки фазы тактовых импульсов | 1986 |

|

SU1389005A2 |

| Устройство синхронизации | 1990 |

|

SU1781835A1 |

| Устройство тактовой синхронизации | 1986 |

|

SU1411990A1 |

| Резервированный делитель частоты | 1989 |

|

SU1691954A1 |

Изобретение относится к технике передачи цифровой информации и уменьшает время вхождения в синхронизм. Устр-во содержит задающий г-р I, делители частоты (ДЧ) 2-4, блок 5 вьщеления значащих моментов входного сигнала, эл-ты ИЛИ 6 и 7, эл-т И 8. Блок 5 содержит регистр 9 сдвига, полусумматор 10. При отсутствии входного сигнала на выходе полусумматора устанавливается состояние ло- гич.О, что обеспечивает формирование сигнала, соответствующего ло- гич.1 на выходе эл-та ИЛИ 7, и разрешает прохождение импульса с выхода ДЧ 4 через эл-т И 8. При появлении информац. сигнала на Ьыходе полусумматора 10 формируются импульсы, к-рые, поступая на вход эл-та РШИ 6, не разрешают прохождение, в эти моменты импульсов с ДЧ 4. 2 ил. СО САЭ СП о: го 4 00

| Устройство для синхронизации двоичных сигналов | 1976 |

|

SU636813A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство тактовой синхронизации | 1977 |

|

SU661833A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-11-30—Публикация

1984-08-31—Подача