1136

Изобретение относится к вычислительной технике, предназначено для построения постоянных запоминающих устройств с низкой потребляемой мощ- ностыо и большим быстродействием и является усовершенствованием изобретения по авт.св. № 746730,

Цель изобретения - повышение быстродействия устройства.

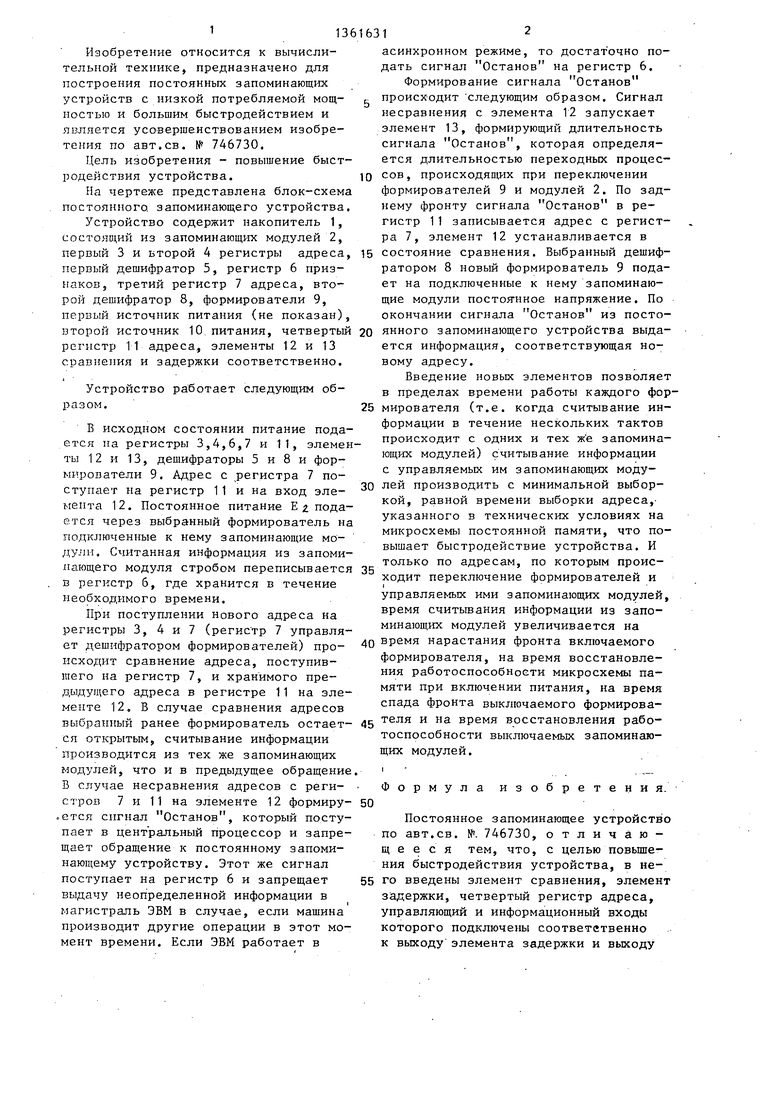

На чертеже представлена блок-схема постоян1юго. запоминающего устройства.

Устройство содержит накопитель 1, состояпАИй из запоминающих модулей 2, первый 3 и второй 4 регистры адреса, первый дешифратор 5, регистр 6 признаков, третий регистр 7 адреса, второй дешифратор 8, формирователи 9, первый источник питания (не показан), второй источник 10 питания, четвертый регистр 11 адреса, элементы 12 и 13 сравнения и задержки соответственно.

Устройство работает следующим образом.

Б исходном состоянии питание подается па регистры 3,4,6,7 и 11, элементы 12 и 13, дешифраторы 5 и 8 и формирователи 9. Адрес с регистра 7 поступает на регистр 11 и на вход эле- мента 12. Постоянное питание Е подается через выбранный формирователь на подключенные к нему запоминающие мо- ду. ли Считанная информация из запоминающего модуля стробом переписывается в регистр б, где хранится в течение необходимого времени.

При поступлении нового адреса на регистры 3, 4 и 7 (регистр 7 управляет дешифратором формирователей) про- исходит сравнение адреса, поступившего на регистр 7, и хранимого предыдущего адреса в регистре 11 на элементе 12, В случае сравнения адресов выбранный ранее формирователь остает- ся открытым, считывание информации производится из тех же запоминающих модулей, что и в предыдущее обращение В случае несравнения адресов с реги- стров 7 и 11 на элементе 12 формиру- ется сигнал Останов, который поступает в центральный процессор и запрещает обращение к постоянному запоминающему устройству. Этот же сигнал поступает на регистр 6 и запрещает выдачу неопределенной информации в магистраль ЭВМ в случае, если машина производит другие операции в этот момент времени. Если ЭВМ работает в

1

асинхронном режиме, то достат очно подать сигнал Останов на регистр 6.

Формирование сигнала Останов происходит следующим образом. Сигнал несравнения с элемента 12 запускает элемент 13, формирующий длительность сигнала Останов, которая определяется длительностью переходных процессов, происходящих при переключении формирователей 9 и модулей 2. По заднему фронту сигнала Останов в регистр 11 записывается адрес с регистра 7, элемент 12 устанавливается в состояние сравнения. Выбранный дешифратором 8 новый формирователь 9 подает на подключенные к нему запоминающие модули постоянное напряжение. По окончании сигнала Останов из постоянного запоминающего устройства выдается информация, соответствующая новому адресу.

Введение новых элементов позволяет в пределах времени работы каждого формирователя (т,е. когда считывание информации в течение нескольких тактов происходит с одних и тех ж е запоминающих модулей) считывание информации с управляемых им запоминающих модулей производить с минимальной выборкой, равной времени выборки адреса,- указанного в технических условиях на микросхемы постоянной памяти, что повышает быстродействие устройства. И только по адресам, по которым происходит переключение формирователей и управляемых ими запоминающих модулей, время считьтания информации из запоминающих модулей увеличивается на время нарастания фронта включаемого формирователя, на время восстановления работоспособности микросхемы памяти при включении питания, на время спада фронта выключаемого формирователя и на время восстановления работоспособности выключаемых запоминающих модулей. I

Формула изобретения.

Постоянное запоминающее устройство по авт.св. №. 746730, отличающееся тем, что, с целью повьше- ния быстродействия устройства, в него введены элемент сравнения, элемент задержки, четвертый регистр адреса, управляющий и информационный входы которого подключены соответственно к выходу элемента задержки и выходу

31361631

третьего регистра адреса, соединен- ключей к входу элемента задержки, ного с первым входом элемента срав- второму информационному входу реги- нения, второй вход которого подклю- стра признаков и является вторым ин- чен к выходу четвертого регистра ад- формационным вькодом постоянного за- реса, выход элемента сравнения под- поминающего устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU746730A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Постоянное запоминающее устройство | 1981 |

|

SU1014037A1 |

| Постоянное запоминающее устройство | 1989 |

|

SU1645999A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СМЕННЫМИ МОДУЛЯМИ | 2014 |

|

RU2571412C1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1280455A1 |

| Устройство для контроля микросхем постоянной памяти | 1987 |

|

SU1478258A1 |

| Динамическое оперативное запоминающее устройство | 1981 |

|

SU1003142A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

Изобретение относится к вычислительной технике и предназначено для построения постоянных запоминающих устройств. Цель изобретения - повышение быстродействия постоянного запоминающего устройства. Поставленная, цель осуществляе тся за счет считывания информации с управляемых формирователем запоминающих модулей с минимальной выборкой адреса, что повышает быстродействие уст- ройства И только по адресам, по которым происходит переключение формирователей и управляемых ими запоминающих модулей, время считывания информации из запоминающих модулей увеличивается на время нарастания фронта включаемого формирователя, на время восстановления работоспособности микросхемы памяти при включении питания, на время спада фронта выключаемого формирователя и время восстановления работоспособности выключаемых запоминающих устройств. Устройство содержит накопитель 1, запоминающие модули 2, регистры 3,4,7,11 адреса, дешифраторы 5,8, регистр 6 признаков,формирователи 9, источник 10 питания, элементы 12 и 13 сравнения и задержки. 1 ил. (О Останов ли ZfO CD OS со го

| Постоянное запоминающее устройство | 1977 |

|

SU746730A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-12-23—Публикация

1986-07-15—Подача