Ifi ЭЬ Л

U9

сутствии сигналов записи на входе 41 сигналом с пятого выхода формирователя 2 устройство переводится в режим готовности к чтению, о чем сигнализирует сигнал на выходе 42 и нулевое состояние выхода триггера 16. Сигнал

чтения подается по входу 45. Нулевое состояние выхода 43 триггера 17 соответствует переполнению накопителя 13. Информация записывается по входам 47 и считывается на выходную шину 46. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство ввода-вывода информации | 1988 |

|

SU1619283A1 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| Формирователь страниц для голографического запоминающего устройства | 1986 |

|

SU1388948A1 |

| Логическое запоминающее устройство | 1981 |

|

SU1014036A1 |

| Устройство для ввода информации | 1987 |

|

SU1432544A1 |

| Логическое запоминающее устройство | 1983 |

|

SU1140172A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Мультипрограммное вычислительное устройство | 1990 |

|

SU1777147A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и предназначено для сопряжения периферийных устройств с ЭВМ, имеющими параллельный интерфейс. Целью изобретения является расширение области применения устройства за счет обеспечения асинхронных режимов записи и чтения данных. Устройство содержит генератор 1 импульсов, первый 2 и второй 3 формирователи управляющих сигналов, с первого по пятый триггеры 4, 5, 6, 16.и 17, элемент ИЛИ 7, счетчик 8 адреса записи, три элемента И 9-11, коммутатор 12, накопитель 13, блок 14 сравиения, счетчик 18 адреса чтения, элементы И-НЕ 15, 19, шинные формирователи 20, 21 и элементы НЕ 22, 23 и 24. Асинхронная работа буферного запоминающего устройства в режимах записи и чтения обеспечивается применением формирователей 2 и 3, формирующих соответственно сигнгшы управления записью и чтением. При поступлении сигналов записи по входу 41 вход 44 опроса готовности к чтению устройства блокируется триггерами 5 и 4. При отi (Л

1

Изобретение относится к вычислительной технике, в частности к запо- минающим устройствам, и предназначен для сопряжения периферийных устройст

с ЭВМ, имеющими параллельный интерфейс .

Целью изобретения является расширение области применения устройства за счет обеспечения асинхронных режи MOB записи и чтения данных.

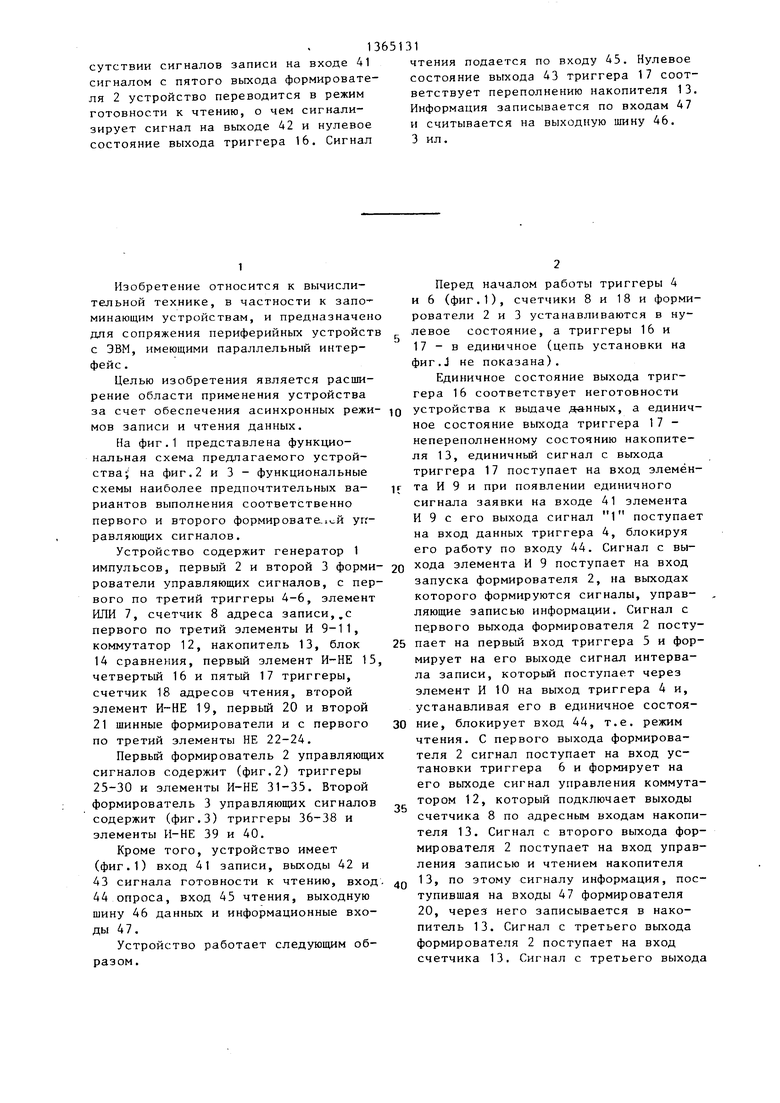

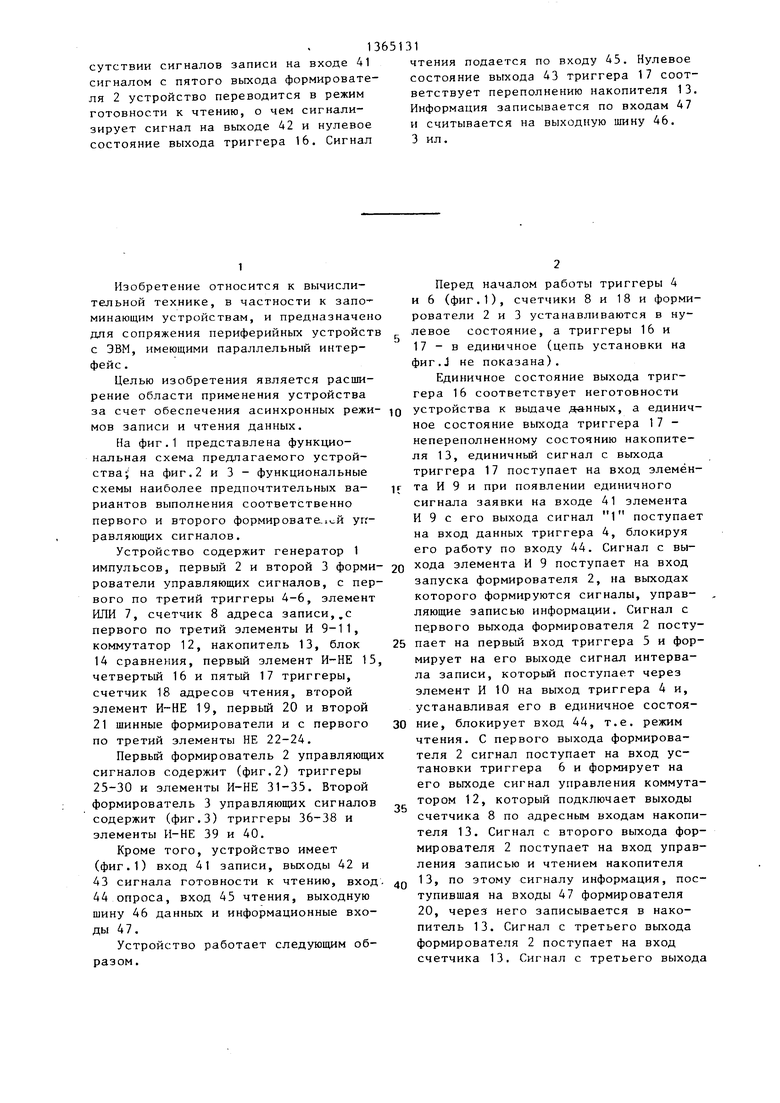

На фиг.1 представлена функциональная схема предлагаемого устройства J на фиг.2 и 3 - функциональные схемы наиболее предпочтительных ва- риантов выполнения соответственно первого и второго формировате.1.-й управляющих сигналов.

Устройство содержит генератор 1 импульсов, первый 2 и второй 3 форми рователи управляющих сигналов, с первого по третий триггеры 4-6, элемент ИЛИ 7, счетчик 8 адреса записи,,с первого по третий элементы И 9-11, коммутатор 12, накопитель 13, блок 14 сравнения, первый элемент И-НЕ 15 четвертый 16 и пятый 17 триггеры, счетчик 18 адресов чтения, второй элемент И-НЕ 19, первый 20 и второй 21 шинные формирователи и с первого по третий элементы НЕ 22-24.

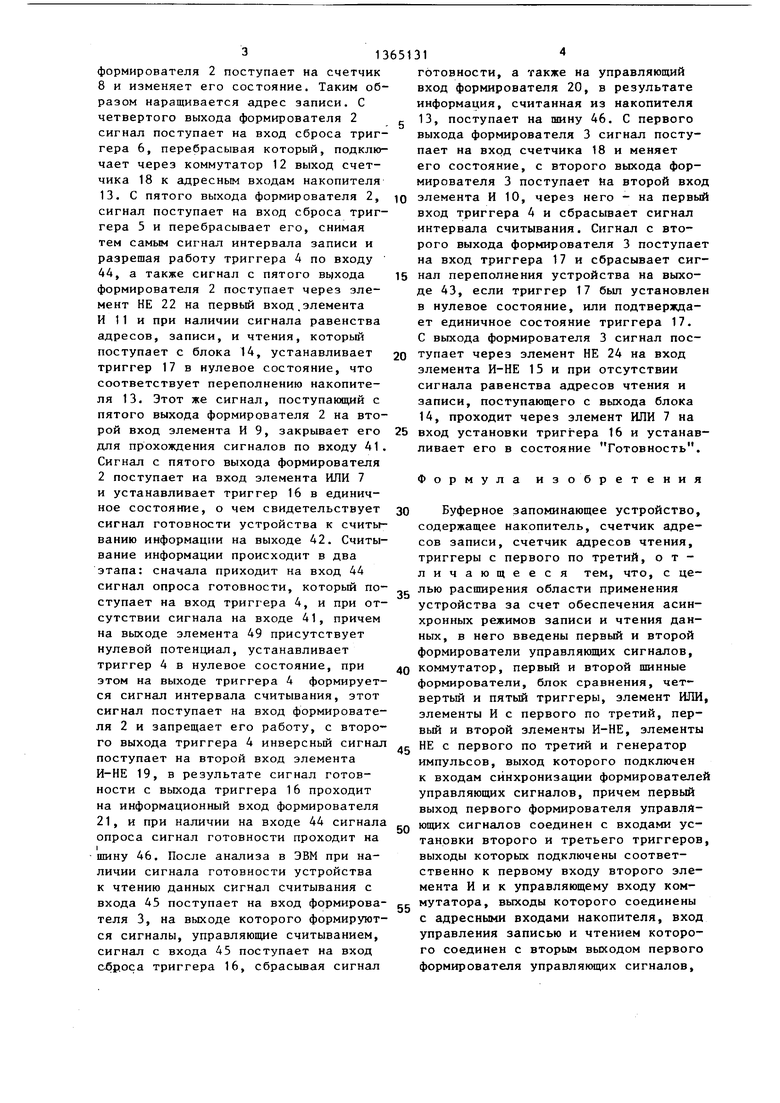

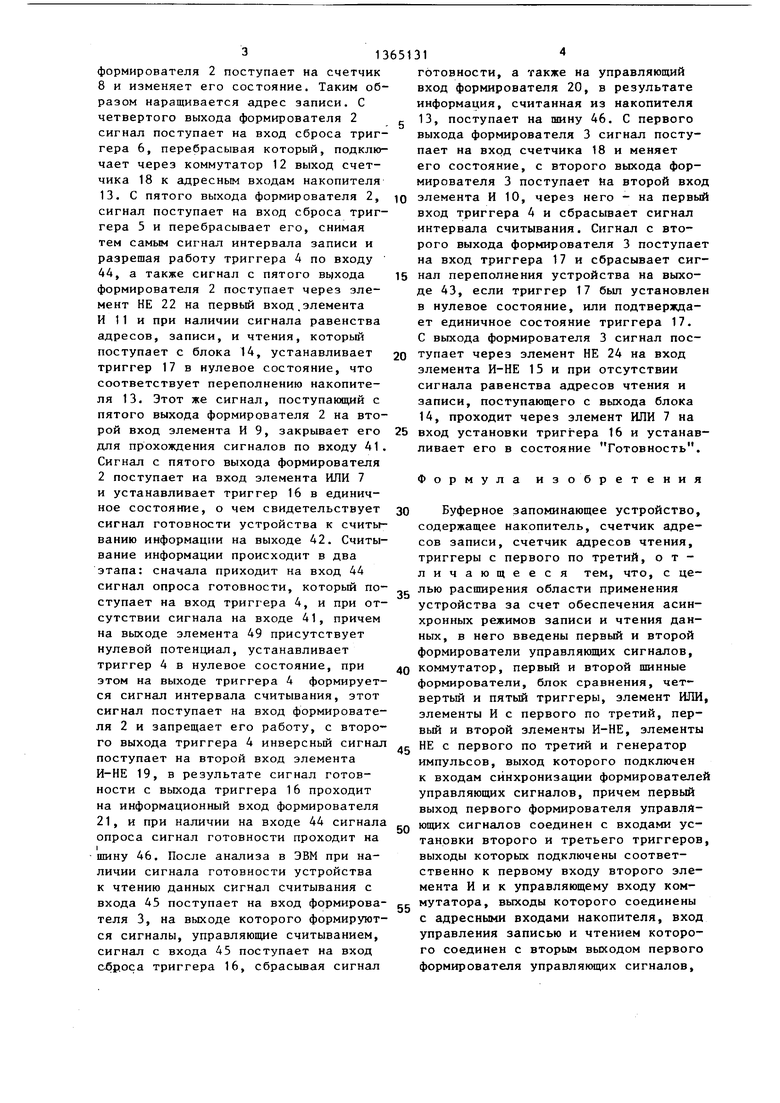

Первый формирователь 2 управляющи сигналов содержит (фиг.2) триггеры 25-30 и элементы И-НЕ 31-35. Второй формирователь 3 управляющих сигналов содержит (фиг.З) триггеры 36-38 и элементы И-НЕ 39 и 40.

Кроме того, устройство имеет (фиг.1) вход 41 записи, выходы 42 и

43сигнала готовности к чтению, вход

44опроса, вход 45 чтения, выходную шину 46 данных и информационные входы 47.

Устройство работает следующим образом .

Перед началом работы триггеры 4 и 6 (фиг.1), счетчики В и 18 и формирователи 2 и 3 устанавливаются в нулевое состояние, а триггеры 16 и 17 - в единичное (цепь установки на фиг.J не показана).

Единичное состояние выхода триггера 16 соответствует неготовности устройства к выдаче данных, а единичное состояние выхода триггера 17 - непереполненному состоянию накопителя 13, единичный сигнал с выхода триггера 17 поступает на вход элемента И 9 и при появлении единичного сигнала заявки на входе 41 элемента И 9 с его выхода сигнал 1 поступает на вход данных триггера 4, блокируя его работу по входу 44. Сигнал с выхода элемента И 9 поступает на вход запуска формирователя 2, на выходах которого формируются сигналы, управляющие записью информации. Сигнал с первого выхода формирователя 2 поступает на первьш вход триггера 5 и формирует на его выходе сигнал интервала записи, которьй поступает через элемент И 10 на выход триггера 4 и, устанавливая его в единичное состояние, блокирует вход 44, т.е. режим чтения. С первого выхода формирователя 2 сигнал поступает на вход установки триггера 6 и формирует на его выходе сигнал управления коммутатором 12, который подключает выходы счетчика 8 по адресным входам накопителя 13. Сигнал с второго выхода формирователя 2 поступает на вход управления записью и чтением накопителя 13, по этому сигналу информация, поступившая на входы 47 формирователя 20, через него записывается в накопитель 13. Сигнал с третьего выхода формирователя 2 поступает на вход счетчика 13. Сигнал с третьего выхода

31

формирователя 2 поступает на счетчик 8 и изменяет его состояние. Таким образом наращивается адрес записи. С четвертого выхода формирователя 2 сигнал поступает на вход сброса триггера 6, перебрасывая который, подключает через коммутатор 12 выход счетчика 18 к адресным входам накопителя 13. С пятого выхода формирователя 2, сигнал поступает на вход сброса триггера 5 и перебрасывает его, снимая тем самым сигнал интервала записи и разрешая работу триггера 4 по входу 44, а также сигнал с пятого выхода формирователя 2 поступает через элемент НЕ 22 на первый вход.элемента И 11 и при наличии сигнала равенства адресов, записи, и чтения, который поступает с блока 14, устанавливает триггер 17 в нулевое состояние, что соответствует переполнению накопителя 13. Этот же сигнал, поступаюпц й с пятого выхода формирователя 2 на второй вход элемента И 9, закрывает его для прохождения сигналов по входу 41 Сигнал с пятого выхода формирователя 2 поступает на вход элемента ИЛИ 7 и устанавливает триггер 16 в единичное состояние, о чем свидетельствует сигнал готовности устройства к считыванию информации на выходе 42. Считывание информации происходит в два этапа: сначала приходит на вход 44 сигнал опроса готовности, который поступает на вход триггера 4, и при отсутствии сигнала на входе 41, причем на выходе элемента 49 присутствует нулевой потенциал, устанавливает триггер 4 в нулевое состояние, при этом на выходе триггера 4 формируется сигнал интервала считывания, этот сигнал поступает на вход формирователя 2 и запрещает его работу, с второго выхода триггера 4 инверсный сигнал поступает на второй вход элемента И-НЕ 19, в результате сигнал готовности с выхода триггера 16 проходит на информационный вход формирователя 21, и при наличии на входе 44 сигнала опроса сигнал готовности проходит на

шину 46. После анализа в ЭВМ при наличии сигнала готовности устройства к чтению данных сигнал считывания с входа 45 поступает на вход формирова- теля 3, на выходе которого формируются сигналы, управляющие считыванием, сигнал с входа 45 поступает на вход сброса триггера 16, сбрасьшая сигнал

5 О Q

g

5

5

0

314

готовности, а также на управляющий вход формирователя 20, в результате информация, считанная из накопителя

13,поступает на шину 46. С первого выхода формирователя 3 сигнал поступает на вход счетчика 18 и меняет его состояние, с второго выхода формирователя 3 поступает На второй вход элемента И 10, через него - на первый вход триггера 4 и сбрасывает сигнал интервала считывания. Сигнал с второго выхода формирователя 3 поступает на вход триггера 17 и сбрасывает си1- нал переполнения устройства на выходе 43, если триггер 17 бьш установлен в нулевое состояние, или подтверждает единичное состояние триггера 17.

С выхода формирователя 3 сигнал поступает через элемент НЕ 24 на вход элемента И-НЕ 15 и при отсутствии сигнала равенства адресов чтения и записи, поступающего с выхода блока

14,проходит через элемент ИЛИ 7 на вход установки триггера 16 и устанавливает его в состояние Готовность.

Формула изобретения

Буферное запоминающее устройство, содержащее накопитель, счетчик адресов записи, счетчик адресов чтения, триггеры с первого по третий, отличающееся тем, что, с целью распшрения области применения устройства за счет обеспечения асинхронных режимов записи и чтения данных, в него введены первый и второй формирователи управляющих сигналов, коммутатор, первый и второй щинные формирователи, блок сравнения, четвертый и пятый триггеры, элемент ИЛИ, элементы И с первого по третий, первый и второй элементы И-НЕ, элементы НЕ с первого по третий и генератор импульсов, выход которого подключен к входам синхронизации формирователей управляющих сигналов, причем первый выход первого формирователя управляющих сигналов соединен с входами установки второго и третьего триггеров, выходы которых подключены соответственно к первому входу второго элемента И и к управляющему входу коммутатора, выходы которого соединены с адресными входами накопителя, вход управления записью и чтением которого соединен с вторым выходом первого формирователя управляющих сигналов.

51

третий выход которого подключен к счетному входу счетчика адресов записи, выходы которого соединены с одними из информационных входов коммутатора и блока сравнения, другие информационные входы которых подключены к выходам счетчика адресов чтения, счетный вход которого соединен с первым выходом второго формирова- теля управляющих сигналов, второй выход которого подключен к входу установки в 1 пятого триггера, входу третьего элемента НЕ и второму входу второго элемента И, выход которого соединен с входом асинхронной установки в 1 первого триггера, прямой выход которого подключен к входу сброса первого формирователя управля- Ю1ДИХ сигналов, четвертый выход кото- рого соединен с входом сброса третьего триггера, а пятый выход - с входом сброса второго триггера, первым входом элемента ИЛИ и входом первого элемента НЕ, выход которого подключен к первому входу третьего элемента И, выход которого соединен с входом установки в О пятого триггера, выход которого подключен к первому входу первого элемента И, выход которого соединен с входом, запуска первого формирователя управляющих сигналов и входом данных первого триггера, инверсный выход которого подключен к первому входу второго элемента И-НЕ, второй вход которого соединен с единичным выходом четвертого триггера, вход установки в 1

Q g 5 п

5

31е

которого подключен к выходу элемента ИЛИ, второй вход которого соединен с выходом первого элемента ИгНЕ, первый вход которого подключен к выходу третьего элемента НЕ, второй выход первого элемента И-НЕ соединен с выходом блока сравнения и входом второго элемента НЕ, выход которого подключен к второму входу третьего элемента И, информационные входы и выходы накопителя соединены с одними из информационных выходов и входов первого шинного формирователя, другие входы и выходы которого являются информационными входами и выходами устройства, выход второго элемента И-НЕ подключен к информационному входу второго шинного формирователя, выходы которого являются одними из выходов сигналов готовности к чтению устройства, управляющий вход первого шинного формирователя, второй вход второго формирователя управляющих сигналов и вход сброса четвертого триггера объединены и являются входом чтения устройства, вход установки в О первого триггера и управляющий вход второго шинного формирователя объединены и являются входом опроса устройства, входом записи и выходом разрешения записи которого являются соответственно второй вход первого элемента И и выход пятого триггера, четвертый выход первого формирователя управляющих сигналов является другим выходом сигнала готовности к чтению устройства.

J Фигг

цг.З

Составитель Т.Зайцева

Редактор О.Головач

Техред М.Ходанич

Заказ 6641/45Тираж 590Подписное

ВНЙИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

t 10.17.2

Корректор М.Демчик

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-01-07—Публикация

1986-05-13—Подача