ел

оо о со

1

Изобретение относится к цифровой технике и может быть использовано в цифровых системах с повышенной достоверностью функционирования для контроля правильности функционирования цифровых блоков, формирующих на своих выходах периодически повторяющиеся последовательности импульсов

Целью изобретения является расши- рение функциональных возможностей за счет обеспечения кбнтроля последовательностей с переменным периодом.

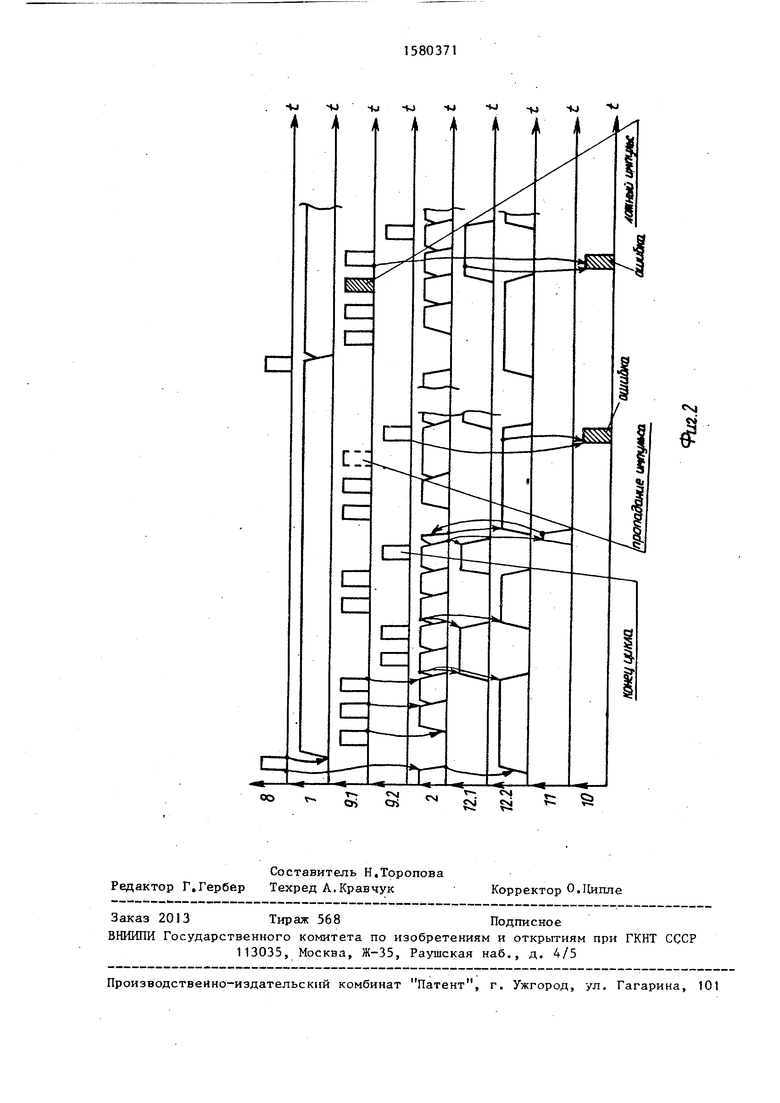

На фиг.1 изображена функциональная схема устройства; на фиг.2 - вре- менные диаграммы его работы для случая п 2,

Устройство содержит регистр 1, счетчик 2, блок 3 памяти, коммутатор 4, первый 5 и второй 6 элементы ИЛИ, входы 7 и 8 соответственно кода номера контролируемой последовательности и пуска устройства, первый,,, n-й информационные входы 9el-9.ni, выход 10 сигнала ошибки устройства, первый выход 11 блока 3, втор6йоое (п+1)-й выходы 12.1-12.п блока 3.

На фиг.2 использованы обозначения, введенные на фиг.1.

Рассматривают назначение основных элементов устройства.

Регистр 1 предназначен для хранения кода номера контролируемой последовательности. Этот код задает адрес страницы в блоке 3, который содержит эталонные значения последовательности выходных сигналов. Запись кода в регистр 1 осуществляется

по заднему фронту импульса, поступающего на его вход стробирования с вхо- да 8 устройства.

Счетчик 2 предназначен для формирования адреса слова в пределах страницы блока 3 путем подсчета общего количества импульсов, поступивших со всех информационных входов. Изменение состояния счетчика 2 происходит по заднему фронту импульса на счетном входе.

Блок 3 постоянной памяти предназна чен для хранения слов, задающих по- тактно эталонные значения, последовательности контролируемых импульсов.

Каждое слово в ПЗУ содержит (п+1) разрядов.

Второй...(п+1)-и разряды, подаваемые соответственно на входы 12,1- 12,п блока 3, задают эталонные значения контролируемых сигналом, поступающих на соответствующие входы 9.1- 9.п устройства в конце текущего такта работы устройства. (Под тактом работы устройства понимается его функционирование от прихода одного импульса на один из информационных входов до прихрда ближайшего импульса на любой информационный вход устройства)0 Значение разряда принимается равным нулю, если на соответствующий вход должен поступить импульс; в противном случае значение разряда принимается равным единице.

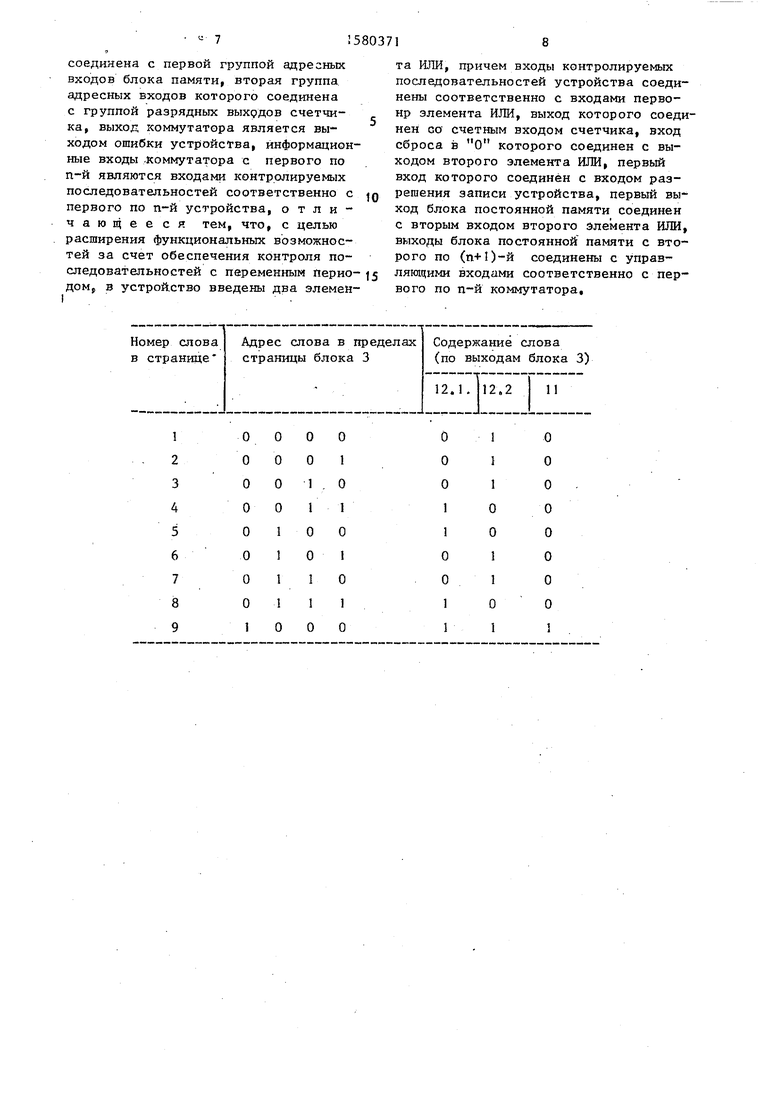

Первый разряд слова подается на выход 11 блока 3 и задает конец цикла контролируемой последовательности сигналов,, Во всех словах, соответствующих тому или -иному блоку, на выходах которого формируется последовательность сигналов с циклом длиной L тактов, значения этого разряда кодируется нулем, кроме последнего, L+1-го слова, в котором все разряды слова должны быть равны единице. Пример кодирования страницы ПЗУ при в случае контроля последовательности типа 3-2-2-1 (т.е. один цикл которой содержит три импульса в первой фазе, а затем два импульса во второй фазе, а затем один импульс во второй фазе) приведен в таблице0

Коммутатор 4 предназначен для формирования сигнала ошибки на выходе 10 устройства путем подключения к этому выходу того информационного входа устройства, на котором в текущем такте импульс появиться не должен. Подключение этого входа к выходу коммутатора осуществляется единичным значением сигнала на соответствующем управляющем входео

Элемент ИЛИ 5 формирует сигналы на счетном входе счетчика 2 адреса.

Элемент ИЛИ 6 предназначен для формирования сигнала, обнуляющего счетчик 2 адреса либо по окончании цикла контролируемой последовательности, либо после переключения устройства на контроль другого блока, которому соответствует другая последовательность импульсов,

Рассматривают работу устройства при в процессе контроля одного цикла последовательности типа 3-2-2-1 когда соответствующая страница блока 3 закодирована так, как показано в таблице. При этом разрядность счетчи515

ка 2 адреса должна быть не меньше четырех.

Пусть контролируемая последовательность формируется без искажений„ По заднему фронту сигнала Пуск с входов устройства в регистр 1 записывается код адреса страницы блока 3 соответствующей контролируемой последовательности о Сигнал Пуск, пройдя через элемент ИЛИ 6, обнуляет счетчик 2 адреса. На выходах блока 3 при этом сигналы имеют значения, соответствующие первому слову страницы (таблица)о Нулевой сигнал с выхода 12.1 блока 3 запрещает прохождение импульса с входа 9,1 на выход 10 ошибки. Единичным же сигналом с выхода 12.2 блока 3 разрешается прохождение через коммутатор 4 сигнала с вхо- да 902 на выход 10 и если на нем появляется в этом такте ложный дополнительный импульс, то он поступает на выход 10, сигнализируя об ошибке„ С приходом первого и второго импуль- сов контролируемой последовательности содержимое счетчика 2 становится соответственно 001 и 010, вследствие чего на выходы блока 3 последовательно поданы слова номер 2 и 3 (таблица). Поскольку эти слова cog- падают с нулевым словом, то значения выходных сигналов блока 3 сохраняются. С приходом на вход 901 третьего импульса на выход блока 3 подано слов номер четыре о При этом в коммутаторе 4 нулевым сигналом с выхода 1202 блока 3 вход 9,2 устройства отключен от выхода 10, а единичным сигналом с выхода 12,1 вход 9.1 скоммутирован на выход 10 ошибки устройства. Этим самым устройство подготовлено к контролю серии импульсов на входе 902, Далее контроль осуществляется аналогично вышеизложенному.С приходом пос- леднего импульса в цикле контролируемой последовательности на выходы блока 3 подано заключительное слово (в данном случае девятое), единичный сигнал которого с выхода 11 блока 3 через элемент ИЛИ 6, устанавливает счетчик 2 адреса в исходное нулевое состояние При этом устройство подготовлено к контролю нового цикла контролируемой последовательностиа При необходимости перейти к контролю последовательности другого типа необходимо код ее адреса занести в регистр 1.

Если в контролируемой последовательности произошло пропадание импульса на одном из информационных входов, то по окончании серии импульсов на этом входе устройство своевременно не переключается на контроль импульсов на другом входе из-за отставания счетчика 2 адреса Вследствие этого первый импульс проходит на выход 10 огаибки устройства через тот информационный вход коммутатора 4Р который из-за отставания счетчика к тому времени еще не отключек от выхода коммутатора. Например, если пропадет третий по счету импульс цикла контролируемой последовательности (фиг02), то счетчик 2 сохранит прежнее состояние 0010 вместо перехода в состояние ООП. Поэтому к моменту прихода четвертого импульса, поступающего с входа 9.2, на выходы блока 3 вместо четвертого слова поступает третье. Единичным сигналом с-выхода 12.2 на выход 10 огаибки по прежнему скоммутирован вход 9.2, по которому поступает четвертый импульс0 Появление этого импульса на выходе 10 сигнализирует об искажении контролируемой последовательности.

Если на каком-либо информационном входе появляется дополнительный импульс, то первый импульс, который должен перевести устройство на контроль серии импульсов по другому входу, поступает на выход 10 устройства. Например, (фиг.2), если после второго импульса цикла появляется дополнительный импульс, то по его приходу на выходы блока 3 уже подано четвертое слово, и вход 9.1 подключен к выходу 10 ошибки.

Следовательно, третий истинный импульс цикла, пройдя на выход 10, падает сигнал об искажении последовательности,

Формула изобретения

Устройство для контроля последовательностей импульсов, содержащее регистр, блок постоянной памяти, коммутатор и счетчик, причем группа информационных входов регистра является группой входов номера контролируемой последовательности устройства, вход разрешения записи регистра является входом разрешения записи устройства, группа выходов регистра

соединена с первой группой адресных входов блока памяти, вторая группа адресных входов которого соединена с группой разрядных выходов счетчика, выход коммутатора является выходом ошибки устройства, информационные входы коммутатора с первого по n-й являются входами контролируемых последовательностей соответственно с первого по n-й устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения контроля последовательностей с переменным периодомр в устройство введены два элемен

та ИЛИ, причем входы контролируемых последовательностей устройства соединены соответственно с входами перво- нр элемента ИЛИ, выход которого соединен со счетным входом счетчика, вход сброса в О которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с входом разрешения записи устройства, первый выход блока постоянной памяти соединен с вторым входом второго элемента ИЛИ, выходы блока постоянной памяти с второго по (п+1)-й соединены с управляющими входами соответственно с первого по n-й коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля двух последовательностей импульсов | 1988 |

|

SU1596336A1 |

| Устройство для контроля двух последовательностей импульсов | 1986 |

|

SU1376088A1 |

| Устройство для контроля управляющих сигналов микропроцессора | 1989 |

|

SU1656536A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1991 |

|

SU1807516A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

Изобретение относится к цифровой технике и может быть использовано для контроля правильности функционирования цифровых блоков, на выходах которых формируется периодически повторяющиеся последовательности импульсов. Отличительной особенностью устройства является то, что оно позволяет контролировать последовательности с переменным числом импульсов. Цель изобретения является расширение функциональных возможностей за счет обеспечения контроля последовательностей с переменным периодом. Поставленная цель достигается за счет введения элементов ИЛИ 5, 6 и новых связей, 1 табл. 2 ил.

1 2 3 4 5 6 7 8 9

4JtJ tJ fj-W

00

«O

«VI

| Устройство для контроля двух импульсных последовательностей | 1984 |

|

SU1244666A1 |

| Устройство для контроля двух последовательностей импульсов | 1986 |

|

SU1376088A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-07-23—Публикация

1988-12-13—Подача