Изобретение относится к цифровой вычислительной технике и может быть использовано в ЭВМ и цифровых системах с повышенной достоверностью функционирования.

Цель изобретения - повышение достоверности контроля.

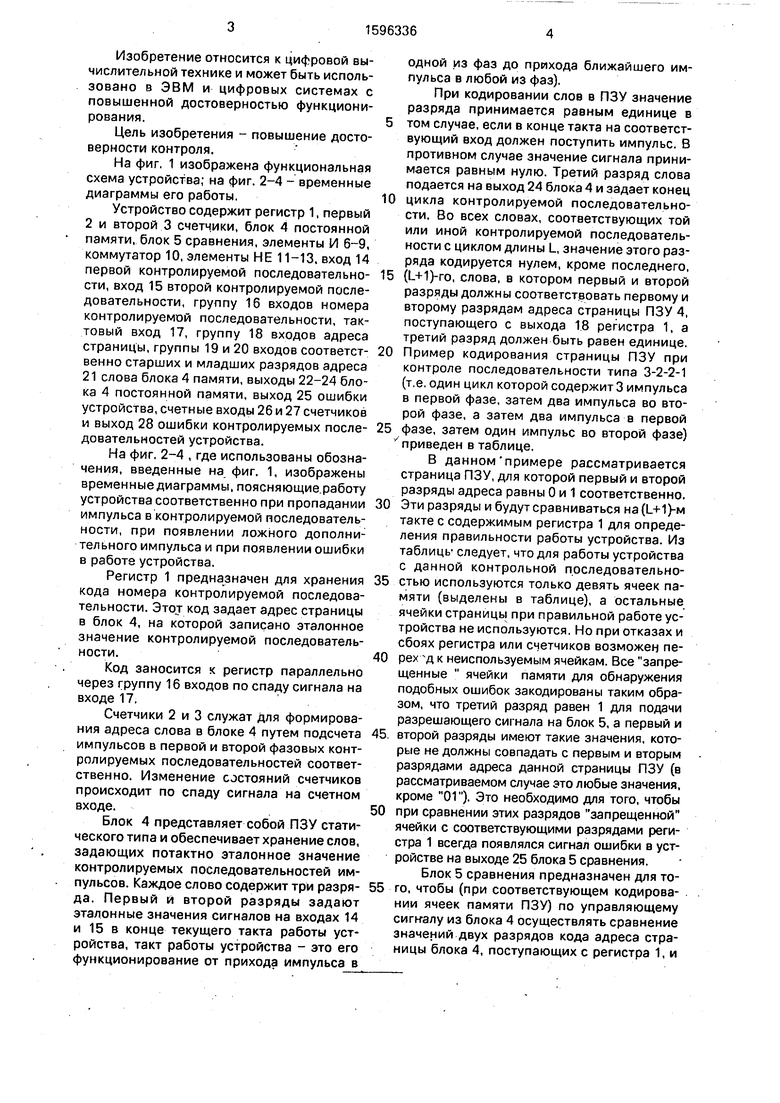

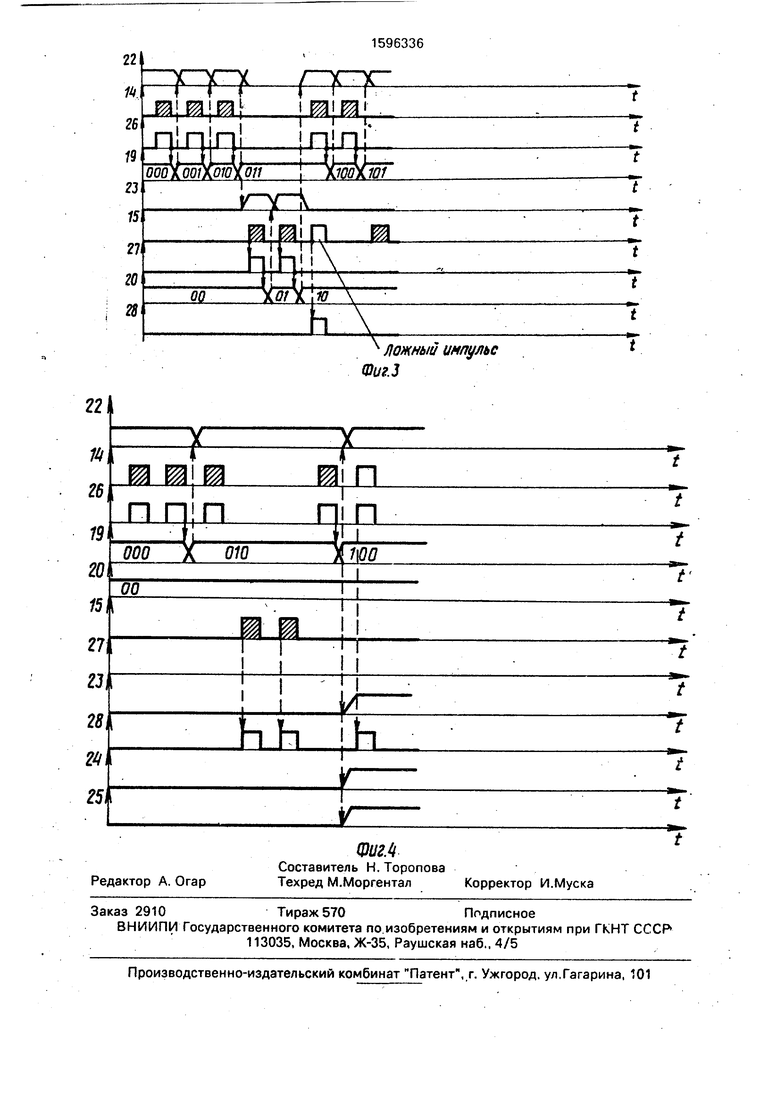

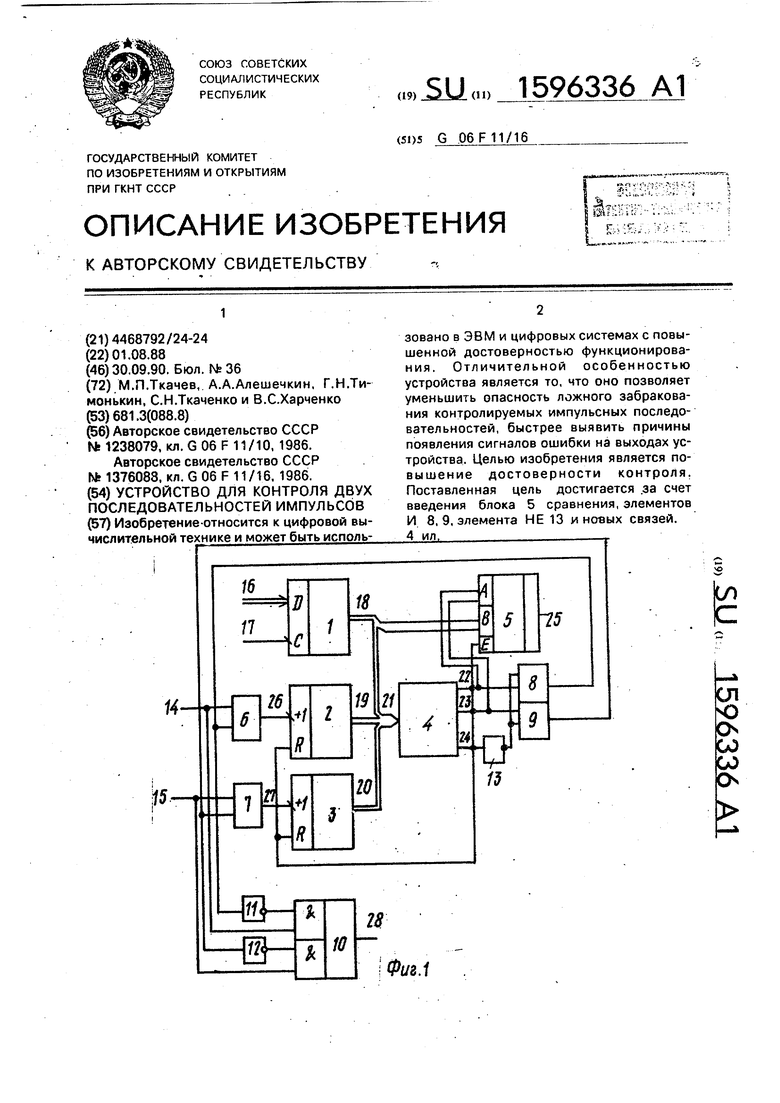

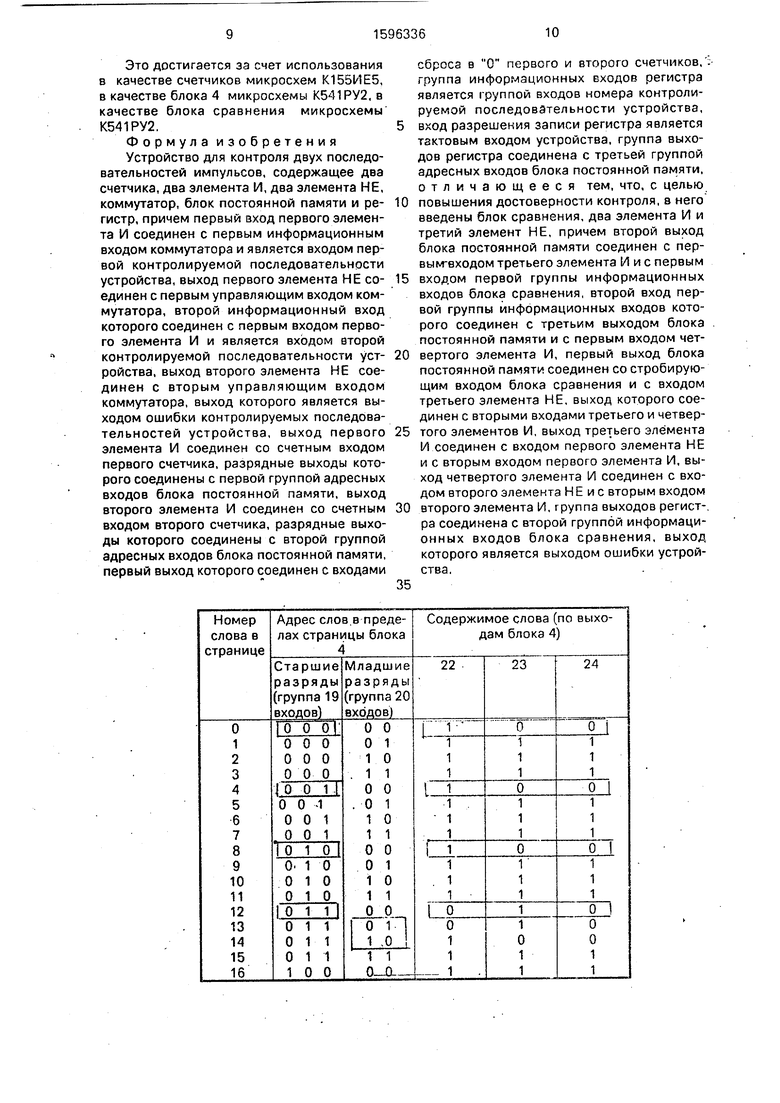

На фиг. 1 изображена функциональная схема устройства; на фиг. 2-4 - временные диаграммы его работы.

Устройство содержит регистр 1, первый 2 и второй 3 счетчики, блок 4 постоянной памяти, блок 5 сравнения, элементы И 6-9, коммутатор 10, элементы НЕ 11-13, вход 14 первой контролируемой последовательности, вход 15 второй контролируемой последовательности, группу 16 входов номера контролируемой последовательности, тактовый вход 17, группу 18 входов адреса страницы, группы 19 и 20 входов соответственно старших и младших разрядов адреса 21 слова блока 4 памяти, выходы 22-24 блока 4 постоянной памяти, выход 25 ошибки устройства, счетные входы 26 и 27 счетчиков и выход 28 ошибки контролируемых последовательностей устройства.

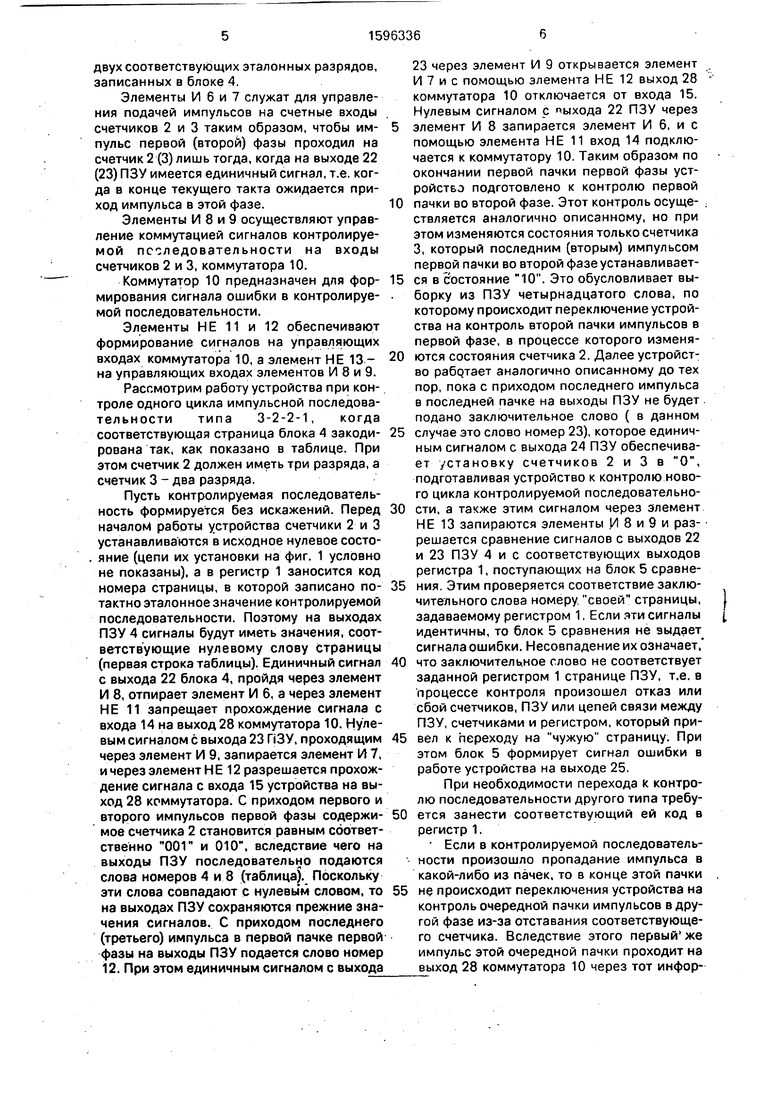

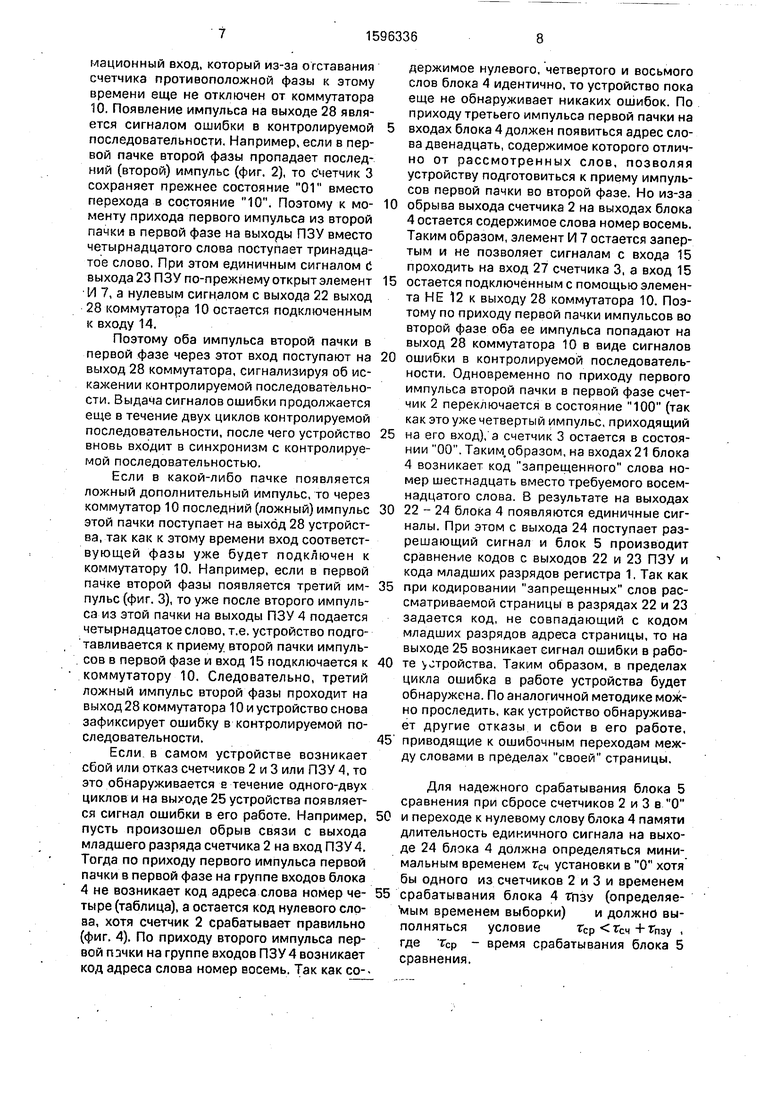

На фиг. 2-4 , где использованы обозначения, введенные на фиг, 1, изображены временные диаграммы, поясняющие.работу устройства соответственно при пропадании импульса в контролируемой последовательности, при появлении ложного дополнительного импульса и при появлении ошибки в работе устройства.

Регистр 1 предназначен для хранения кода номера контролируемой последовательности. Этот код задает адрес страницы в блок 4, на которой записано эталонное значение контролируемой последовательности.

Код заносится к регистр параллельно через группу 16 входов по спаду сигнала на входе 17.

Счетчики 2 и 3 служат Для формирования адреса слова в блоке 4 путем подсчета импульсов в первой и второй фазовых контролируемых последовательностей соответственно. Изменение состояний счетчиков происходит по спаду сигнала на счетном входе.

Блок 4 представляет собой ПЗУ статического типа и обеспечивает хранение слов, задающих потактно эталонное значение контролируемых последовательностей импульсов. Каждое слово содержит три разряда. Первый и второй разряды задают эталонные значения сигналов на входах 14 и 15 в конце текущего такта работы устройства, такт работы устройства - это его функционирование от прихода импульса в

одной из фаз до прихода ближайшего импульса в любой из фаз).

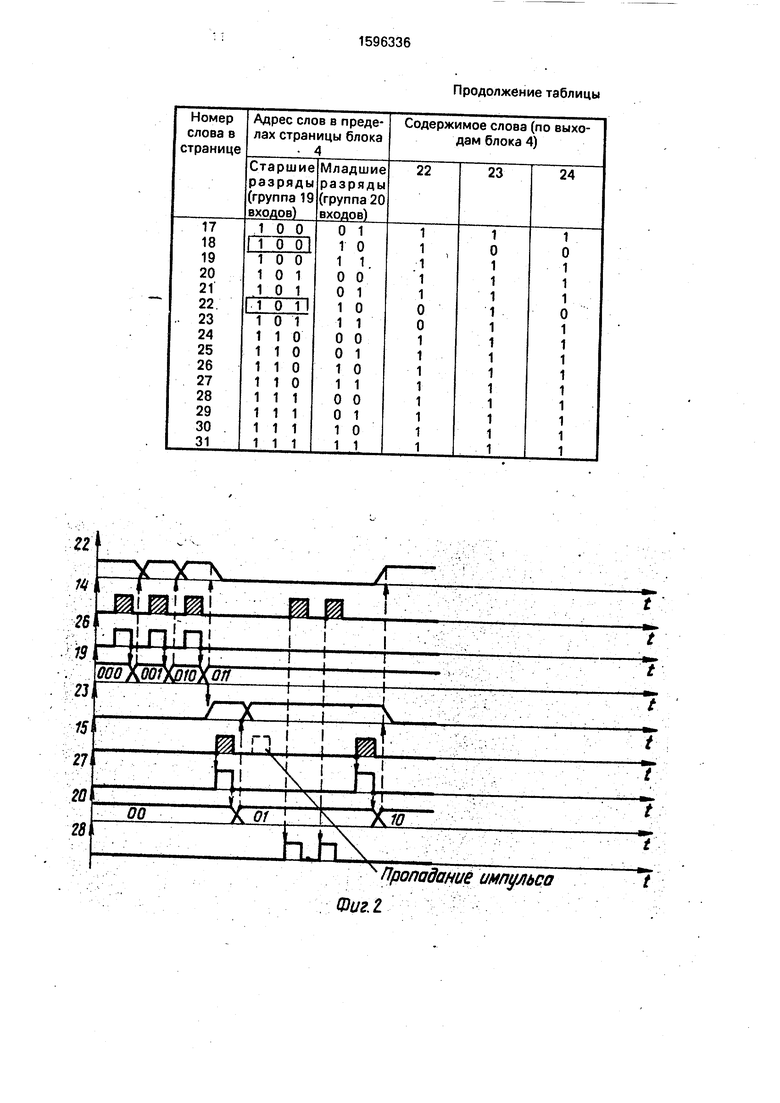

При кодировании слов в ПЗУ значение разряда принимается равным единице в

том случае, если в конце такта на соответствующий вход должен поступить импульс. В противном случае значение сигнала принимается равным нулю. Третий разряд слова подается на выход 24 блока 4 и задает конец

цикла контролируемой последовательности. Во всех словах, соответствующих той или иной контролируемой последовательности с циклом длины L, значение этого разряда кодируется нулем, кроме последнего,

(L+1)-ro, слова, в котором первый и второй разряды должны соответствовать первому и второму разрядам адреса страницы ПЗУ 4, поступающего с выхода 18 регистра 1, а третий разряд должен быть равен единице.

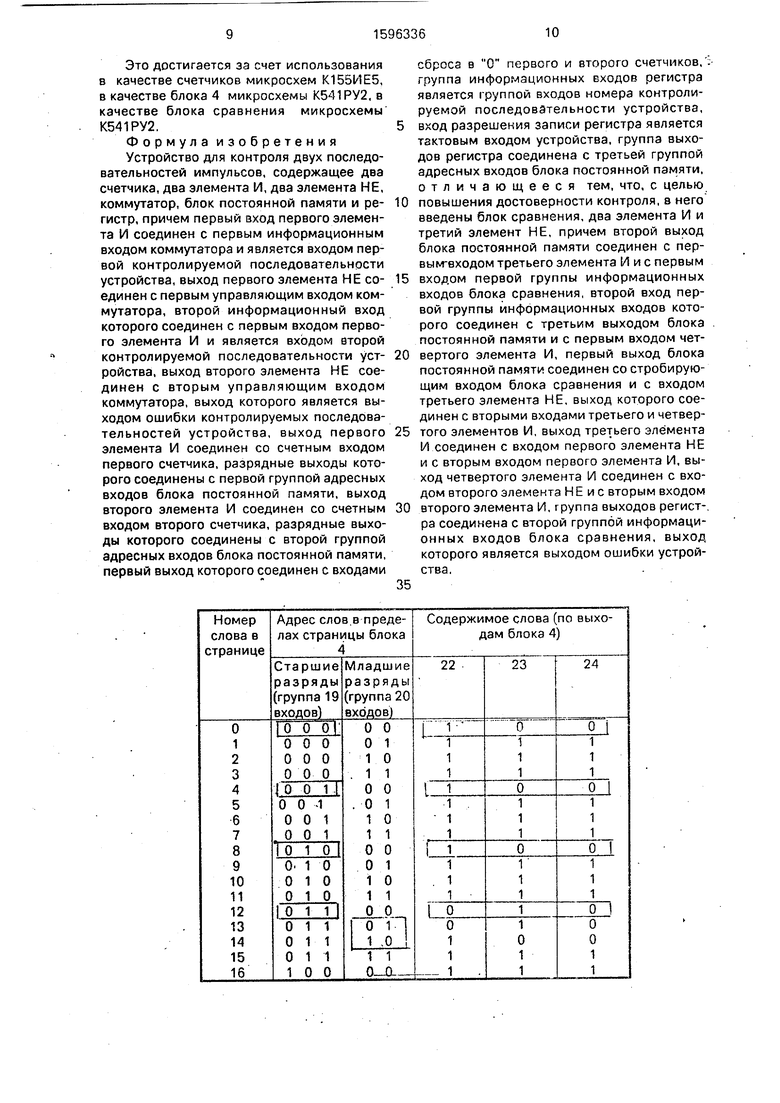

Пример кодирования страницы ПЗУ при контроле последовательности типа 3-2-2-1 (т.е. один цикл которой содержит 3 импульса в первой фазе, затем два импульса во второй фазе, а затем два импульса в первой

фазе, затем один импульс во второй фазе) приведен в таблице.

В данномпримере рассматривается страница ПЗУ, для которой первый и второй разряды адреса равны О и 1 соответственно.

Эти разряды и будут сравниваться на {L+1)-M такте с содержимым регистра 1 для определения правильности работы устройства. Из таблицы следует, что для работы устройства с данной контрольной последовательностью используются только девять ячеек памяти (выделены в таблице), а остальные ячейки страниць при правильной работе устройства не используются. Но при отказах и сбоях регистра или счетчиков возможен перех д к неиспользуемым ячейкам. Все запрещенные ячейки памяти для обнаружения подобных ошибок закодированы таким образом, что третий разряд равен 1 для подачи разрешающего сигнала на блок 5, а первый и

второй разряды имеют такие значения, которые не должны совпадать с первым и вторым разрядами адреса данной страницы ПЗУ (в рассматриваемом случае это любые значения, кроме 01). Это необходимо для того, чтобы

при сравнении этих разрядов запрещенной ячейки с соответствующими разрядами регистра 1 всегда появлялся сигнал ошибки в устройстве на выходе 25 блока 5 сравнения. Блок 5 сравнения предназначен для того, чтобы (при соответствующем кодировании ячеек памяти ПЗУ) по управляющему сигналу из блока 4 осуществлять сравнение значений двух разрядов кода адреса страницы блока 4, поступающих с регистра 1, и

двух соответствуйэщих эталонных разрядов, записанных в блоке 4.

Элементы И 6 и 7 служат для управления подачей импульсов на счетные входы счетчиков 2 и 3 таким образом, чтобы импульс первой (второй) фазы проходил на счетчик 2 (3) лишь тогда, когда на выходе 22 (23) ПЗУ имеется единичный сигнал, т.е. когда в конце текущего такта ожидается приход импульса в этой фазе.

Элементы И 8 и 9 осуществляют управление коммутацией сигналов контролируемой последовательности на входы счетчиков 2 и 3, коммутатора 10.

Коммутатор 10 предназначен для формирования сигнала ошибки в контролируемой последовательности.

Элементы НЕ 11 и 12 обеспечивают формирование сигналов на управляющих

входах коммутатора 10, а элемент НЕ 13 на управляющих входах элементов И 8 и 9.

Рассмотрим работу устройства при контроле одного цикла импульсной последовательности типа 3-2-2-1, когда соответствующая страница блока 4 закодирована так, как показано в таблице. При этом счетчик 2 должен иметь три разряда, а счетчик 3 - два разряда.

Пусть контролируемая последовательность фopмиpyetcя без искажений. Перед началом работы устройства счетчики 2 и 3 устанавливаются в исходное нулевое состояние (цепи их установки на фиг. 1 условно не показаны), а в регистр 1 заносится код номера страницы, в которой записано потактно эталонное значение контролируемой последовательности. Поэтому на выходах ПЗУ 4 сигналы будут иметь значения, соответствующие нулевому слову страницы (первая строка таблицы). Единичный сигнал с выхода 22 блока 4, пройдя через элемент И 8, отпирает элемент И 6, а через элемент НЕ 11 запрещает прохождение сигнала с входа 14 на выход 28 коммутатора 10. Нулевым сигналом с выхода 23 ПЗУ, проходящим через элемент И 9, запирается элемент И 7, и через элемент НЕ 12 разрешается прохождение сигнала с входа 15 устройства на выход 28 коммутатора. С приходом первого и второго импульсов первой фазы содержимое счетчика 2 становится равным соответственно 001 и 010, вследствие чего на выходы ПЗУ последовательно подаются слова номеров 4 и 8 (таблица). Поскольку эти слова совпадают с нулевым словом, то на выходах ПЗУ сохраняются прежние значения сигналов. С приходом последнего (третьего) импульса в первой пачке первой фазы на выходы ПЗУ подается слово номер 12. При этом единичным сигналом с выхода

23 через элемент И 9 открывается элемент И 7 и с помощью элемента НЕ 12 выход 28 коммутатора 10 отключается от входа 15. Нулевым сигналом с пыхода 22 ПЗУ через

5 элемент И 8 запирается элемент И 6, и с помощью элемента НЕ 11 вход 14 подключается к коммутатору 10. Таким образом по окончании первой пачки первой фазы устройство подготовлено к контролю первой

0 пачки во второй фазе. Этот контроль осуществляется аналогично описанному, но при этом изменяются состояния только счетчика 3, который последним (вторым) импульсом первой пачки во второй фазеустанавливает5 ся в состояние 10. Это обусловливает выборку из ПЗУ четырнадцатого слова, по которому происходит переключение устройства на контроль второй пачки импульсов в первой фазе, в процессе которого изменя0 ются состояния счетчика 2. Далее устройство рабртает аналогично описанному до тех пор, пока с приходом последнего импульса в последней пачке на выходы ПЗУ не будет . подано заключительное слово ( в данном

5 случае это слово номер 23), которое единичным сигналом с выхода 24 ПЗУ обеспечивает установку счетчиков 2 и 3 в О, подготавливая устройство к контролю нового цикла контролируемой последовательности, а также этим сигналом через элемент НЕ 13 запираются элементы И 8 и 9 и разрешается сравнение сигналов с выходов 22 и 23 ПЗУ 4 и с соответствующих выходов регистра 1, поступающих на блок 5 сравнения. Этим проверяется соответствие заключительного слова номеру своей страницы, задаваемому регистром 1, Если .чти сигналы идентичны, то блок 5 сравнения не эыдает сигнала ошибки. Несовпадение их означает,

0 что заключительное слово не соответствует заданной регистром 1 странице ПЗУ, т.е. в процессе контроля произошел отказ или сбой счетчиков, ПЗУ или цепей связи между ПЗУ, счетчиками и регистром, который привел к переходу на чужую страницу. При этом блок 5 формирует сигнал ошибки в работе устройства на выходе 25.

При необходимости перехода k контролю последовательности другого типа требуется занести соответствующий ей код в регистр 1.

Если в контролируемой последовательности произошло пропадание импульса в какой-либо из пачек, то в конце этой пачки

5 не происходит переключения устройства на контроль очередной пачки импульсов в другой фазе из-за отставания соответствующего счетчика. Вследствие этого первыйже импульс этой очередной пачки проходит на

вь1ход 28 коммутатора 10 через тот информационный вход, который из-за огставания счетчика противоположной фазы к этому времени еще не отключен от коммутатора 10. Появление импульса на выходе 28 является сигналом ошибки в контролируемой последовательности. Например, если в первой пачке второй фазы пропадает последний (второй) импульс (фиг. 2), то счетчик 3 сохраняет прежнее состояние 01 вместо перехода в состояние 10. Поэтому к моменту прихода первого импульса из второй пачки в первой фазе на выходы ПЗУ вместо четырнадцатого слова поступает тринадцатое слово. При этом единичным сигналом С выхода 23 ПЗУ по-прежнему открыт элемент И 7, а нулевым сигналом с выхода 22 выход 28 коммутатора 10 остается подключенным к входу 14.

Поэтому оба импульса второй пачки в первой фазе через этот вход поступают на выход 28 коммутатора, сигнализируя об искажении контролируемой последовательности. Выдача сигналов ошибки продолжается еще в течение двух циклов контролируемой последовательности, после чего устройство вновь входит в синхронизм с контролируемой последовательностью.

Если в какой-либо пачке появляется ложный дополнительный импульс, то через коммутатор 10 последний (ложный) импульс этой пачки поступает на выход 28 устройства, так как к этому времени вход соответствующей фазы уже будет подключен к коммутатору 10. Например, если в первой пачке второй фазы появляется третий импульс (фиг. 3), то уже после второго импульса из этой пачки на выходы ПЗУ 4 подается четырнадцатое слово, т.е. устройство подготавливается к приему второй пачки импульсов в первой фазе и вход 15 подключается к коммутатору 10. Следовательно, третий ложный импульс второй фазы проходит на выход 28 коммутатора 10 и устройство снова зафиксирует ошибку в контролируемой последовательности.

Если, в самом устройстве возникает сбой или отказ счетчиков 2 и 3 или ПЗУ 4, то это обнаруживается Е течение одного-двух циклов и на выходе 25 устройства появляется сигнал ошибки в его работе. Например, пусть произошел обрыв связи с выхода младшего разряда счетчика 2 на вход ПЗУ 4. Тогда по приходу первого импульса первой пачки в первой фазе на группе входов блока 4 не возникает код адреса слова номер четыре (таблица), а остается код нулевого слова, хотя счетчик 2 срабатывает правильно (фиг. 4). По приходу второго импульса первой пэчки на группе входов ПЗУ 4 возникает код адреса слова номер восемь. Так как со-.

держимое нулевого, четвертого и восьмого слов блока 4 идентично, то устройство пока еще не обнаруживает никаких ошибок. По приходу третьего импульса первой пачки на

входах блока 4 должен появиться адрес слова двенадцать, содержимое которого отлично от рассмотренных слов, позволяя устройству подготовиться к приему импульсов первой пачки во второй фазе. Но из-за

обрыва выхода счетчика 2 на выходах блока 4 остается содержимое слова номер восемь. Таким образом, элемент И 7 остается запертым и не позволяет сигналам с входа 15 проходить на вход 27 счетчика 3, а вход 15

остается подключённым с помощью элемента НЕ 12 к выходу 28 коммутатора 10. Поэтому по приходу первой пачки импульсов во второй фазе оба ее импульса попадают на выход 28 коммутатора 10 в виде сигналов

ошибки в контролируемой последовательности. Одновременно по приходу первого импульса второй пачки в первой фазе счетчик 2 переключается в состояние 100 (так как это уже четвертый импульс, приходящий

на его вход), а счетчик 3 остается в состоянии 00.Таким.образом, на входах 21 блока 4 возникает код запрещенного слова номер шестнадцать вместо требуемого восемнадцатого слова. В результате на выходах

22 - 24 блока 4 появляются единичные сигналы. При этом с выхода 24 поступает разрешающий сигнал и блок 5 производит сравнение кодов с выходов 22 и 23 ПЗУ и кода младших разрядов регистра 1. Так как

при кодировании запрещенных слов рассматриваемой страницы в разрядах 22 и 23 задается код, не совпадающий с кодом младших разрядов адреса страницы, то на выходе 25 возникает сигнал ошибки в работе устройства. Таким образом, в пределах цикла ошибка в работе устройства будет обнаружена. По аналогичной методике можно проследить, как устройство обнаруживает другие отказы и сбои в его работе,

приводящие к ошибочным переходам между словами в пределах своей страницы.

Для надежного срабатывания блока 5 сравнения при сбросе счетчиков 2 и 3 в О

и переходе к нулевому слову блока 4 памяти длительность единичного сигнала на выходе 24 блока 4 должна определяться минимальным временем Гсч установки в О хотя бы одного из счетчиков 2 и 3 и временем

срабатывания блока 4 ГПЗУ (определяемым временем выборки) и должно выполняться условиеТер Тсч + , где Тер - время срабатывания блока 5 сравнения.

Это достигается за счет использования в качестве счетчиков микросхем К15ьИЕ5, в качестве блока 4 микросхемы К541РУ2, в качестве блока сравнения микросхемы К541РУ2.

Формула изобретения Устройство для контроля двух последовательностей импульсов, содержащее два счетчика, два элемента И, два элемента НЕ, коммутатор, блок постоянной памяти и регистр, причем первый вход первого элемента И соединен с первым информационным входом коммутатора и является входом первой контролируемой последовательности устройства, выход первого элемента НЕ соединен с первым управляющим входом коммутатора, второй информационный вход которого соединен с первым входом первого элемента И и является входом второй контролируемой последовательности устройства, выход второго элемента НЕ соединен с вторым управляющим входом коммутатора, выход которого является выходом ошибки контролируемых последовательностей устройства, выход первого элемента И соединен со счетным входом первого счетчика, разрядные выходы которого соединены с первой группой адресных входов блока постоянной памяти, выход второго элемента И соединен со счетным входом второго счетчика, разрядные выходы которого соединены с второй группой адресных входов блока постоянной памяти, первый выход которого соединен с входами

сброса в О первого и второго счетчиков, группа информационных входов регистра является группой входов номера контролируемой последовательности устройства, вход разрешения записи регистра является тактовым входом устройства, группа выходов регистра соединена с третьей группой адресных входов блока постоянной памяти, отличающееся тем, что, с целью повышения достоверности контроля, в него введены блок сравнения, два элемента И и третий элемент НЕ, причем второй выход блока постоянной памяти соединен с первым входом третьего элемента Л и с первым входом первой группы информационных входов блока сравнения, второй вход первой группы информационных входов которого соединен с третьим выходом блока постоянной памяти и с первым входом четвертого элемента И, первый выход блока постоянной памяти соединен со стробирующим входом блока сравнения и с входом третьего элемента НЕ, выход которого соединен с вторыми входами третьего и четвертого элементов И, выход третьего элемента И соединен с входом первого элемента НЕ и с вторым входом первого элемента И, выход четвертого элемента И соединен с входом второго элемента Н Е и с вторым входом второго элемента И, группа выходов регист-. ра соединена с второй группой информационных входов блока сравнения, выход которого является выходом ошибки устройства.

Продолжение таблицы MLMIM MIMi )KHbiu импульс Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля двух последовательностей импульсов | 1986 |

|

SU1376088A1 |

| Устройство для контроля последовательностей импульсов | 1988 |

|

SU1580371A1 |

| Устройство для контроля управляющих сигналов микропроцессора | 1989 |

|

SU1656536A1 |

| Устройство для контроля управляющей вычислительной машины | 1987 |

|

SU1464163A1 |

| РЕЛЕ ЧАСТОТЫ ИЛИ ФАЗЫ | 1993 |

|

RU2056693C1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Устройство микропрограммногоупРАВлЕНия | 1979 |

|

SU809184A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в ЭВМ и цифровых системах с повышенной достоверностью функционирования. Отличительной особенностью устройства является то, что оно позволяет уменьшить опасность ложного забракования контролируемых импульсных последовательностей, быстрее выявить причины появления сигналов ошибки на выходах устройства. Целью изобретения является повышение достоверности контроля. Поставленная цель достигается за счет введения блока 5 сравнения, элементов И 8, 9, элемента НЕ 13 и новых связей. 4 ил.

| Устройство для контроля распределителя импульсов | 1984 |

|

SU1238079A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-09-30—Публикация

1988-08-01—Подача