§

(Л

Изобретение относится к вычислительной технике и предназначено для использования в быстродействующих вычислительных машинах.

Цель изобретения - сокращение аппаратурных затрат.

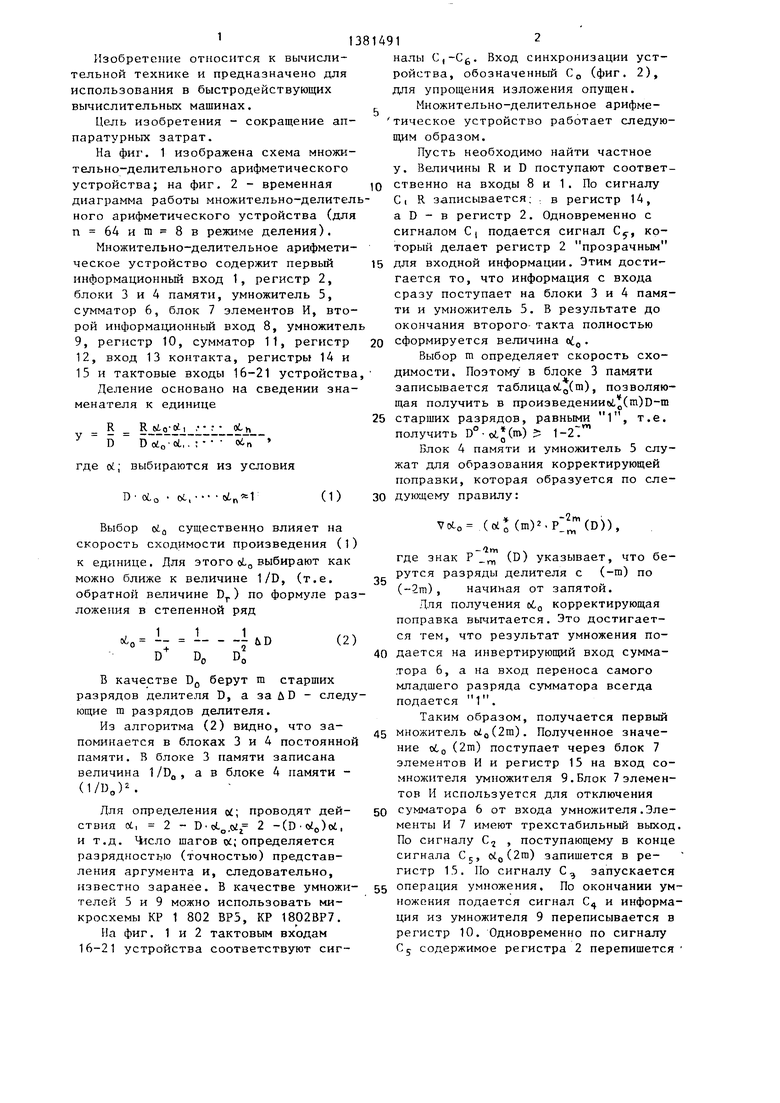

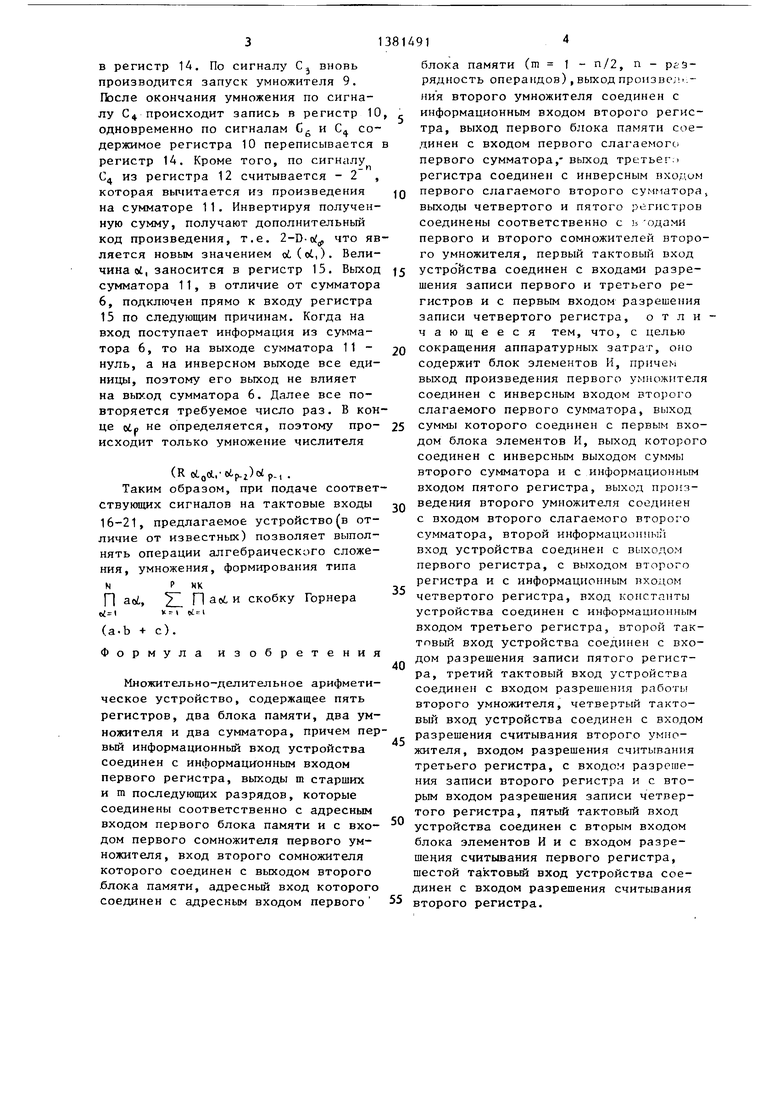

На фи1 , 1 изображена схема множи- тельно-делительного арифметического устройства; на фиг. 2 - временная диаграмма работы множительно-делител ного арифметического устройства (для п 64ит-8в режиме деления).

Множительно-делительное арифметическое устройство содержит первый информационньш вход 1, регистр 2, блоки 3 и 4 памяти, умножитель 5, сумматор 6, блок 7 элементов И, второй информационный вход 8, умножител 9, регистр 10, сумматор 11, регистр 12, вход 13 контакта, регистры 14 и 15 и тактовые входы 16-21 устройства

Деление основано на сведении знаменателя к единице

R R -o;ffj. oi.h D DoTo-oi... ; oi7

где оС; выбираются из условия

D oi,.oJ.,

(1)

0

0

налы C,-C. Вход синхронизации устройства, обозначенный С (фиг. 2), для упрощения изложения опущен.

Множительно-делительное арифметическое устройство работает следующим образом.

Пусть необходимо найти частное у. Величины R и D поступают соответственно на входы 8 и 1. По сигналу Ci R записывается; в регистр 14, а D - в регистр 2. Одновременно с сигналом С| подается сигнал С, который делает регистр 2 прозрачным

5 для входной информации. Этим достигается то, что информация с входа сразу поступает на блоки 3 и 4 памяти и умножитель 5. В результате до окончания второго такта полностью сформируется величина ci .

Выбор m определяет скорость сходимости. Поэтому в блоке 3 памяти записывается таблицаoio(т), позволяющая получить в произведении1у1(т)В-т

5 старших разрядов, равными 1, т.е. получить D°-ot(m)2;

Блок 4 памяти и умножитель 5 служат для образования корректирующей поправки, которая образуется по следующему правилу:

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое множительно-делительное устройство | 1990 |

|

SU1730623A1 |

| Множительно-делительное арифметическое устройство | 1988 |

|

SU1562906A1 |

| Преобразователь кода из системы остаточных классов в позиционный код | 1986 |

|

SU1388996A1 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Параллельно-последовательное множительное устройство | 1982 |

|

SU1156065A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для умножения | 1985 |

|

SU1305667A1 |

| Устройство для умножения 12N-разрядных двоичных чисел | 1988 |

|

SU1589271A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1983 |

|

SU1149275A1 |

Изобретение относится к области вычислительной техники и может быть использовано при конструировании процессов быстродействующих ЭВМ. Целью изобретения является сокращение аппаратурных затрат. Поставленная цель достигается тем, что множительно-де- лительное арифметическое устройство, содержащее регистры 2, 10, 12, 14, 15, блоки 3, 4 памяти, умножители 5, 9 и сумматоры 6, 11 дополнительно содержит блок 7 элементов И с соответствующими связями. 2 ил. 1

Выбор oig существенно влияет на скорость сходимости произведения (1) к единице. Для этого ot-g выбирают как можно ближе к величине 1/D, (т.е. обратной величине D) по формуле разложения в степенной ряд

1

D

I В„

В„

(2)

В качестве DQ берут m старших разрядов делителя D, а за иD - следующие m разрядов делителя.

Из алгоритма (2) видно, что запоминается в блоках 3 и 4 постоянной памяти. В блоке 3 памяти записана величина 1/D, а в блоке 4 памяти - (1/UJ4

Для определения oi проводят действия ct, 2 - D ot.,oi 2 -(D Oio)oi, и т.д. шагов oi; определяется разрядностью (точностью) представления аргумента и, следовательно, известно заранее. В качестве умножителей 5 и 9 можно использовать микросхемы КР 1 802 ВРЗ, КР 1Вр2ВР7.

Иа фиг. 1 и 2 тактовым входам 16-21 устройства соответствуют сигVoto (Ы (т)2

p:l(D)),

знак Р (D) указывает, что бе

-Im

где знак f

рутся разряды делителя с (-т) по

(-2т), начиная от запятой.

Для получения корректирующая поправка вычитается. Это достигается тем, что результат умножения подается на инвертирующий вход сумматора 6, а на вход переноса самого младшего разряда сумматора всегда подается 1.

Таким образом, получается первый множитель Ыо(2т). Полученное значение обо (2ni) поступает через блок 7 элементов И и регистр 15 на вход сомножителя умножителя 9.Блок 7 элементов И используется для отключения сумматора 6 от входа умножителя.Элементы И 7 имеют трехстабильный выход.

По сигналу С.

поступающему в конце

сигнала С, (2га) запишется в регистр 15. По сигналу С запускается операция умножения. По окончании умножения подается сигнал С и информация из умножителя 9 переписывается в регистр 10. Одновременно по сигналу С5 содержимое регистра 2 перепишется

в регистр 1А. По сигналу С вновь производится запуск умножителя 9. После окончания умножения по сигналу Сф происходит запись в регистр 10 одновременно по сигналам Cg и С содержимое регистра 10 переписывается регистр 14. Кроме того, по сигналу С из регистра 12 считывается - 2 , которая вычитается из произведения на сумматоре 11. Инвертируя полученную сумму, получают дополнительный код произведения, т.е. 2-D-o; что является новым значением oiCoi,). Величина oi, заносится в регистр 15, Выход сумматора 11, в отличие от сумматора 6, подключен прямо к входу регистра 15 по следующим причинам. Когда на вход поступает информация из сумматора 6, то на выходе сумматора 11 - нуль, а на инверсном выходе все единицы, позтому его выход не влияет на выход сумматора 6, Далее все повторяется требуемое число раз, В конце обр не определяется, поэтому про- исходит только умножение числителя

(R oioOL. oi.p-i)oip., . Таким образом, при подаче соответ

ствующих сигналов на тактовые входы 16-21, предлагаемое устройство(в отличие от известных) позволяет выполнять операции алгебраического сложения, умножения, формирования типа

N С NK

П aoi, П и скобку Горнера

изобретения

Множительно-делительное арифметическое устройство, содержащее пять регистров, два блока памяти, два умножителя и два сумматора, причем первый информационный вход устройства соединен с информационным входом первого регистра, выходы m старших и m последующих разрядов, которые соединены соответственно с адресным входом первого блока памяти и с входом первого сомножителя первого умножителя, вход второго сомножителя которого соединен с выходом второго блока памяти, адресный вход которого соединен с адресным входом первого

10

25

15

20

3814914

блока памяти (т 1 - п/2, п - рез- рядность операндов), выход произве; :- ния второго умножителя соединен с информационным входом второго регистра, выход первого блока памяти соединен с входом первого слагаемогс) первого сумматора,- выход третьег;) регистра соединен с инверсным входом первого слагаемого второго сумматора выходы четвертого и пятого регистров соединены соответственно с ь одами первого и второго сомножителей второго умножителя, первый тактовый вход устройства соединен с входами разрешения записи первого и третьего регистров и с первым входом разрешения записи четвертого регистра, отличающееся тем, что, с целью сокращения аппаратурных затрат, оно содержит блок элементов И, причем выход произведения первого умножителя соединен с инверсным входом второго слагаемого первого сумматора, выход суммы которого соединен с первым входом блока элементов И, выход которого соединен с инверсньм выходом суммы второго сумматора и с информационным входом пятого регистра, выход произведения второго умножителя соединен с входом второго слагаемого второго сумматора, второй информационный вход устройства соединен с выходом первого регистра, с выходом второго регистра и с информационным пходом четвертого регистра, вход константы устройства соединен с информационным входом третьего регистра, второй тактовый вход устройства соединен с входом разрешения записи пятого регистра, третий тактовый вход устройства соединен с входом разрешения работы второго умножителя, четвертый тактовый вход устройства соединен с входом разрешения считывания второго умножителя, входом разрешения считывания третьего регистра, с входом разрешения записи второго регистра и с вторым входом разрешения записи четвертого регистра, пятый тактовый вход устройства соединен с вторым входом блока элементов И и с входом разрешения считывания первого регистра, шестой тактовый вход устройства соединен с входом разрешения считывания второго регистра.

30

35

40

45

50

55

Шаг

20 51

УЛШ

шаг г

а

а

Фиг. 2

| Устройство для деления | 1975 |

|

SU602944A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления 48-разрядных чисел | 1984 |

|

SU1239712A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-15—Публикация

1986-03-11—Подача